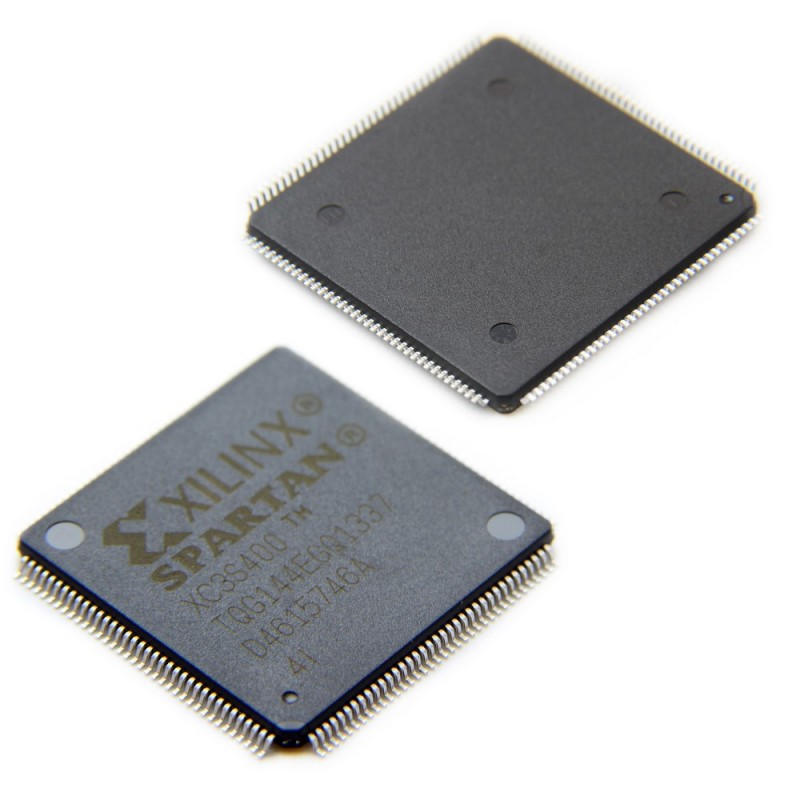

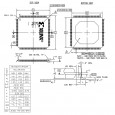

XC3S400-4TQG144I

کد کالا: 43716

نو (جدید)

دستهبندی: انواع FPGA

FPGA-G:400000 I/O:97 CEL:8064 Fpga Family; System Gates:400000 ; I/O:97 ; Macrocells:8064 ; 1.2V

لیست دیگر فروشندگان این کالا

-

XC3S400-4TQG144I

ارسال آی سی کالاIn stock quantity: 20 Item minimum quantity: 1 Item256,128,400 ریالIn stock quantity: 20 Item minimum quantity: 1 Item -

XC3S400-4TQG144I

فروشنده: رادین الکترونیکارسال از: 1 روزکاری دیگرIn stock quantity: 10 Item minimum quantity: 1 Item51,643,900 ریالIn stock quantity: 10 Item minimum quantity: 1 Item -

XC3S400-4TQG144I

فروشنده: مهرگان سیستم آذرخشارسال از: 2 روزکاری دیگرIn stock quantity: 5 Item minimum quantity: 1 Item46,750,000 ریالIn stock quantity: 5 Item minimum quantity: 1 Item

دانلود

ویژگی های: XC3S400-4TQG144I

مشخصات کلی

مشخصات تغذیه

مشخصات پردازنده

مشخصات حافظه

اطلاعات بیشتر

FPGA ها نسل جدید مدارهای مجتمع دیجیتال قابل برنامهریزی هستند. سرعت اجرای توابع منطقی در FPGA ها بسیار بالا و در حد نانو ثانیه استFPGA. ها یک معماری پیچیده مبتنی بر بلوکهای عملیاتی و یک ساختار اتصالی مبتنی بر کانالهای انعطافپذیر دارند و برای کاربردهایی با تراکم متوسط و بالا مناسبند. عملکرد آنها با برنامهنویسی کاربر نهایی تعیین میشود FPGA.ها به طراحان امکان میدهد که طرح مدار دیجیتال خود را در عرض چند دقیقه در سطح سیلیکون پیاده کنند.

اگر بخواهیمFPGA ها را به طور ساده تشریح کنیم، عبارت است از یک تراشه که از تعداد بالایی بلوک منطقی برنامهپذیر CLB برای پیاده سازی منطق ترکیبی و ترتیبی، یک سری اتصالات داخلی ثابت اما برنامه پذیر که مسیریابی سیگنال را انجام میدهند و پایههای ورودی/خروجی (IOB) تشکیل شده است که به صورت آرایه های در کنار یکدیگر قرار دارند.

کارایی و تراکم FPGAها با پیشرفت در فناوری بهبود یافته است. قطعات امروزی دارای بلوک حافظه و نیز حافظه توزیع شده، اتصالات داخلی قوی، سیگنالهای سراسری برای عملیات همگام سرعت بالا و منابع مختلف I/O برنامه پذیر منطبق با استانداردهای واسط میباشند.

تکنولوژی FPGAهای مبتنی بر SRAM، توسط برنامه پیکربندی میشود که در حافظه CMOS ایستا به نام حافظه پیکربندی ذخیره میشود. برنامه پیکربندی از یک ماشین میزبان یا PROM موجود بر روی بورد، در FPGA بار میشود. هنگام قطع تغذیه قطعه، برنامه ذخیره شده در حافظه از دست میرود و قطعه بایستی قبل از استفاده مجدد دوباره برنامه ریزی شود.

سری Spartan3 از FPGAهای شرکتXilinx از همان معماری CLB و IOB مدلهای قبل از خود اما با کارایی بالاتر استفاده میشود و برای کاربردهایی با حجم زیاد که به حافظه و بلوکهای محاسباتی(ضرب کننده(توزیع شده بر روی تراشه و کارای بالا نیازمند است، مناسبند. وجود حافظه بزرگ بر روی تراشه، کارایی سیستم را با حذف یا کاهش نیاز به دستیابی به حافظههای خارج از تراشه را بهبود میبخشد. خانواده Spartan3 با فناوری CMOS 0/18 µm و 0/22µm با شش لایه فلز برای اتصالات فیزیکی ساخته میشود. Spartan3 از درختهای ساعت بافر شده در سطح تراشه برای به حداقل رساندن انحراف پالس ساعت در کل تراشه استفاده میکند Xilinx. حلقههای قفل شده تاخیر (DLL) تمام دیجیتال برای همگام سازی/مدیریت پالس ساعت در مدارهای سرعت بالا تدارک دیده است. DLLها تاخیر توزیع پالس ساعت را حذف میکنند و ضرب کنندههای فرکانس، تقسیم کنندههای فرکانس و آینههای ساعت را فراهم میکنند. تراشه XC3S400 دارای 400 هزار گیت سیستمی، 16 ضرب کننده سخت افزاری 18*18 بیتی و 4 واحد مدیریت ساعت دیجیتال (DCM)میباشد. همچنین از 56 کیلو بیت RAM توزیع شده در سطح تراشه، بهره مند است. این تراشه از 8 پروتکل استاندارد ورودی/ خروجی پشتیبانی میکند و در بستهبندی PQ208 ارائه شده است.

@COMMENT_TITLE@

@COMMENT_COMMENT@