# GHz PLL with I<sup>2</sup>C Bus and Four Chip Addresses

## **Preliminary Data**

## Features

- 1-chip system for MPU control (I<sup>2</sup>C bus)

- 4 programmable chip addresses

- Short pull-in time for quick channel switch-over and optimized loop stability

- Charge pump output with switch off option

- Up to 3\*) high current band switch outputs (20 mA)

- Up to 4\*) output ports (5 mA)

- \*) depending on version

```

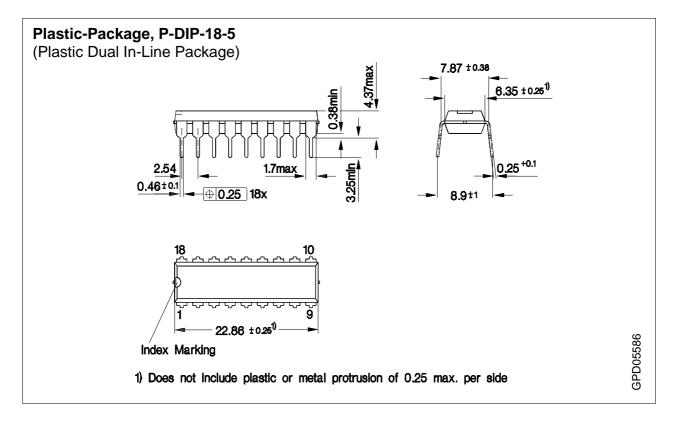

P-DIP-18-5

```

| Туре         | Ordering Code | Package                      |

|--------------|---------------|------------------------------|

| SDA 3302-5   | Q67000-H5112  | P-DIP-18-5                   |

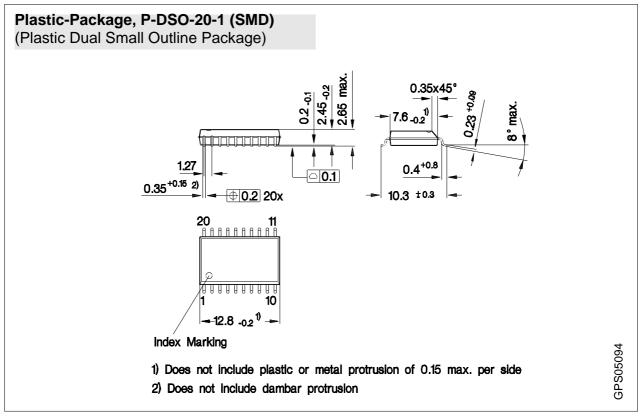

| SDA 3302-5X  | Q67000-H5111  | P-DSO-20-1 (SMD)             |

| SDA 3302-5X6 | Q67000-H5110  | P-DSO-16-1 (SMD)             |

| SDA 3302-5X  | Q67006-H5111  | P-DSO-20-1 Tape & Reel (SMD) |

| SDA 3302-5X6 | Q67006-H5110  | P-DSO-16-1 Tape & Reel (SMD) |

1

## SDA 3302 Family

**Bipolar IC**

#### **Functional Description**

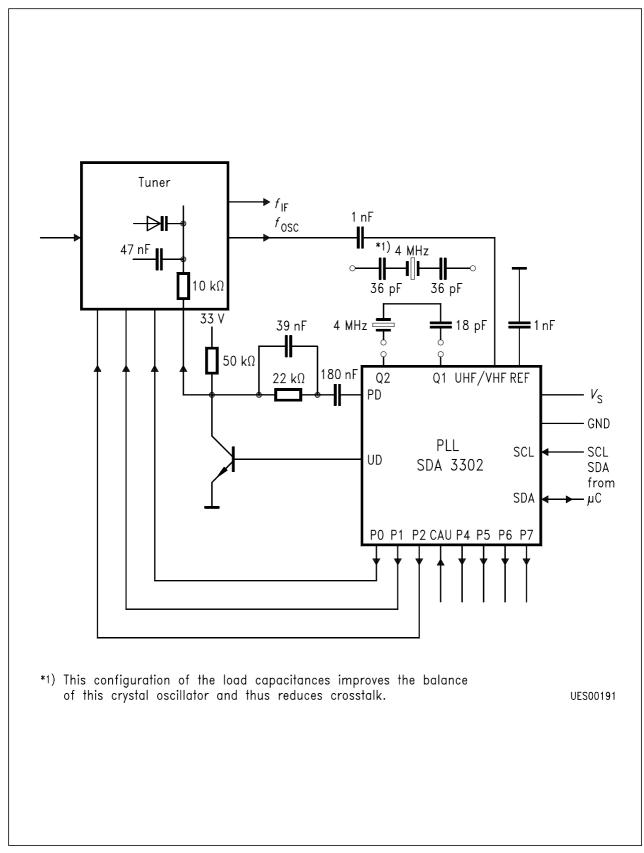

Combined with a VCO (tuner) the SDA 3302 device, with four hardware-switched chip addresses, forms a digitally programmable phase-locked loop for use in television sets with PLL frequency-synthesis tuning.

The PLL permits precise crystal-controlled setting of the frequency of the tuner oscillators between 16 and 1300 MHz in increments of 62.5 kHz. The tuning process is controlled by a microprocessor via an I<sup>2</sup>C bus. The crystal oscillator generates a sinusoidal signal suppressing the higher-order harmonics, which reduces the moiré noise considerably.

### **Circuit Description**

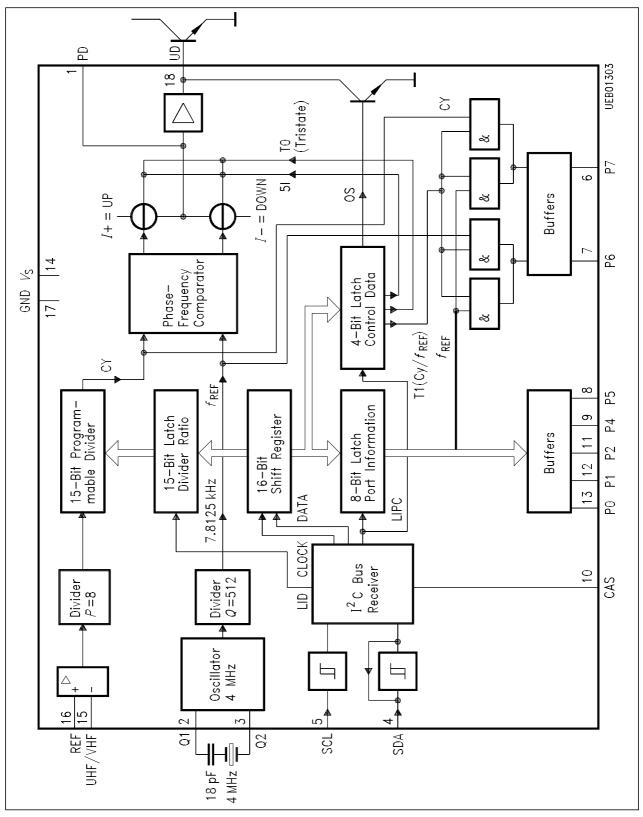

**Tuning Section** (refer to block diagram)

UHF/VHF The tuner signal is capacitively coupled at the UHF/VHF input and subsequently amplified. The reference input REF should be decoupled to ground using a capacitor of low series inductance. The signal passes through an asynchronous divider with a fixed ratio of P = 8, an adjustable divider with ratio N = 256 through 32767 and is then compared in a digital phase/frequency detector to a reference frequency  $f_{\text{REF}}$  of 7.8125 kHz. The latter is derived from a balanced, low-impedance 4 MHz crystal oscillator (pin Q1, Q2), whose output signal is divided by Q = 512.

The phase detector has two outputs UP and DOWN that drive the two current sources I+ and I- of a charge pump. If the negative edge of the divided VCO signal appears prior to the negative edge of the reference signal, the I+ current source pulses for the duration of the phase difference. In the reverse case the I- current source pulses.

PD, UD When the two signals are in phase, the charge-pump output (PD) goes highimpedance (PLL is locked). An active low-pass filter integrates the current pulses to generate the tuning voltage for the VCO (internal amplifier an external transistor at the UD output and an external RC circuitry). The charge-pump output can also be set to high-impedance state when control bit T0 = 1. Here it should be noted, however, that the tuning voltage can alter over a long period in the high-impedance state as a result of self-discharge in the peripheral circuitry. UD can be disconnected internally by the control bit OS to enable external adjustments.

By means of a control bit 5I the pump current can be switched between two values by software. This switchover permits alteration of the control response of the PLL in the locked-in state. In this way different VCO gains in the different TV bands can be compensated for example.

#### **Circuit Description** (cont'd)

- P0-P2 The software-switched outputs (P0, P1, P2) can be used for direct band selection (20-mA current output).

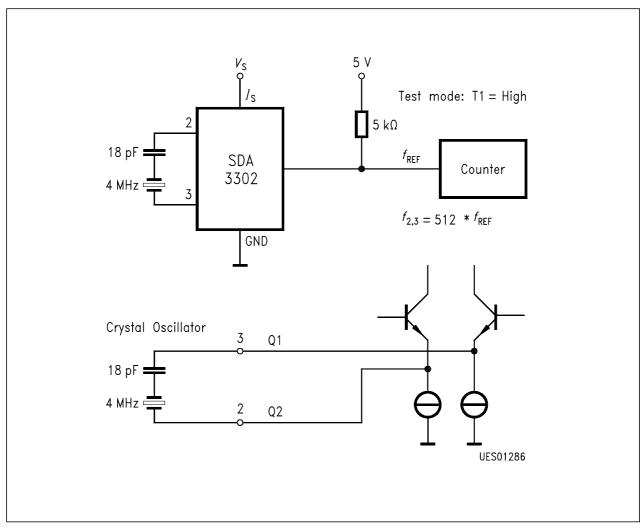

- P4-P7 P4, P5, P6 and P7 are open-collector outputs for a variety of different purposes. The test bit T1 = 1 switches the test signals  $f_{REF}$  (4 MHz/512) and Cy (divided input signal) to P6 and P7.

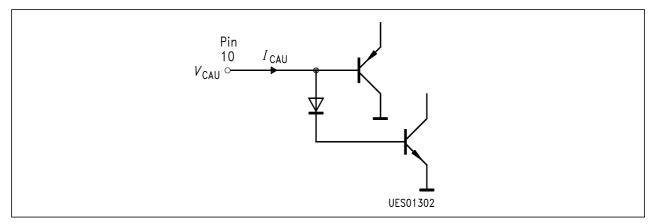

- CAS Four different chip addresses can be set by appropriate connection of pin CAS.

### I<sup>2</sup>C-Bus Interface

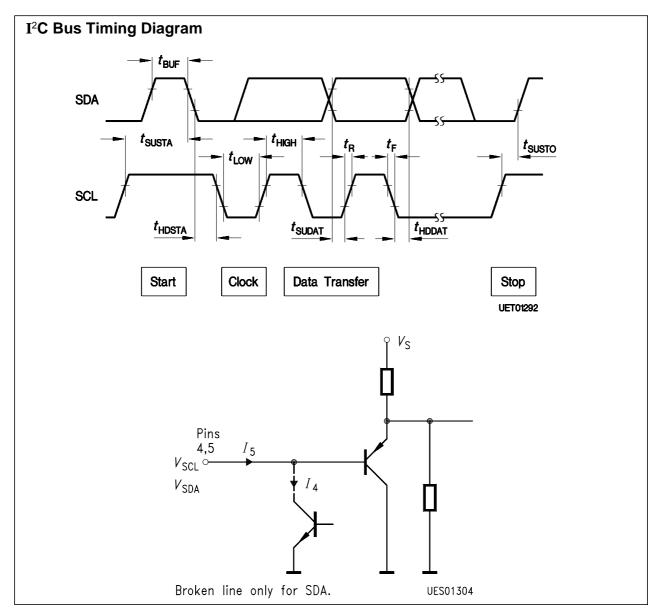

SCL, SDA Data are exchanged between the processor and the PLL on the I<sup>2</sup>C bus. The clock is produced by the processor (input SCL), while pin SDA works as an input or output depending on the direction of the data (open collector; external pullup resistor). Both inputs have hysteresis and a lowpass characteristic, which enhances the noise immunity of the I<sup>2</sup>C bus.

The data from the processor are applied to an I<sup>2</sup>C bus controller and filed in registers according to their function. When the bus is free, both lines are in the marking state (SDA, SCL are high). Each telegram begins with a start condition and ends with the stop condition. Start condition: SDA goes low while SCL remains high; stop condition: SDA goes high while SCL remains high. All further data exchanges occur while SCL is low and are accepted by the controller with the positive clock edge.

For what follows, refer to the table of logic allocations.

All telegrams are transmitted byte by byte, followed by a ninth clock pulse, during which the controller puts the SDA line on low (acknowledge condition). The first byte consists of seven address bits, with which the processor selects the PLL from a number of peripheral devices (chip select). The eighth bit is always low. In the data portion of the telegram the first bit of the first or third data byte determines whether a divider ratio or control information follows. In each case the byte following the first byte must be of the same data type (or a stop condition).

$V_{\rm S}$ , GND When the supply voltage is applied, a power-on reset circuit prevents the PLL from putting the SDA line on low, which would block the bus.

## Circuit Description (cont'd)

## **Logic Allocations**

|                      | MSB |     |     |     |     | A = Acknowledge |     |    |   |

|----------------------|-----|-----|-----|-----|-----|-----------------|-----|----|---|

| Address byte         | 1   | 1   | 0   | 0   | 0   | MA1             | MA0 | 0  | А |

| Prog. divider byte 1 | 0   | n14 | n13 | n12 | n11 | n10             | n9  | n8 | А |

| Prog. divider byte 2 | n7  | n6  | n5  | n4  | n3  | n2              | n1  | n0 | А |

| Control info. byte 1 | 1   | 51  | T1  | ТО  | 1   | 1               | 1   | OS | А |

| Control info. byte 2 | P7  | P6  | P5  | P4  | Х   | P2              | P1  | P0 | А |

## **Divider Ratio**

$$\begin{split} N = 16384 \times n14 + 8192 \times n13 + 4096 \times n12 + 2048 \times n11 + 1024 \times n10 + 512 \times n9 + 256 \times n8 + \\ + 128 \times n7 + 64 \times n6 + 32 \times n5 + 16 \times n4 + 8 \times n3 + 4 \times n2 + 2 \times n1 \\ + n0 \end{split}$$

## **Band Selection**

P2-P0 = 1 Open-collector output is active.

### Port Outputs

P7-P4 = 1 Open-collector output is active.

## Pump Current Switchover

5I = 1

High current.

## UD Disable

OS = 1  $V_D$  is disabled.

## **Test Mode**

| T1, T0 = 0,0 | Normal mode                                   |

|--------------|-----------------------------------------------|

| T1 = 1       | $P6 = f_{REF}$ ; $P7 = Cy$                    |

| T0 = 1       | Tristate charge pump PD is in high-impedance. |

## Circuit Description (cont'd)

## **Chip-Address Switching**

| MA1 | MA0 | Voltage on CAS           |  |

|-----|-----|--------------------------|--|

| 0   | 0   | (0-0.1) V <sub>S</sub>   |  |

| 0   | 1   | open                     |  |

| 1   | 0   | (0.4-0.6) V <sub>S</sub> |  |

| 1   | 1   | (0.9-1) V <sub>S</sub>   |  |

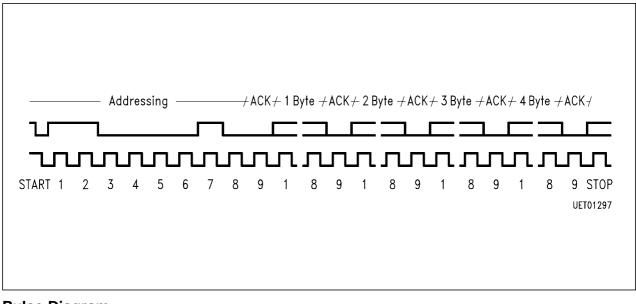

## **Pulse Diagram**

### **Telegram Examples**

Start-Addr-DR1-DR2-CW1-CW2-Stop Start-Addr-CW1-CW2-DR1-DR2-Stop Start-Addr-DR1-DR2-CW1-Stop Start-Addr-CW1-CW2-DR1-Stop Start-Addr-DR1-DR2-Stop Start-Addr-CW1-CW2-Stop Start-Addr-DR1-Stop

| Start | = start condition        |

|-------|--------------------------|

| Addr  | = address                |

| DR1   | = divider ratio 1st byte |

- DR2 = divider ratio 2nd byte

- = control word 1st byte CW1

- = control word 2nd byte

- CW2 = stop condition Stop

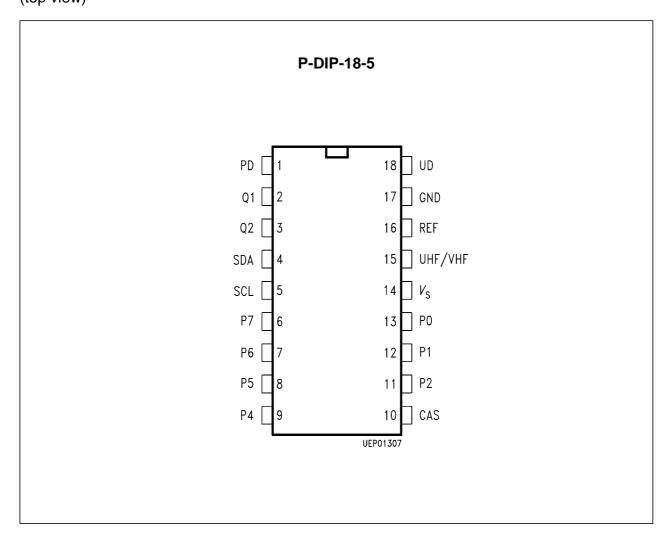

## **Pin Configuration (SDA 3302-5)** (top view)

| <b>Pin Definitions and Functions</b> | (SDA 3302-5) |

|--------------------------------------|--------------|

|--------------------------------------|--------------|

| Pin No. | Symbol  | Function                                   |

|---------|---------|--------------------------------------------|

| 1       | PD      | Active-filter input/charge-pump output     |

| 2       | Q1      | Crystal                                    |

| 3       | Q2      | Crystal                                    |

| 4       | SDA     | Data input/output for I <sup>2</sup> C bus |

| 5       | SCL     | Clock input for I <sup>2</sup> C bus       |

| 6       | P7      | Port output (open collector)               |

| 7       | P6      | Port output (open collector)               |

| 8       | P5      | Port output (open collector)               |

| 9       | P4      | Port output (open collector)               |

| 10      | CAS     | Chip-address switchover                    |

| 11      | P2      | Port output (open collector)               |

| 12      | P1      | Port output (open collector)               |

| 13      | P0      | Port output (open collector)               |

| 14      | Vs      | Supply voltage                             |

| 15      | UHF/VHF | Signal input                               |

| 16      | REF     | Amplifier reference input                  |

| 17      | GND     | Ground                                     |

| 18      | UD      | Output active filter                       |

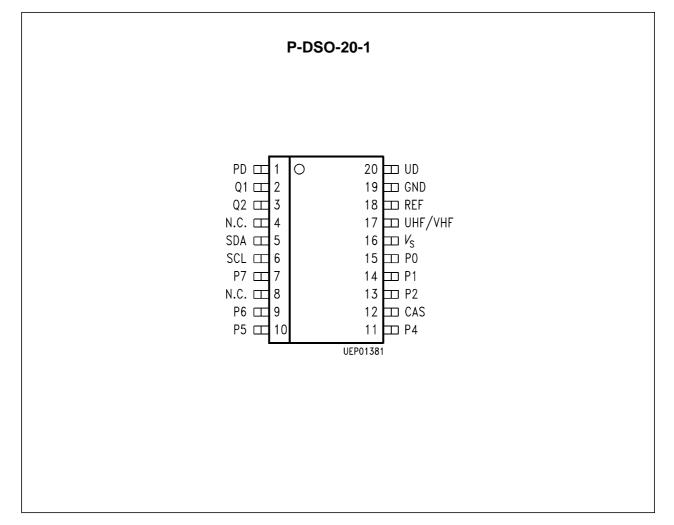

## Pin Configuration (SDA 3302-5X)

(top view)

| <b>Pin Definitions and Functions</b> | (SDA 3302-5X) |

|--------------------------------------|---------------|

|--------------------------------------|---------------|

| Pin No. | Symbol  | Function                                   |  |

|---------|---------|--------------------------------------------|--|

| 1       | PD      | Active-filter input/charge-pump output     |  |

| 2       | Q1      | Crystal                                    |  |

| 3       | Q2      | Crystal                                    |  |

| 4       | N.C.    | Not connected                              |  |

| 5       | SDA     | Data input/output for I <sup>2</sup> C bus |  |

| 6       | SCL     | Clock input for I <sup>2</sup> C bus       |  |

| 7       | P7      | Port output (open collector)               |  |

| 8       | N.C.    | Not connected                              |  |

| 9       | P6      | Port output (open collector)               |  |

| 10      | P5      | Port output (open collector)               |  |

| 11      | P4      | Port output (open collector)               |  |

| 12      | CAS     | Chip-address switchover                    |  |

| 13      | P2      | Port output (open collector)               |  |

| 14      | P1      | Port output (open collector)               |  |

| 15      | P0      | Port output (open collector)               |  |

| 16      | Vs      | Supply voltage                             |  |

| 17      | UHF/VHF | Signal input                               |  |

| 18      | REF     | Amplifier reference input                  |  |

| 19      | GND     | Ground                                     |  |

| 20      | UD      | Active-filter output                       |  |

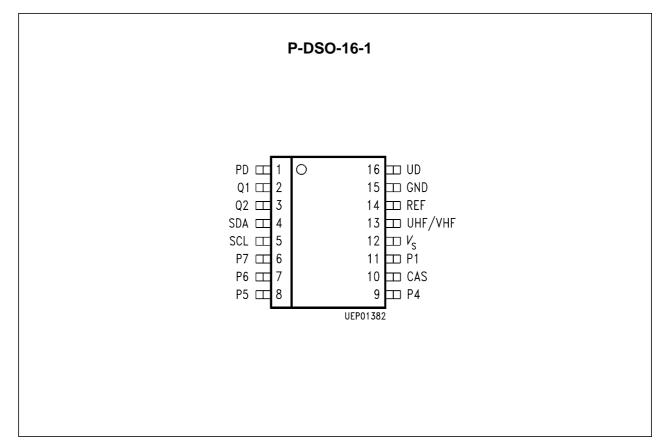

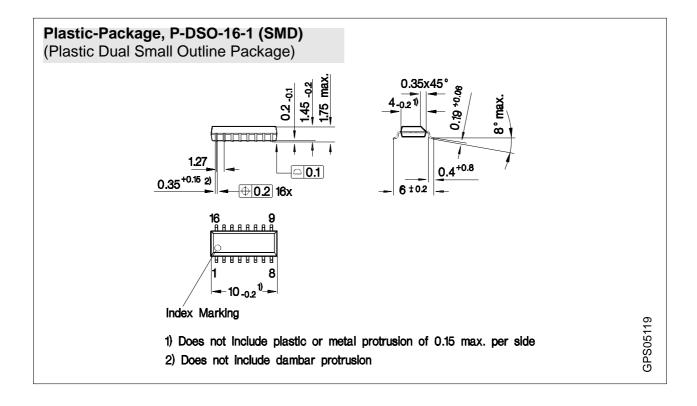

## Pin Configuration (SDA 3302-5X6)

(top view)

| <b>Pin Definitions and Functions</b> | (SDA 3302-5X6) |

|--------------------------------------|----------------|

|--------------------------------------|----------------|

| Pin No. | Symbol  | Function                                   |  |

|---------|---------|--------------------------------------------|--|

| 1       | PD      | Active-filter input/output pump output     |  |

| 2       | Q1      | Crystal                                    |  |

| 3       | Q2      | Crystal                                    |  |

| 4       | SDA     | Data input/output for I <sup>2</sup> C bus |  |

| 5       | SCL     | Clock input for I <sup>2</sup> C bus       |  |

| 6       | P7      | Port output (open collector)               |  |

| 7       | P6      | Port output (open collector)               |  |

| 8       | P5      | Port output (open collector)               |  |

| 9       | P4      | Port output (open collector)               |  |

| 10      | CAS     | Chip-address switchover                    |  |

| 11      | P1      | Port output (open collector)               |  |

| 12      | Vs      | Supply voltage                             |  |

| 13      | UHF/VHF | Signal input                               |  |

| 14      | REF     | Amplifier reference input                  |  |

| 15      | GND     | Ground                                     |  |

| 16      | UD      | Output active filter                       |  |

| SDA 3302<br>P-DIP-18-5<br>Pin No. | DIP-18-5 P-DSO-20-1 P |    | Symbol  | Function                                     |

|-----------------------------------|-----------------------|----|---------|----------------------------------------------|

| 1                                 | 1                     | 1  | PD      | Input active-filter input charge pump output |

| 2                                 | 2                     | 2  | Q1      | Crystal                                      |

| 3                                 | 3                     | 3  | Q2      | Crystal                                      |

| -                                 | 4                     | -  | N.C.    | Not connected                                |

| 4                                 | 5                     | 4  | SDA     | Data input/output for I <sup>2</sup> C bus   |

| 5                                 | 6                     | 5  | SCL     | Clock input for I <sup>2</sup> C bus         |

| 6                                 | 7                     | 6  | P7      | Port output (open collector)                 |

| -                                 | 8                     | -  | N.C.    | Not connected                                |

| 7                                 | 9                     | 7  | P6      | Port output (open collector)                 |

| 8                                 | 10                    | 8  | P5      | Port output (open collector)                 |

| 9                                 | 11                    | 9  | P4      | Port output (open collector)                 |

| 10                                | 12                    | 10 | CAS     | Chip-address switchover                      |

| 11                                | 13                    | -  | P2      | Port output (open collector)                 |

| 12                                | 14                    | 11 | P1      | Port output (open collector)                 |

| 13                                | 15                    | -  | P0      | Port output (open collector)                 |

| 14                                | 16                    | 12 | Vs      | Supply voltage                               |

| 15                                | 17                    | 13 | UHF/VHF | Signal input                                 |

| 16                                | 18                    | 14 | REF     | Amplifier reference input                    |

| 17                                | 19                    | 15 | GND     | Ground                                       |

| 18                                | 20                    | 16 | UD      | Output active filter                         |

## Block Diagram SDA 3302-5

Pin nos. refer to P-DIP-18 package only. For other packages, see reference list on page 16

## Absolute Maximum Ratings

*T*<sub>A</sub> = 25 °C

| Parameter                       | Symbol <sup>2)</sup>        | Limi      | t Values | Unit | Remarks               |

|---------------------------------|-----------------------------|-----------|----------|------|-----------------------|

|                                 |                             | min. max. |          |      |                       |

| Supply voltage                  | Vs                          | - 0.3     | 6        | V    |                       |

| Output PD                       | V <sub>1</sub>              | - 0.3     | Vs       | V    |                       |

| Crystal Q1                      | V <sub>2</sub>              | - 0.3     | Vs       | V    |                       |

| Crystal Q2                      | V <sub>3</sub>              | - 0.3     | Vs       | V    |                       |

| Bus input/output SDA            | $V_4$                       | - 0.3     | 6        | V    |                       |

| Bus input SCL                   | V <sub>5</sub>              | - 0.3     | 6        | V    |                       |

| Port output P7, P6, P5, P4      | V <sub>6, 7, 8, 9</sub>     | - 0.3     | 16       | V    |                       |

| Chip-address switchover         | V <sub>10</sub>             | - 0.3     | Vs       | V    |                       |

| Port output P2, P1, P0          | V <sub>11, 12, 13</sub>     | - 0.3     | 16       | V    | open collector        |

| Signal input UHF/VHF            | V <sub>15</sub>             | - 0.3     | 0.3      | V    | for $V_{\rm S} = 0$ V |

| Reference input REF             | V <sub>16</sub>             | - 0.3     | 0.3      | V    | for $V_{\rm S} = 0$ V |

| Output active filter UD         | V <sub>18</sub>             | - 0.3     | Vs       | V    |                       |

| Bus output SDA                  | I <sub>4L</sub>             | - 1       | 5        | mA   | open collector        |

| Port output P7, P6, P5, P4      | I <sub>6L, 7L, 8L, 9L</sub> | - 1       | 5        | mA   | open collector        |

| Port output P2, P1, P0          | I <sub>11L, 12L, 13L</sub>  | - 1       | 20       | mA   | open collector        |

| Chip temperature                | T <sub>C</sub>              |           | 125      | °C   |                       |

| Total port output current       |                             |           | 25       | mA   |                       |

| Storage temperature             | T <sub>stg</sub>            | - 40      | 125      | °C   |                       |

| Thermal resistance (system-air) | R <sub>thSA</sub>           |           | 80       | K/W  |                       |

2) Pin nos. refer to P-DIP-18 package

## Absolute Maximum Ratings

*T*<sub>A</sub> = 25 °C

| Parameter                   | Symbol <sup>2)</sup> | Limit Values |       | Unit | Remarks |

|-----------------------------|----------------------|--------------|-------|------|---------|

|                             |                      | min.         | max.  |      |         |

| Operating Range             |                      |              |       |      |         |

| Supply voltage              | Vs                   | 4.5          | 5.5   | V    |         |

| Ambient temperature         | T <sub>A</sub>       | - 20         | 80    | °C   |         |

| Input frequency             | $f_{15}$             | 16           | 1300  | MHz  |         |

| Crystal frequency           | f <sub>2,3</sub>     |              | 4     | MHz  |         |

| Programmable divider factor | N                    | 256          | 32767 |      |         |

1) Design note: no 100 % final inspection.

2) Pin nos. refer to P-DIP-18 package

### Characteristics

$V_{\rm S}$  = 5 V;  $T_{\rm A}$  = 25 °C

| Parameter                                                     | Symbol <sup>2)</sup>                   | Liı                           | nit Val | ues                     | Unit | Test Condition                                                                              | Test        |

|---------------------------------------------------------------|----------------------------------------|-------------------------------|---------|-------------------------|------|---------------------------------------------------------------------------------------------|-------------|

|                                                               |                                        | min.                          | typ.    | max.                    |      |                                                                                             | Circuit     |

| Current consumption                                           | Is                                     |                               | 35      |                         | mA   | $V_{\rm S}$ = 5 V                                                                           | 1           |

| Crystal-oscillator<br>frequency                               | <i>f</i> <sub>2, 3</sub>               | 3.99975                       | 4.000   | 4.00025                 | MHz  | series capaci-<br>tance 18 pF;<br>$f_{xtal}$ = 4 MHz                                        | 1           |

| Oscillator level <sup>1)</sup><br>(Voltage across<br>crystal) | V <sub>2,3</sub>                       |                               | 2.6     |                         | Vpp  |                                                                                             |             |

| Margin from 1st <sup>1)</sup> and 2nd harmonic                |                                        |                               | 20      |                         | dB   |                                                                                             |             |

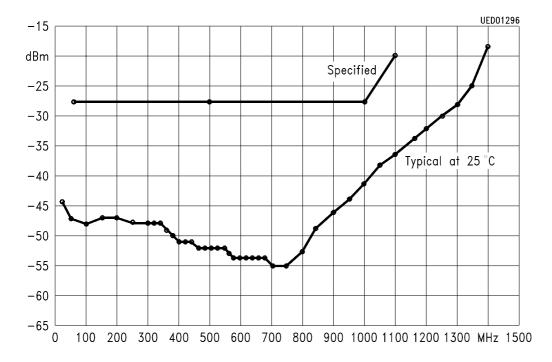

| Input Sensitivity L                                           | JHF/VHF                                |                               |         |                         |      |                                                                                             |             |

|                                                               | $a_{15} \\ a_{15} \\ a_{15} \\ a_{15}$ | - 27/10<br>- 27/10<br>- 27/10 |         | 3/315<br>3/315<br>3/315 | 3)   | $f_{15} = 70-500 \text{ MHz}$<br>$f_{15} = 1000 \text{ MHz}$<br>$f_{15} = 1100 \text{ MHz}$ | 2<br>2<br>2 |

Band-Select Outputs P0-P2 (switch with open collector)

| Reserve current  | I <sub>13H</sub> |  | 10  | μA | V <sub>13H</sub> = 13.5 V | 3 |

|------------------|------------------|--|-----|----|---------------------------|---|

| Residual voltage | V <sub>13L</sub> |  | 0.5 | V  | I <sub>13H</sub> = 20 mA  | 3 |

Port Outputs P4-P7 (switch with open collector)

| Reserve current  | I <sub>9H</sub> |  | 10  | μA | V <sub>9H</sub> = 13.5 V | 4 |

|------------------|-----------------|--|-----|----|--------------------------|---|

| Residual voltage | $V_{ m 9L}$     |  | 0.5 | V  | I <sub>9L</sub> = 1.7 mA | 4 |

Note: The sum of the currents in ports P0-P7 must not exceed 25 mA  $\,$

#### Phase-Detector Output PD

| Pump current   | I <sub>1H</sub> | ± 90 | ±230 | ± 300 | μA | 5I = HIGH;<br>$V_1 = 2 V$ |  |

|----------------|-----------------|------|------|-------|----|---------------------------|--|

| Pump current   | I <sub>1H</sub> | ±22  | ± 50 | ±75   | μA | 5I = LOW;<br>$V_1 = 2 V$  |  |

| Output voltage | V <sub>1L</sub> | 1.0  |      | 2.5   | V  | locked                    |  |

1) Design note: no 100 % final inspection.

2) Pin nos. refer to P-DIP-18 package

3) dBm/mV<sub>rms</sub> into 50  $\Omega$

## Characteristics (cont'd)

$V_{\rm S} = 5 \text{ V}; T_{\rm A} = 25 \text{ °C}$

| Parameter         | Symbol <sup>2)</sup>      | L    | .imit Va | lues       | Unit   | Test Condition                                         | Test    |

|-------------------|---------------------------|------|----------|------------|--------|--------------------------------------------------------|---------|

|                   |                           | min. | typ.     | max.       |        |                                                        | Circuit |

| Output Active Fil | ter UD (T0 =              | - 1) |          |            |        |                                                        |         |

| Output current    | - I <sub>18</sub>         | 500  |          |            | μA     | $V_{18} = 0.8 \text{ V};$<br>$I_{1H} = 90 \mu\text{A}$ | 5       |

| Output voltage    | V <sub>18</sub>           |      |          | 100        | mV     | $V_{1L} = 0 \text{ V}$                                 | 5       |

| Output voltage    | V <sub>18</sub>           |      |          | 500        | mV     | OS = 1                                                 | 5       |

| Chip-Address Sv   | vitchover                 |      |          | - 1        |        |                                                        |         |

| Input current     | I <sub>10H</sub>          |      |          | 50         | μA     | V <sub>10H</sub> = 5 V                                 | 7       |

| Input current     | - I <sub>10H</sub>        |      |          | 50         | μA     | V <sub>10H</sub> = 0 V                                 | 7       |

| Bus Inputs SCL,   | SDA                       | 1    |          |            |        |                                                        |         |

| Input voltage     | $V_{\rm 5H} \ V_{\rm 5L}$ | 3    |          | 5.5<br>5.5 | V<br>V |                                                        | 6<br>6  |

| Input current     | I <sub>5H</sub>           |      |          | 10         | μA     | $V_{\rm 5H} = V_{\rm S}$                               | 6       |

| Input current     | - I <sub>5L</sub>         |      |          | 20         | μA     | $V_{5L} = 0 \text{ V}$                                 | 6       |

| Output SDA (ope   | n collector)              | 1    |          |            |        |                                                        | _       |

| Reverse current   | I <sub>4H</sub>           |      |          | 10         | μA     | $V_{\rm 4H} = 5.5 \ { m V}$                            | 6       |

| Output voltage    | V <sub>4L</sub>           |      |          | 0.4        | V      | $I_{4L} = 3 \text{ mA}$                                | 6       |

| Edges SCL, SDA    |                           | 1    |          |            |        |                                                        |         |

| Rise time         | t <sub>R</sub>            |      |          | 1          | μs     |                                                        | 6       |

| Fall time         | t <sub>F</sub>            |      |          | 0.3        | μs     |                                                        | 6       |

| Shift Clock SCL   | 1                         |      |          |            |        | 1                                                      | -1      |

| Frequency         | $f_5$                     | 0    |          | 100        | kHz    |                                                        | 6       |

|                   |                           |      | -        | +          |        | 1                                                      | 1       |

| Frequency     | $f_5$           | 0   | 100 | kHz | 6 |

|---------------|-----------------|-----|-----|-----|---|

| H-pulse width | t <sub>5H</sub> | 4   |     | μs  | 6 |

| L-pulse width | t <sub>5L</sub> | 4.7 |     | μs  | 6 |

2) Pin nos. refer to P-DIP-18 package

## Characteristics (cont'd)

$V_{\rm S} = 5 \text{ V}; T_{\rm A} = 25 ^{\circ} \text{C}$

| Parameter                                  | Symbol <sup>2)</sup> | L    | _imit Va | lues | Unit | <b>Test Condition</b> | Test    |

|--------------------------------------------|----------------------|------|----------|------|------|-----------------------|---------|

|                                            |                      | min. | typ.     | max. |      |                       | Circuit |

| Start                                      |                      |      |          |      |      |                       |         |

| Setup time                                 | t <sub>SUSta</sub>   | 4.7  |          |      | μs   |                       | 6       |

| Hold time                                  | t <sub>HDSta</sub>   | 4    |          |      | μs   |                       | 6       |

| Stop                                       |                      | •    |          |      |      |                       |         |

| Setup time                                 | t <sub>SUsto</sub>   | 4.7  |          |      | μs   |                       | 6       |

| Bus free                                   | t <sub>BUF</sub>     | 4.7  |          |      | μs   |                       | 6       |

| Data Exchange                              |                      |      |          |      | ·    |                       |         |

| Setup time                                 | t <sub>SUDat</sub>   | 0.25 |          |      | μs   |                       | 6       |

| Hold time                                  | t <sub>HDDat</sub>   | 0    |          |      | μs   |                       | 6       |

| Input hysteresis <sup>1)</sup><br>SCL, SDA |                      |      | 300      |      | mV   |                       |         |

| Lowpass cutoff <sup>1)</sup><br>frequency  |                      |      | 500      |      | kHz  |                       |         |

1) Design note: no 100 % final inspection.

2) Pin nos. refer to P-DIP-18 package

SCL, SDA

**Test Circuit 1**

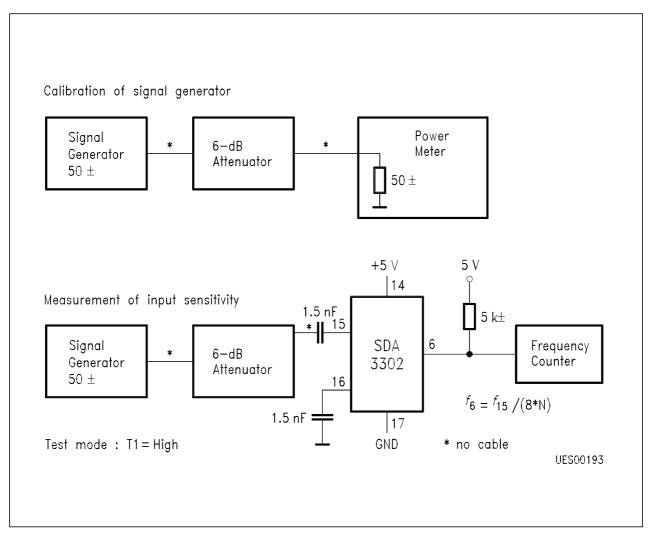

### **Test Circuit 2**

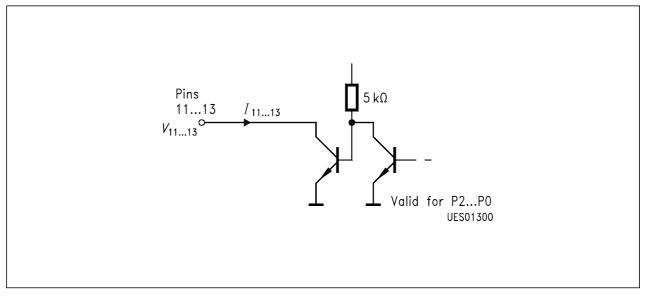

### Test Circuit 3

Semiconductor Group

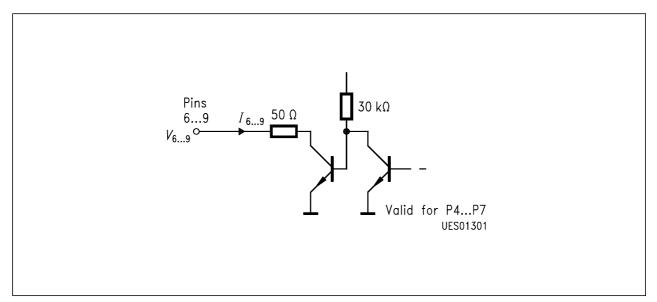

### **Test Circuit 4**

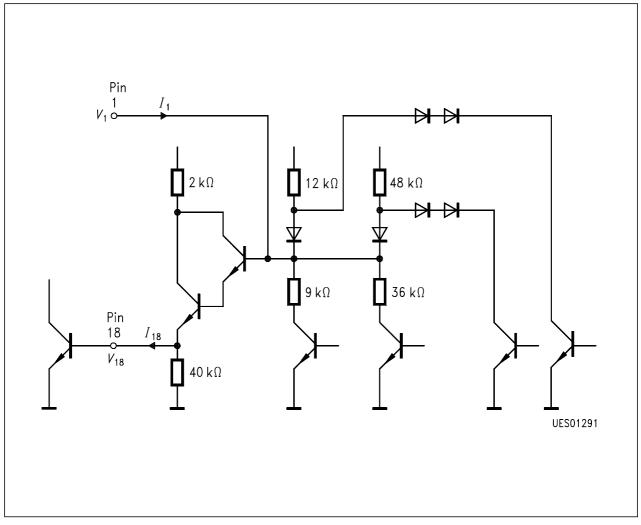

## Test Circuit 5

Semiconductor Group

#### **Test Circuit 6**

### Test Circuit 7

Semiconductor Group

### **Application Circuit**

## **Application Circuit**

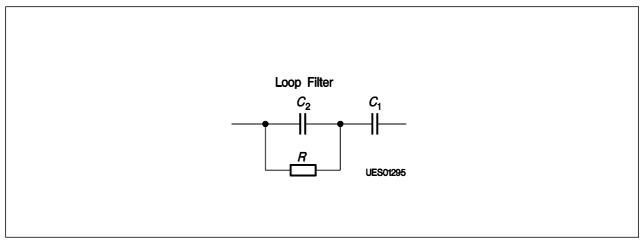

## Calculation of Loop Filter

Loop bandwidth  $\omega_{\rm R} = \sqrt{(I_{\rm p} \times K_{\rm VCO}) / (C_1 \times P \times N)}$

Attenuation:  $\xi = 0.5 \times \omega_R \times R \times C_1$

- P = prescaler

- *N* = programmable divider

- $I_{\rm p}$  = pump current

- $K_{\rm VCO}$  = tuner slope

- *R*,  $C_1$  = loop filter

Example for channel 47:

P = 8, N = 11520,  $I_p$  = 100 μA;  $K_{VCO}$  = 18.7 MHz/V, R = 22 kΩ,  $C_1$  = 180 nF,  $\omega_R$  = 336 Hz,  $f_r$  = 54 Hz,  $\xi$  = 0.67

Standard dimensioning:  $C_2 = C_{1/5}$

**Note:** The high-impedance port outputs and CAS can be blocked against external noise with a capacitor of 1 nF.

## **Input Sensitivity**

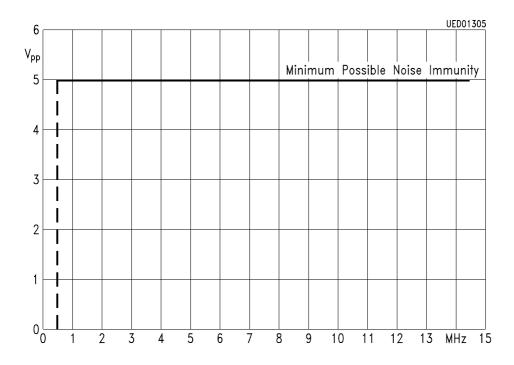

## I<sup>2</sup>C Bus Noise Immunity

The sinusoidal noise pulses are applied via a coupling capacitance of 33 pF to SCL and SDA inputs.

### **Package Outlines**

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information"

SMD = Surface Mounted Device

Dimensions in mm

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.