## M5L8243P

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 11663 INPUT/OUTPUT EXPANDER

#### **DESCRIPTION**

The M5L8243P is an input/output expander fabricated using N-channel silicon-gate EDMOS technology. This device is designed specifically to provide a low-cost means of I/O expansion for the Series MELPS 8-48 single-chip microcomputers and Series MELPS 8-41 slave microcomputers.

#### **FEATURES**

- 16 Input/output pins (I<sub>OL</sub> = 5.0mA(max.))

- Simple interface to Series MELPS 8-48, Series MELPS

- Single 5V power supply

- Low power dissipation ...... 50mW(typ.)

- Interchangeable with i8243 in pin configuration and electrical characteristics

#### **APPLICATION**

1/O expansion for the Series MELPS 8-48 single-chip microcomputers and Series MELPS 8-41 slave microcomputers.

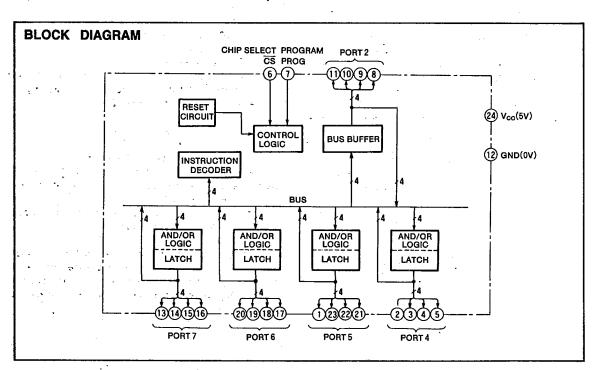

The M5L8243P is designed to provide a low-cost means of I/O expansion for the Series MELPS 8-41 and the Series MELPS 8-48. The M5L8243P consists of four 4-bit bidirectional static I/O ports and one 4-bit port which serves as an interface to the Series MELPS 8-41 and Series MELPS 8-48. Thus multiple M5L8243Ps can be added to a single master. Using the original instruction set of the master, the M5L8243P serves as the in resident I/O facility. Its

I/O ports are accessed by instructions MOVD, ANLD and ORLD. -

### M5L8243P 6249828 MITSUBISHI(MICMPTR/MIPRC)

DE

91D 11664

D

#### INPUT/OUTPUT EXPANDER

T-52-33-03

#### PIN DESCRIPTION

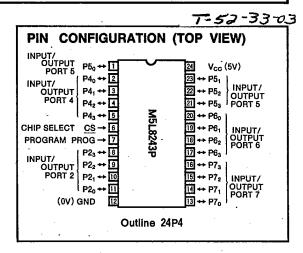

| Symbol                                                                       | Name                                                                            | Input or output | Function                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                                                                           | Chip select                                                                     | ln .            | Chip select input. A high on $\overline{CS}$ causes PROG input to be regarded high inside the M5L8243P, then this inhibits any change of output or internal status.                                                                                                                                                              |

| PROG                                                                         | Program                                                                         | . In<br>-       | A high-to-low transition on PROG signifies that address (PORT 4-7) and control are available on PORT 2, and a low-to-high transition signifies that the designated data is available on the disignated port through PORT 2. The designation is shown in Table 1.                                                                 |

| P2 <sub>0</sub> ~P2 <sub>3</sub>                                             | Input/output port 2                                                             | In/out          | The 4-bit bidirectional port contains the address and control bits shown in Table 1 on a high-to-low transition of PROG. During a low-to-high transition it contains the input (output) data on this port.                                                                                                                       |

| $P4_0 \sim P4_3$<br>$P5_0 \sim P5_3$<br>$P6_0 \sim P6_3$<br>$P7_0 \sim P7_3$ | Input/output port 4 Input/output port 5 Input/output port 6 Input/output port 7 | In/out          | The 4-bit bidirectional I/O port. May be programmed to be input, low-impedance latched output or a three-state. This port is automatically set output mode when it is written. ANLed or ORLed then continues its mode until next read operation. After reset on a read operation, this port is in high-impedance and input mode. |

#### **OPERATION**

The M5L8243P is an input/output expander designed specifically for the Series MELPS 8-41 and Series MELPS 8-48. The Series MELPS 8-41 and Series MELPS 8-48 already have instructions and PROG pin to communicate with the M5L8243P.

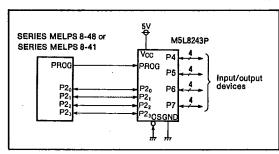

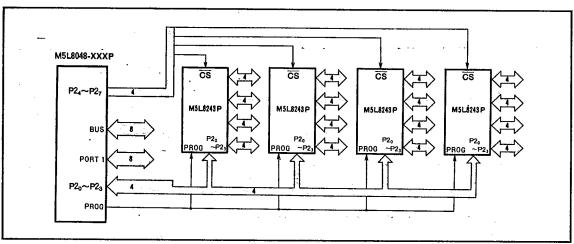

An example of the M5L8243P and the Series MELPS 8-41 or Series MELPS 8-48 is shown in Fig. 1. The following description of the M5L8243P basic operation is made according to Fig. 1.

Upon initial application of power supply to the device, and then about 500 µs after, resident bias circuits become stable and each device is ready to operate. And each port of the M5L8243P is set input mode (high-impedance) by means of a resident power-on initialization circuit.

When the microcomputer begins to execute a transfer instruction

> MOVD A, PI i = 4, 5, 6, 7

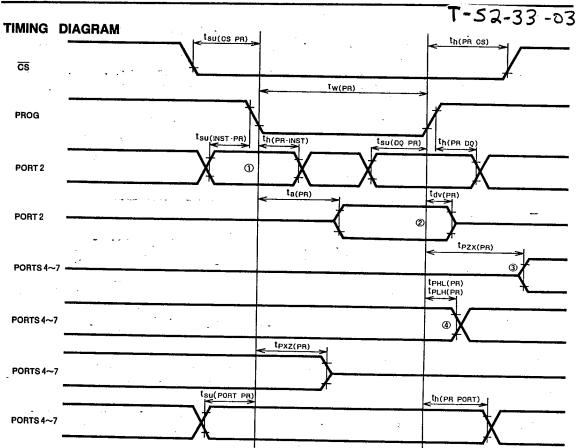

which means the value on the port Pi is transferred to the accumulator, then the signals are sent out on the pins PROG and P20~P23 as shown in Timing Diagram.

On the high-to-low transition of the pin PROG, the M5L8243P latches the instructions (ex. 0000) into itself from pins  $P2_0 \sim P2_3$  and transfers them to the instruction register (① in Timing Diagram). During the low-level of PROG, the M5L8243P continuously outputs the contents of the specified input (output) port (in this case port P4) to pins P20~  $P2_3$  ( $\bigcirc$  in Timing Diagram). The microcomputer, at an appropriate time, latches the level of pins P20~P23 and resumes high-level of PROG.

The next example is the case in which the microcomputer executes

MOVD i = 4, 5, 6, 7

the transfer (output) instruction.

In this case, as in the previous case, on the high-to-low transition of the pin PROG, the M5L8243P latches the instructions (ex. 0110) into itself from pins P20~P23 and transfers them to the instruction register (1) in Timing Diagram). After this, the microcomputer sends out high to the pin PROG, transferring the data to pin P20~P23 which is an output data to input/output port. Then the, M5L8243P transfers the data of pins P20~P23 to the port latch of the designated input/output port (in this case P<sub>6</sub>). In a few seconds after a low-to-high transition on the PROG, the designated port (P6) becomes in an output mode and the data of the port latch are transferred to the port pins (3) in Timing Diagram).

When instructions

**ANLD** Pi, A

**ORLD**

Pi,A i = 4, 5, 6, 7

are executed, the microcomputer generally operates as same function as MOVD Pi, A.

It only differs in that the data of port latch after 4 in the Timing Diagram is ANDed or ORed with the data of port latch before @ and the data of pins P20~P23.

When instructions

MOVD

**ANLD** Pi, A

ORLD

Pi, A i = 4, 5, 6, 7

are executed toward the port in an output mode, the outputs are generated on the port as soon as low-to-high transition on the PROG occurs.

When the mode of the output port is going to be changed during the execution and the instruction

> MOVD A, Pi i = 4, 5, 6, 7

is executed, it is preferable to execute one dummy instruction. Because it takes a little time to turn the designated port into a high-impedance state after high-to-low transition on the PROG, the result may be that the first instruction is not read correctly.

#### M5L8243P

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 11665

D

#### INPUT/OUTPUT EXPANDER

#### ABSOLUTE MAXIMUM RATINGS

$S_{ij} = \{ (i,j) \in \mathbb{R}^{n} \mid \forall j \in \mathcal{J}_{ij} \mid j \in \mathcal{J}_{ij} \}$

T-52-33-03

| Symbol | Parameter                            | Conditions                      | Limits         | Unit |

|--------|--------------------------------------|---------------------------------|----------------|------|

| Vcc    | Supply voltage                       |                                 | −0.5~7         | V    |

| Vı     | Input voltage                        | With respect to V <sub>SS</sub> | −0.5~7         | ٧    |

| Vo     | Output voltage                       |                                 | −0.5~7 ·       | V    |

| Pd     | Maximum power dissipation            | Ta = 25°C                       | 1000           | mW   |

| Topr   | Operating free-air temperature range |                                 | -20~75         | ℃    |

| Tsta   | Storage temperature range            |                                 | <b>−65~150</b> | °C   |

#### **RECOMMENDED OPERATING CONDITIONS** ( $\tau_a = -20 \sim 75 \, \text{C}$ , $v_{cc} = 5 \text{V} \pm 10 \%$ , unless otherwise noted)

| Symbol          | B                        |      | 11-14 |                      |      |

|-----------------|--------------------------|------|-------|----------------------|------|

| Symbol          | Parameter                |      | Nom   | Max                  | Unit |

| Voc             | Supply voltage           | 4.5  | 5     | 5.5                  | v    |

| Vss             | Supply voltage           |      | 0     |                      | V    |

| V <sub>IH</sub> | High-level input voltage | 2    |       | V <sub>cc</sub> +0.5 | V    |

| V <sub>IL</sub> | Low-level input voltage  | -0.5 |       | 0.8                  | ٧    |

#### **ELECTRICAL** CHARACTERISTICS ( $T_{a} = -20 \sim 75$ °C, $V_{cc} = 5 \text{ V} \pm 10\%$ , unless otherwise noted)

| Symbol           | Parameter                               | T1                                                       |      | Limits |      |      |

|------------------|-----------------------------------------|----------------------------------------------------------|------|--------|------|------|

|                  |                                         | Test conditions                                          | Min  | Тур    | Max  | Unit |

| V <sub>OL1</sub> | Low-level output voltage, ports 4~7     | I <sub>OL</sub> = 5mA                                    |      |        | 0.45 | V    |

| V <sub>OL2</sub> | Low-level output voltage, port 7        | I <sub>OL</sub> = 20 mA                                  |      |        | 1    | V    |

| Vols             | Low-level output voltage, port 2        | I <sub>OL</sub> = 0.6mA                                  |      |        | 0.45 | V    |

| V <sub>OH1</sub> | High-level output voltage, ports 4~7    | $I_{OH} = -240 \mu A$                                    | 2.4  |        |      | ٧    |

| V <sub>OH2</sub> | High-level output voltage, port 2       | $I_{OH} = -100 \mu A$                                    | 2. 4 |        |      | ٧٠   |

| 111              | Input leakage current, ports 4~7        | 0V ≤ V <sub>in</sub> ≤ V <sub>cc</sub>                   | -10  |        | 20   | μΑ   |

| 112              | Input leakage current, port 2, CS, PROG | 0V ≤ V <sub>in</sub> ≤ V <sub>cc</sub>                   | -10  |        | 10   | μA   |

| loo              | Supply current from V <sub>CC</sub>     |                                                          |      | 10     | 20   | mA   |

| loL              | Sum of all IoL from 16 outputs          | I <sub>OL</sub> = 5mA (V <sub>OL</sub> = 0.45V) Each pin |      |        | 80   | mΆ   |

Table 1 Instruction and address codes

| Instruction code | P2 <sub>3</sub> | P2 <sub>2</sub> | Address code | P2 <sub>1</sub> | P2 <sub>0</sub> |

|------------------|-----------------|-----------------|--------------|-----------------|-----------------|

| Read             | 0               | 0               | port 4       | 0               | 0               |

| Write            | 0               | 1               | port 5       | 0               | 1               |

| ORLD             | 1               | 0               | port 6       | 1               | 0               |

| ANLD             | 1               | 1               | port 7       | 1               | 1               |

Fig.1 Basic connection

#### M5L8243P

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 11666

#### INPUT/OUTPUT EXPANDER

#### **TIMING REQUIREMENTS** ( $\tau_a = -20 \sim 75 \, \text{C}$ , $V_{\text{CC}} = 5 \text{V} \pm 10 \%$ , unless otherwise noted)

| Symbol                 | Parameter                               | Alternative symbol | Test conditions | Limits |     |     |      |

|------------------------|-----------------------------------------|--------------------|-----------------|--------|-----|-----|------|

|                        |                                         |                    |                 | Min    | Тур | Max | Unit |

| tsu(INST-PR)           | Instruction code setup time before PROG | t <sub>A</sub>     | 80pF Load       | 100    |     |     | ns   |

| th(PR-INST)            | Instruction code hold time after PROG   | t <sub>B</sub>     | 20pF Load       | 60     |     |     | ns - |

| t <sub>SU(DQ-PR)</sub> | Data setup time before PROG             | to                 | 80pF Load       | 200    |     |     | ns   |

| th(PR-DQ)              | Data hold time after PROG               | t <sub>D</sub>     | 20pF Load       | 20     |     |     | ns   |

| tw(pa)                 | PROG pulse width                        | t <sub>K</sub>     |                 | 700    |     |     | ns   |

| tsu(cs-PR)             | Chip-select setup time before PROG      | tos                |                 | 50     |     |     | ns   |

| th(PR-CS)              | Chip-select hold time after PROG        | tos                |                 | 50     |     |     | ns   |

| tsu(PORT-PR)           | Port setup time before PROG             | t <sub>IP</sub>    | N. F            | 100    |     |     | ns   |

| th(PR-PORT)            | Port hold time after PROG               | t <sub>IP</sub>    |                 | 100    |     |     | ns   |

#### **SWITCHING CHARACTERISTICS** ( $\tau_a = -20 \sim 75$ °C, $V_{cc} = 5 V \pm 10\%$ , unless otherwise noted)

| Symbol               | Parameter                       | Alternative      | Test conditions | Limits   |     |     | 11-14 |

|----------------------|---------------------------------|------------------|-----------------|----------|-----|-----|-------|

|                      |                                 | symbol           |                 | Min      | Тур | Max | Unit  |

| ta(PR)               | Data access time after PROG     | t <sub>ACC</sub> | 80pF Load       | 0        |     | 650 | ns    |

| tdv(PR)              | Data valid time after PROG      | t <sub>H</sub>   | 20pF Load       | 0        |     | 150 | ns    |

| t <sub>PHL(PR)</sub> | Output valid time after PROG    | too              | 100pF Load      |          |     | 700 | ns    |

| t <sub>PLH(PR)</sub> | Output valid titlle alter Priod | t <sub>PO</sub>  |                 | <u> </u> |     | /00 |       |

| t <sub>PZX(PR)</sub> | Input/output switching time     |                  |                 |          |     | 800 | ns    |

| texz(en)             | inhan onthat satirountal mus    | 1                | l               |          |     | 000 | 110   |

# ъ **П**

#### MITSUBISHI MICROCOMPUTERS

M5L8243P

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 11667 D

#### INPUT/OUTPUT EXPANDER.

#### Note 1: AC test conditions

| Input pulse level                       |

|-----------------------------------------|

| Input pulse rise time tr (10%~90%)20ns  |

| Input pulse fall time tf (10%~90%) 20ne |

| Referer | nce voltage for switching characteristic measurement. |

|---------|-------------------------------------------------------|

| Output  | V <sub>OH</sub> 2V                                    |

|         | V <sub>OL</sub>                                       |

#### **Current Sinking Capability**

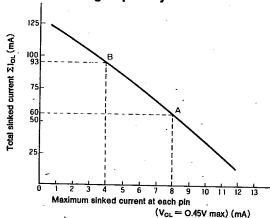

Each of the 16 I/O lines of the M5L8243P is capable of sinking 5mA simultaneously ( $V_{OL}=0.45V$  max). However, the drive capacity of each line depends upon whether all lines are sinking current simultaneously and on the degree of loading. This is illustrated in the curve shown. Example

Assuming that the remaining pins are not loaded, how many pins would be able to accommodate 20LSTTL loads (0.4mA)?

$I_{OL} = 0.4 \text{mA} \times 20 = 8 \text{mA} \text{ (sink current for each pin)}$

$\Sigma I_{OL} = 60 \text{mA} \text{ from curve (POINT A)}$

(total sinking current)

Number of pins =  $60 \text{mA} \div 8 \text{mA} = 7.5 > 7$

For this case, each of the 7 lines could sink 8mA for a total of 56mA. Since 4mA reserve sinking capability exists, 9 of the I/O lines of the M5L8243P can be divided arbitrarily.

#### M5L8243P

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 11668 D

#### INPUT/OUTPUT EXPANDER

T-52-33-03

To use 20mA sinking capability at port 7, find the effects on the sinking capabilities of the other I/O lines.

Assume the M5L8243P is driving loads as shown below.

3 lines: -20mA ( $V_{OL} = 1.0$ V max, port 7 only)

4 lines: -4mA (V<sub>OL</sub> = 0.45V max) 9 lines: -1.6mA (V<sub>OL</sub> = 0.45V max)

Is this within the allowable limit?

$\Sigma I_{OL} = (20 \text{mA} \times 3) + (4 \text{mA} \times 4) + (1.6 \text{mA} \times 9) =$ 90.4mA

From the curve we see that with respect to  $I_{\rm OL}=4{\rm mA}$ ,  $I_{\rm OL}$ is 93mA (Point B) and that the above load of 90.4mA is within the limit of 93mA.

Note: The sinking current of ports  $4 \sim 7$  must not exceed 30mA regardless of the value of Vol.

Fig.2 Expansion interface example