- Multiplexed Inputs/Outputs Provide Improved Bit Density

- 3-State Outputs Drive Bus Lines Directly

- Sign Extend Function

- Direct Overriding Clear

#### description

These low-power Schottky eight-bit shift registers feature multiplexed input/output data ports to achieve full eight-bit data handling in a single 20-pin package. Serial data may be entered into the shift-right register through either the D0 or the D1 input as selected by the data select input. A serial output (QH') is also provided to facilitate expansion. Synchronous parallel loading is accomplished by taking both the register enable and the S/P inputs low. This places the three-state input/output ports in the data input mode. Data are entered on the low-to-high transition of the clock. The data extend function repeats the sign in the QA flip-flop during shifting. A direct overriding clear input clears the internal registers when taken low whether the outputs are enabled or off. The output enable does not interfere with synchronous operation of the register.

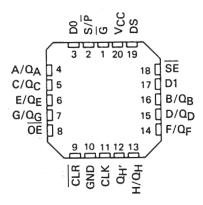

SN54LS322A . . . J OR W PACKAGE SN74LS322A . . . DW OR N PACKAGE (TOP VIEW)

# SN54LS322A . . . FK PACKAGE (TOP VIEW)

### **FUNCTION TABLE**

|             | INPUTS |                         |     |                      |                      |                        |     | 11               |                 |                    |                  |                          |

|-------------|--------|-------------------------|-----|----------------------|----------------------|------------------------|-----|------------------|-----------------|--------------------|------------------|--------------------------|

| OPERATION   | CLR    | REGISTER<br>ENABLE<br>G | S/P | SIGN<br>EXTEND<br>SE | DATA<br>SELECT<br>DS | OUTPUT<br>ENABLE<br>OE | CLK | A/Q <sub>A</sub> | B/QB            | c/Q <sub>C</sub> . | н/о <sub>Н</sub> | OUTPUT<br>Q <sub>H</sub> |

| Class       | L      | н                       | Х   | Х                    | X                    | L                      | X   | L                | L               | L                  | L                | L                        |

| Clear       | L      | ×                       | Н   | X                    | X                    | L                      | ×   | L                | L               | L                  | L                | L                        |

| Hold        | Н      | Н                       | Х   | Х                    | Х                    | L                      | X   | Q <sub>A0</sub>  | Q <sub>B0</sub> | Q <sub>C0</sub>    | QH0              | Q <sub>H0</sub>          |

| Shift Right | Н      | L                       | Н   | Н                    | L                    | L                      | 1   | D0               | Q <sub>An</sub> | Q <sub>Bn</sub>    | $Q_{Gn}$         | QGn                      |

| Silit Right | Н      | L                       | Н   | Н                    | Н                    | L                      | 1   | D1               | $Q_{An}$        | $Q_{Bn}$           | $Q_{Gn}$         | $Q_{Gn}$                 |

| Sign Extend | ∴H     | L                       | Н   | L                    | Х                    | L                      | 1   | Q <sub>An</sub>  | Q <sub>An</sub> | $Q_{Bn}$           | $Q_{Gn}$         | Q <sub>Gn</sub>          |

| Load        | Н      | L                       | L   | X                    | ×                    | X                      | †   | а                | b               | С                  | h                | h                        |

When the output enable is high, the eight input/output terminals are disabled to the high-impedance state; however, sequential operation or clearing of the register is not affected. If both the register enable input and the  $S/\overline{P}$  input are low while the clear input is low, the register is cleared while the eight input/output terminals are disabled to the high-impedance state.

H.= high level (steady state)

L = low level (steady state)

X = irrelevant (any input, including transitions)

† = transition from low to high level

QAO...QHO = the level of QA through QH, respectively, before the indicated steady-state conditions were established

$Q_{An} \dots Q_{Hn} = \text{the level of } Q_A \text{ through } Q_H, \text{ respectively, before the most recent } \uparrow \text{ transition of the clock}$

D0, D1 = the level of steady-state inputs at inputs D0 and D1 respectively

a...h = the level of steady-state inputs at inputs A through H respectively

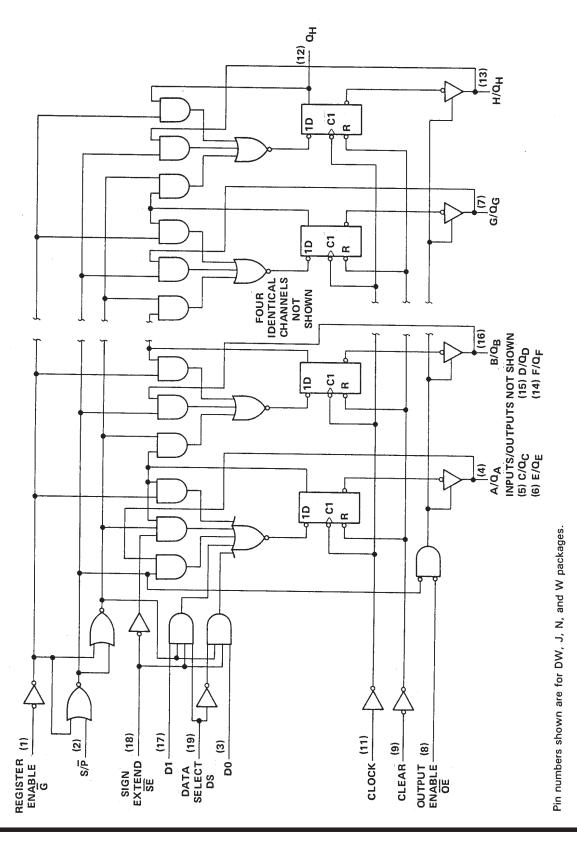

## logic diagram (positive logic)

TEXAS INSTRUMENTS

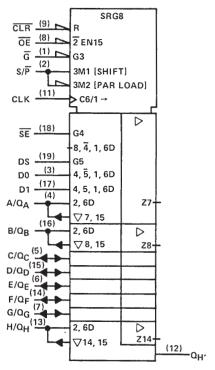

### logic symbol†

$^\dagger$ This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12. Pin numbers shown are for DW, J, N, and W packages.

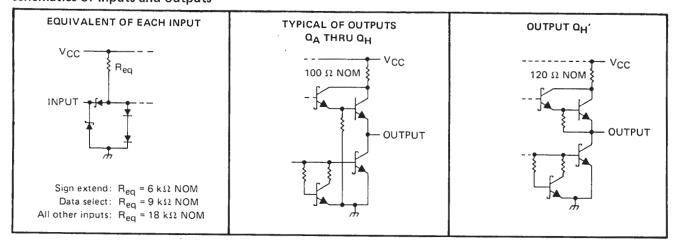

## schematics of inputs and outputs

# SN54LS322A, SN74LS322A 8-BIT SHIFT REGISTERS WITH SIGN EXTEND

SDLS159 - OCTOBER 1977 - REVISED MARCH 1988

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1) .    |            |  |  |  |  |  |  |  |  |            |      |      |      | 7 V  |

|---------------------------------------|------------|--|--|--|--|--|--|--|--|------------|------|------|------|------|

| Input voltage                         |            |  |  |  |  |  |  |  |  |            |      |      |      | 7 V  |

| Off-state output voltage              |            |  |  |  |  |  |  |  |  |            |      |      |      | 7 V  |

| Operating free-air temperature range: | SN54LS322A |  |  |  |  |  |  |  |  | <u>_</u> 5 | 5°0  | C to | 12   | 25°C |

|                                       | SN74LS322A |  |  |  |  |  |  |  |  |            | 0    | °C   | to 7 | 70°C |

| Storage temperature                   |            |  |  |  |  |  |  |  |  | _6         | \$5° | C tr | . 16 | 50°C |

NOTE 1: Voltage values are with respect to network ground terminal.

## recommended operating conditions

|                       |                                |                                    | SN   | 154LS32                               | 22A     | SN   | 74LS32                                  | 2A                                      |      |  |  |  |

|-----------------------|--------------------------------|------------------------------------|------|---------------------------------------|---------|------|-----------------------------------------|-----------------------------------------|------|--|--|--|

|                       |                                |                                    | MIN  | NOM                                   | MAX     | MIN  | NOM                                     | MAX                                     | UNIT |  |  |  |

| VCC                   | Supply voltage                 |                                    | 4.5  | 5                                     | 5.5     | 4.75 | 5                                       | 5.25                                    | V    |  |  |  |

| $V_{\text{IH}}$       | High-level input voltage       |                                    | 2    |                                       |         | 2    |                                         |                                         | V    |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage        |                                    |      |                                       | 0.7     |      |                                         | 0.5                                     | V    |  |  |  |

| Іон                   | High-level output current      | Q <sub>A</sub> thru Q <sub>H</sub> |      |                                       | - 1     |      |                                         | -2.6                                    |      |  |  |  |

| 'OH                   |                                | Q <sub>H</sub> ′                   |      | · · · · · · · · · · · · · · · · · · · | -0.4    |      |                                         | -0.4                                    | mA   |  |  |  |

| loL                   | Low-level output current       |                                    |      |                                       | 12      |      |                                         | 24                                      |      |  |  |  |

| 'UL                   |                                | QH'                                |      |                                       | 4       |      |                                         | 8                                       | mA   |  |  |  |

| f <sub>clock</sub>    | Clock frequency                |                                    | 0    | -                                     | 20      | 0    |                                         | 20                                      | MHz  |  |  |  |

| tt                    | Width of clock pulse           | Clock high                         | 30   |                                       |         | 30   |                                         |                                         |      |  |  |  |

| <sup>t</sup> w(clock) | Width of clock palse           | Clock low                          | 10   |                                       | ******* | 10   | *************************************** |                                         | ns   |  |  |  |

| tw(clear)             |                                | Clear low                          | 20   |                                       |         | 20   |                                         |                                         | ns   |  |  |  |

|                       |                                | Data select                        | 101  |                                       |         | 10↑  |                                         |                                         |      |  |  |  |

|                       |                                | High-level data <sup>†</sup>       | 201  | _                                     |         | 201  |                                         |                                         |      |  |  |  |

| t <sub>su</sub>       | Setup time                     | Low-level data <sup>†</sup>        | 201  |                                       |         | 201  |                                         | ***                                     |      |  |  |  |

| -su                   | Sotop time                     | Clear inactive-state               | 201  |                                       |         | 201  |                                         |                                         | ns   |  |  |  |

|                       |                                | Register enable G high             | 35↑  | •                                     |         | 35↑  |                                         |                                         |      |  |  |  |

|                       |                                | Register enable G low              | 501  |                                       |         | 501  |                                         |                                         |      |  |  |  |

|                       |                                | Data select                        | 10t  |                                       |         | 101  |                                         |                                         |      |  |  |  |

| th                    | Hold time                      | Data <sup>†</sup>                  | 21   |                                       |         | 21   |                                         | *************************************** |      |  |  |  |

| -11                   | Trong Gillo                    | Register enable<br>high or low     | Of   |                                       |         | Oî   | 77.888                                  |                                         | ns   |  |  |  |

| TA                    | Operating free-air temperature |                                    | - 55 |                                       | 125     | 0    | *************************************** | 70                                      | °C   |  |  |  |

$<sup>\</sup>ensuremath{^{\dagger}}\xspace$  Data includes the two serial inputs and the eight input/output data lines.

<sup>†</sup>The arrow indicates that the rising edge of the clock pulse is used for reference.

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DAG             | RAMETER                            |                        | ST CONDITION             | ct                      | SI   | 154LS32 | 22A   | SN   | 174LS32 | 22A          | UNIT |  |

|-----------------|------------------------------------|------------------------|--------------------------|-------------------------|------|---------|-------|------|---------|--------------|------|--|

| PAI             | ANIETER                            | 16                     | STCOMBITION              | 5'                      | MIN  | TYP‡    | MAX   | MIN  | TYP‡    | MAX          | ONT  |  |

| VIK             |                                    | V <sub>CC</sub> = MIN, | I <sub>I</sub> = - 18 mA |                         |      |         | - 1.5 |      |         | - 1.5        | V    |  |

| Voн             | Q <sub>A</sub> thru Q <sub>H</sub> | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,   | VIL = MAX,              | 2.4  | 3.2     |       | 2.4  | 3.1     |              | V    |  |

| VOH             | QH'                                | IOH = MAX              |                          | 1                       | 2.5  | 3.4     |       | 2.7  | 3.4     |              | · •  |  |

|                 | Q <sub>A</sub> thru Q <sub>H</sub> |                        |                          | I <sub>OL</sub> = 12 mA |      | 0.25    | 0.4   |      | 0.25    | 0.4          |      |  |

| VoL             | - CA tille CH                      | V <sub>CC</sub> = MIN, | $V_{IH} = 2 V$ ,         | I <sub>OL</sub> = 24 mA |      |         |       |      | 0.35    | 0.5          | v    |  |

| VOL             | Ou                                 | $V_{iL} = MAX$         |                          | 1 <sub>OL</sub> = 4 mA  |      | 0.25    | 0.4   |      | 0.25    | 0.4          |      |  |

|                 | Q <sub>H</sub>                     |                        |                          | I <sub>OL</sub> = 8 mA  |      |         |       |      | 0.35    | 0.5          |      |  |

| lozh            | Q <sub>A</sub> thru Q <sub>H</sub> | $V_{CC} = MAX$ ,       | V <sub>IH</sub> = 2 V,   | V <sub>O</sub> = 2.7 V  |      |         | 40    |      |         | 40           | μA   |  |

| IOZL            | Ω <sub>A</sub> thru Q <sub>H</sub> | V <sub>CC</sub> = MAX, | V <sub>IH</sub> = 2 V,   | V <sub>O</sub> = 0.4 V  |      |         | - 0.4 |      |         | 0.4          | mA   |  |

|                 | A thru H                           |                        |                          | V <sub>I</sub> = 5.5 V  |      |         | 0.1   |      |         | 0.1          |      |  |

| I <sub>I</sub>  | Data select                        | V <sub>CC</sub> = MAX  |                          | V <sub>1</sub> = 7 V    |      |         | 0.2   | -    |         | 0.2          | mA   |  |

| 11              | Sign extend                        | ACC - MVV              |                          | ∨ <sub>1</sub> = 7 ∨    |      |         | 0.3   |      |         | 0.3          | ША   |  |

|                 | Any other                          |                        |                          | V <sub>1</sub> = 7 V    |      |         | 0.1   |      |         | 0.1          |      |  |

|                 | A thru H, DS                       |                        |                          |                         |      |         | 40    |      |         | 40           |      |  |

| ЧΗ              | Sign extend                        | $V_{CC} = MAX$ ,       | V <sub>I</sub> = 2.7 V   |                         |      |         | 60    |      |         | 60           | μΑ   |  |

|                 | Any other                          |                        |                          |                         |      |         | 20    |      |         | 20           |      |  |

|                 | Data select                        |                        | ***                      |                         |      |         | - 0.8 |      |         | - 0.8        |      |  |

| l <sub>IL</sub> | Sign extend                        | $V_{CC} = MAX$ ,       | $V_I = 0.4 V$            |                         |      |         | - 1.2 |      |         | - 1.2        | mA   |  |

|                 | Any other                          |                        |                          |                         |      |         | - 0.4 |      |         | - 0.4        | 1    |  |

| los§            | Q <sub>A</sub> thru Q <sub>H</sub> | V00 - MAY              | Vo = 2.25                | V (for 54LS only)       | - 15 |         | - 65  | - 30 |         | - 130        |      |  |

|                 | QH'                                | VCC = MAX,             | v <sub>0</sub> = 2.25    | v (for 54LS only)       | - 10 |         | - 50  | - 20 |         | <b>– 100</b> | mA   |  |

| Icc             |                                    | V <sub>CC</sub> = MAX  |                          |                         |      | 35      | 60    |      | 35      | 60           | mA   |  |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ} \text{ C}$

| PARAMETER¶       | FROM<br>(INPUT) | TO<br>(OUTPUT)                     | TEST CONE                             | TEST CONDITIONS         |    |    |    | UNIT |

|------------------|-----------------|------------------------------------|---------------------------------------|-------------------------|----|----|----|------|

| fmax             |                 |                                    | See Note 2                            |                         | 20 | 35 |    | MHz  |

| tPLH             | CLK             | QH'                                | P 2 kg                                | 0 - 15 - 5              |    | 22 | 33 |      |

| tPHL             | CLK             | ФН                                 | $R_L = 2 k\Omega$ ,<br>See Note 2     | C <sub>L</sub> = 15 pF, |    | 26 | 35 | ns   |

| tPHL             | CLR             | QH'                                | See Note 2                            |                         |    | 27 | 35 | ns   |

| tPLH t           | CLK             | Q <sub>A</sub> thru Q <sub>H</sub> |                                       |                         |    | 16 | 25 |      |

| tPHL.            | CER             | QA and QH                          | D - 00F 0                             |                         |    | 22 | 33 | ns   |

| tPHL_            | CLR             | Q <sub>A</sub> thru Q <sub>H</sub> | R <sub>L</sub> = 665 Ω,<br>See Note 2 | $C_L = 45 pF$ ,         |    | 22 | 35 | ns   |

| <sup>t</sup> PZH |                 | Q <sub>A</sub> thru Q <sub>H</sub> | See Note 2                            |                         |    | 15 | 35 |      |

| tPZL             | ŌĒ              | ад ши он                           |                                       |                         |    | 15 | 35 | ns   |

| tPHZ             |                 | Q <sub>A</sub> thru Q <sub>H</sub> | $R_L = 665 \Omega$ ,                  | C <sub>L</sub> = 5 pF,  |    | 15 | 25 |      |

| tPLZ             | ŌĒ              | CA tilla CH                        | See Note 2                            |                         |    | 15 | 25 | ns   |

$<sup>\</sup>P_{\mathsf{fmax}} \equiv \mathsf{maximum} \ \mathsf{clock} \ \mathsf{frequency}$

tpZL ≡ output enable time to low level

$\begin{array}{ll} \mbox{tp}_{LH} \equiv \mbox{propagation delay time, low-to-high-level output} & \mbox{tp}_{HZ} \equiv \mbox{output disable time from high level} \\ \mbox{tp}_{HL} \equiv \mbox{propagation delay time, high-to-low-level output} & \mbox{tp}_{LZ} \equiv \mbox{output disable time from low level} \\ \end{array}$

tpZH ≡ output enable time to high level

NOTE 2: For testing f<sub>max</sub>, all outputs are loaded simultaneously, each with C<sub>L</sub> and R<sub>L</sub> as specified for the propagation times. Load circuits and voltage waveforms are shown in Section 1.

<sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ} \text{C}$ .

<sup>§</sup> Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.