# Single chip 2.4 GHz Transceiver

# nRF24L01

#### **FEATURES**

- True single chip GFSK transceiver

- Complete OSI Link Layer in hardware

- Enhanced ShockBurst<sup>TM</sup>

- Auto ACK & retransmit

- Address and CRC computation

- On the air data rate 1 or 2Mbps

- Digital interface (SPI) speed 0-8 Mbps

- 125 RF channel operation

- Short switching time enable frequency hopping

- Fully RF compatible with nRF24XX

- 5V tolerant signal input pads

- 20-pin package (QFN20 4x4mm)

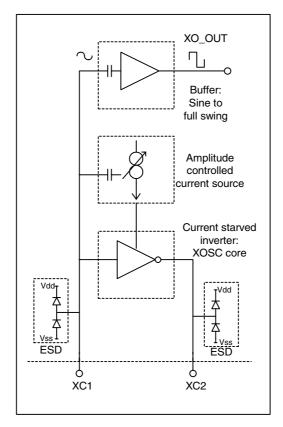

- Uses ultra low cost +/- 60 ppm crystal

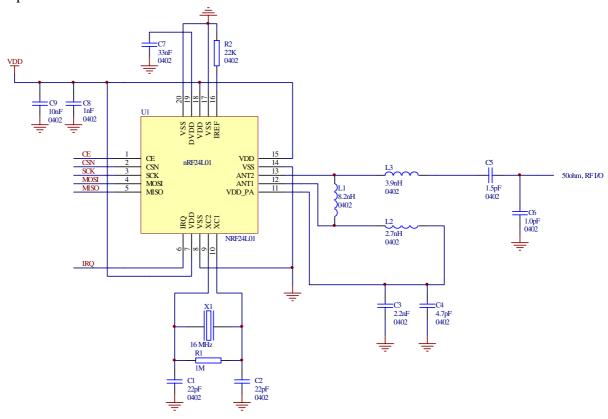

- Uses low cost chip inductors and 2-layer PCB

- Power supply range: 1.9 to 3.6 V

#### **APPLICATIONS**

- Wireless mouse, keyboard, joystick

- Keyless entry

- Wireless data communication

- Alarm and security systems

- Home automation

- Surveillance

- Automotive

- Telemetry

- Intelligent sports equipment

- Industrial sensors

- Toys

# **GENERAL DESCRIPTION**

nRF24L01 is a single chip radio transceiver for the world wide 2.4 - 2.5 GHz ISM band. The transceiver consists of a fully integrated frequency synthesizer, a power amplifier, a crystal oscillator, a demodulator, modulator and Enhanced ShockBurst<sup>TM</sup> protocol engine. Output power, frequency channels, and protocol setup are easily programmable through a SPI interface. Current consumption is very low, only 9.0mA at an output power of -6dBm and 12.3mA in RX mode. Built-in Power Down and Standby modes makes power saving easily realizable.

#### **QUICK REFERENCE DATA**

| Parameter                                     | Value      | Unit |

|-----------------------------------------------|------------|------|

| Minimum supply voltage                        | 1.9        | V    |

| Maximum output power                          | 0          | dBm  |

| Maximum data rate                             | 2000       | kbps |

| Supply current in TX mode @ 0dBm output power | 11.3       | mA   |

| Supply current in RX mode @ 2000 kbps         | 12.3       | mA   |

| Temperature range                             | -40 to +85 | °C   |

| Sensitivity @ 1000 kbps                       | -85        | dBm  |

| Supply current in Power Down mode             | 900        | nA   |

Table 1 nRF24L01 quick reference data

| Type Number    | Description                                          | Version |

|----------------|------------------------------------------------------|---------|

| nRF24L01       | 20 pin QFN 4x4, RoHS & SS-00259 compliant            | D       |

| nRF24L01 IC    | Bare Dice                                            | D       |

| nRF24L01-EVKIT | Evaluation kit (2 test PCB, 2 configuration PCB, SW) | 1.0     |

Table 2 nRF24L01 ordering information

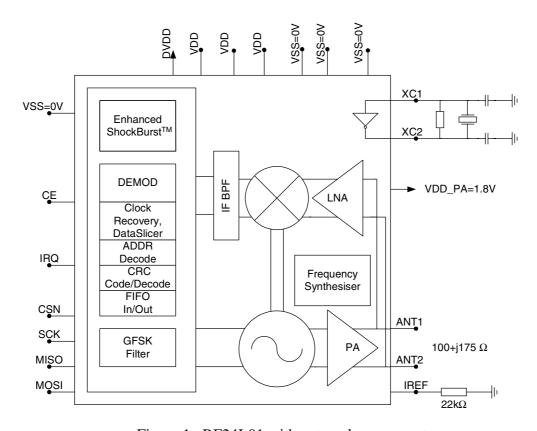

# **BLOCK DIAGRAM**

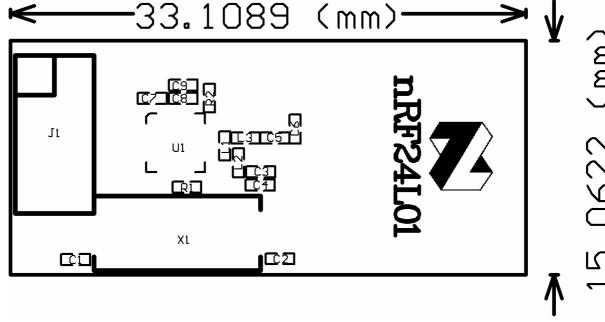

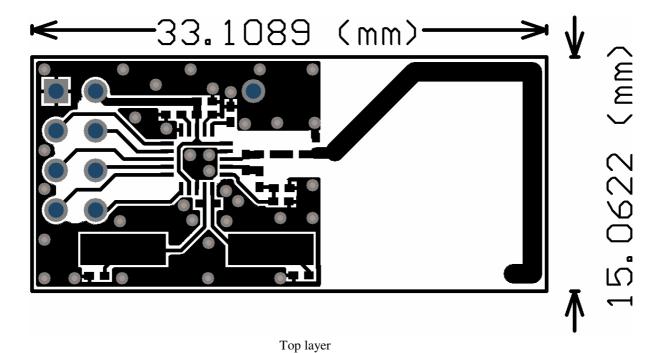

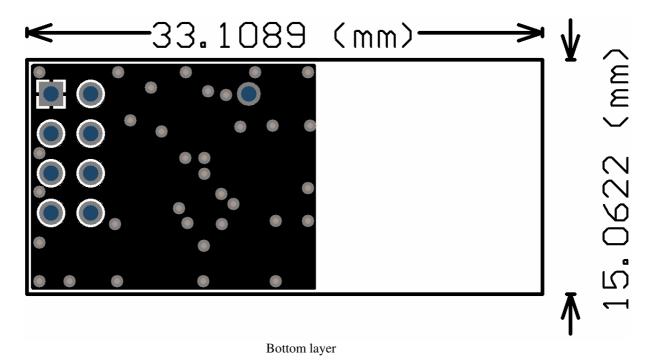

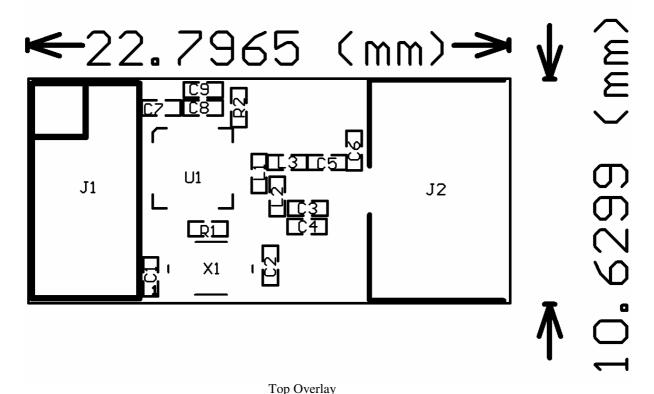

Figure 1 nRF24L01 with external components.

# **PIN FUNCTIONS**

| Pin | Name   | Pin function   | Description                                             |

|-----|--------|----------------|---------------------------------------------------------|

| 1   | CE     | Digital Input  | Chip Enable Activates RX or TX mode                     |

| 2   | CSN    | Digital Input  | SPI Chip Select                                         |

| 3   | SCK    | Digital Input  | SPI Clock                                               |

| 4   | MOSI   | Digital Input  | SPI Slave Data Input                                    |

| 5   | MISO   | Digital Output | SPI Slave Data Output, with tri-state option            |

| 6   | IRQ    | Digital Output | Maskable interrupt pin                                  |

| 7   | VDD    | Power          | Power Supply (+3V DC)                                   |

| 8   | VSS    | Power          | Ground (0V)                                             |

| 9   | XC2    | Analog Output  | Crystal Pin 2                                           |

| 10  | XC1    | Analog Input   | Crystal Pin 1                                           |

| 11  | VDD_PA | Power Output   | Power Supply (+1.8V) to Power Amplifier                 |

| 12  | ANT1   | RF             | Antenna interface 1                                     |

| 13  | ANT2   | RF             | Antenna interface 2                                     |

| 14  | VSS    | Power          | Ground (0V)                                             |

| 15  | VDD    | Power          | Power Supply (+3V DC)                                   |

| 16  | IREF   | Analog Input   | Reference current                                       |

| 17  | VSS    | Power          | Ground (0V)                                             |

| 18  | VDD    | Power          | Power Supply (+3V DC)                                   |

| 19  | DVDD   | Power Output   | Positive Digital Supply output for de-coupling purposes |

| 20  | VSS    | Power          | Ground (0V)                                             |

Table 3 nRF24L01 pin function

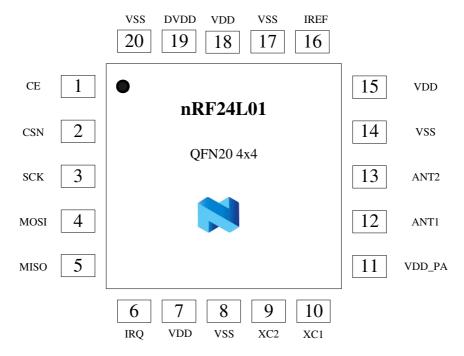

# PIN ASSIGNMENT

Figure 2 nRF24L01 pin assignment (top view) for a QFN20 4x4 package.

nRF24L01 Single Chip 2.4 GHz Radio Transceiver

# **ELECTRICAL SPECIFICATIONS**

Conditions: VDD = +3V, VSS = 0V,  $T_A = -40$ °C to +85°C

| Symbol               | Parameter (condition)                                                          | Notes | Min.     | Typ. | Max.   | Units |

|----------------------|--------------------------------------------------------------------------------|-------|----------|------|--------|-------|

|                      | Operating conditions                                                           |       |          |      |        |       |

| VDD                  | Supply voltage                                                                 |       | 1.9      | 3.0  | 3.6    | V     |

| TEMP                 | Operating Temperature                                                          |       | -40      | +27  | +85    | °C    |

|                      | Digital input pin                                                              |       |          |      |        |       |

| $V_{\mathrm{IH}}$    | HIGH level input voltage                                                       | 1     | 0.7VDD   |      | 5.25   | V     |

| $V_{\rm IL}$         | LOW level input voltage                                                        |       | VSS      |      | 0.3VDD | V     |

|                      | Digital output pin                                                             |       |          |      |        |       |

| $V_{OH}$             | HIGH level output voltage (I <sub>OH</sub> =-0.25mA)                           |       | VDD- 0.3 |      | VDD    | V     |

| $V_{OL}$             | LOW level output voltage (I <sub>OL</sub> =0.25mA)                             |       | VSS      |      | 0.3    | V     |

|                      | General RF conditions                                                          |       |          |      |        |       |

| $f_{OP}$             | Operating frequency                                                            | 2     | 2400     |      | 2525   | MHz   |

| $f_{XTAL}$           | Crystal frequency                                                              |       |          | 16   |        | MHz   |

| $\Delta f_{1M}$      | Frequency deviation @ 1000kbps                                                 |       |          | ±160 |        | kHz   |

| $\Delta f_{2M}$      | Frequency deviation @ 2000kbps                                                 |       |          | ±320 |        | kHz   |

| $R_{GFSK}$           | Data rate ShockBurst <sup>TM</sup>                                             |       | >0       |      | 2000   | kbps  |

| F <sub>CHANNEL</sub> | Channel spacing @ 1000kbps                                                     |       |          | 1    |        | MHz   |

| F <sub>CHANNEL</sub> | Channel spacing @ 2000kbps                                                     |       |          | 2    |        | MHz   |

|                      | Transmitter operation                                                          |       |          |      |        |       |

| $P_{RF}$             | Maximum Output Power                                                           | 3     |          | 0    | +4     | dBm   |

| P <sub>RFC</sub>     | RF Power Control Range                                                         |       | 16       | 18   | 20     | dB    |

| P <sub>RFCR</sub>    | RF Power Accuracy                                                              |       |          |      | ±4     | dB    |

| $P_{BW}$             | 20dB Bandwidth for Modulated Carrier (2000kbps)                                |       |          | 1800 | 2000   | kHz   |

| P <sub>RF1</sub>     | 1st Adjacent Channel Transmit Power 2MHz                                       |       |          |      | -20    | dBm   |

| P <sub>RF2</sub>     | 2 <sup>nd</sup> Adjacent Channel Transmit Power 4MHz                           |       |          |      | -50    | dBm   |

| $I_{VDD}$            | Supply current @ 0dBm output power                                             | 4     |          | 11.3 |        | mA    |

| $I_{VDD}$            | Supply current @ -18dBm output power                                           |       |          | 7.0  |        | mA    |

| $I_{VDD}$            | Average Supply current @ -6dBm output power, Enhanced ShockBurst <sup>TM</sup> | 5     |          | 0.05 |        | mA    |

| $I_{VDD}$            | Supply current in Standby-I mode                                               | 6     |          | 32   |        | μΑ    |

| $I_{VDD}$            | Supply current in power down                                                   |       |          | 900  |        | nA    |

$<sup>^1</sup>$  All digital inputs handle up to 5.25V signal inputs. Keep in mind that the VDD of the nRF24L01 must match the  $V_{IH}$  of the driving device for output pins.  $^2$  Usable band is determined by local regulations

<sup>&</sup>lt;sup>3</sup> Antenna load impedance =  $15\Omega$ +j88Ω

Antenna load impedance = 1327+3882. Antenna load impedance =  $15\Omega+38\Omega$ . Effective data rate 1000kbps or 2000 kbps 5 Antenna load impedance =  $15\Omega+38\Omega$ . Effective data rate 10kbps and full packets

<sup>&</sup>lt;sup>6</sup> Given for a 12pF crystal. Current when using external clock is dependent on signal swing.

|                    | Receiver operation                                    |    |                                   |     |

|--------------------|-------------------------------------------------------|----|-----------------------------------|-----|

| $I_{\mathrm{VDD}}$ | Supply current one channel 2000kbps                   |    | 12.3                              | mA  |

| $I_{\mathrm{VDD}}$ | Supply current one channel 1000kbps                   |    | 11.8                              | mA  |

| $RX_{SENS}$        | Sensitivity at 0.1%BER (@2000kbps)                    |    | -82                               | dBm |

| $RX_{SENS}$        | Sensitivity at 0.1%BER (@1000kbps)                    |    | -85                               | dBm |

| C/I <sub>CO</sub>  | C/I Co-channel (@2000kbps)                            | 7  | 7 <sup>8</sup> /11 <sup>9</sup>   | dB  |

| C/I <sub>1ST</sub> | 1 <sup>st</sup> Adjacent Channel Selectivity C/I 2MHz |    | 1/4                               | dB  |

| C/I <sub>2ND</sub> | 2 <sup>nd</sup> Adjacent Channel Selectivity C/I 4MHz |    | -21/-20                           | dB  |

| C/I <sub>3RD</sub> | 3 <sup>rd</sup> Adjacent Channel Selectivity C/I 6MHz |    | -27/-27                           | dB  |

| C/I <sub>CO</sub>  | C/I Co-channel (@1000kbps)                            | 10 | 9 <sup>11</sup> /12 <sup>12</sup> | dB  |

| C/I <sub>1ST</sub> | 1 <sup>st</sup> Adjacent Channel Selectivity C/I 1MHz |    | 8/8                               | dB  |

| C/I <sub>2ND</sub> | 2 <sup>nd</sup> Adjacent Channel Selectivity C/I 2MHz |    | -22/-21                           | dB  |

| C/I <sub>3RD</sub> | 3 <sup>rd</sup> Adjacent Channel Selectivity C/I 3MHz |    | -30/-30                           | dB  |

Table 4 nRF24L01 RF specifications

<sup>&</sup>lt;sup>7</sup> Data rate is 2000kbps for the following C/I measurements

<sup>8</sup> According to ETSI EN 300 440-1 V1.3.1 (2001-09) page 27

<sup>9</sup> nRF24L01 equal modulation on interfering signal

<sup>10</sup> Data rate is 1000kbps for the following C/I measurements

<sup>11</sup> According to ETSI EN 300 440-1 V1.3.1 (2001-09) page 27

<sup>12</sup> nRF24L01 equal modulation on interfering signal

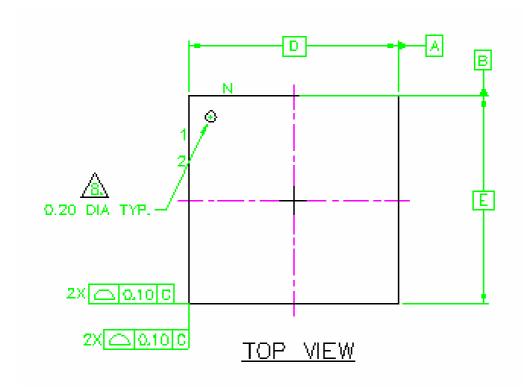

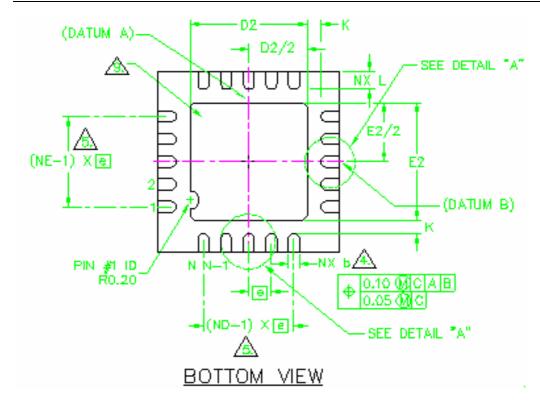

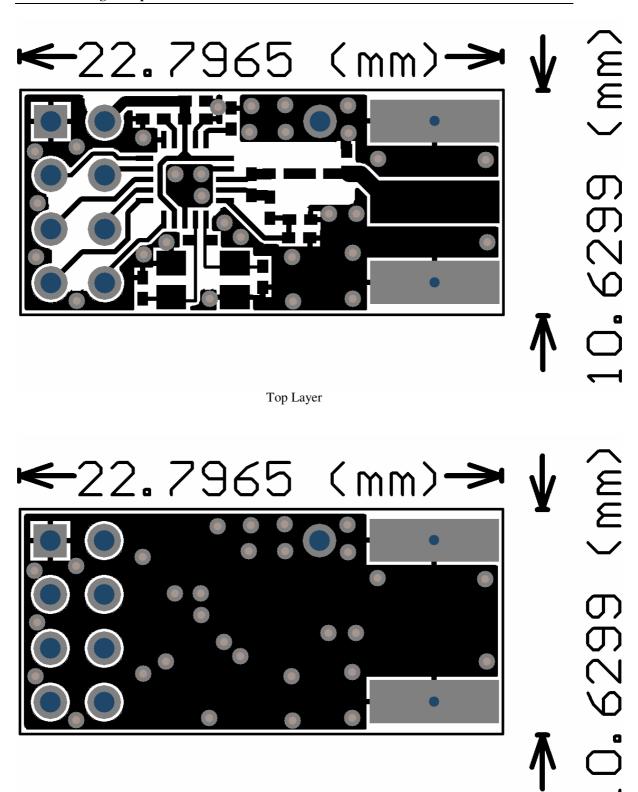

# **PACKAGE OUTLINE**

nRF24L01 uses the QFN20 4x4 package, with matt tin plating.

| Package Type |      | A    | A1   | A3   | K    | D/E                   | e       | D2/E2 | L    | L1   | b    |

|--------------|------|------|------|------|------|-----------------------|---------|-------|------|------|------|

| Saw QFN20    | Min  | 0.80 | 0.00 |      |      |                       |         | 2.50  | 0.35 |      | 0.18 |

| (4x4 mm)     | Тур. | 0.85 | 0.02 | 0.20 | 0.20 | 4.0 BSC <sup>13</sup> | 0.5 BSC | 2.60  | 0.40 | 0.15 | 0.25 |

|              | Max  | 0.95 | 0.05 | REF. | min  |                       |         | 2.70  | 0.45 | max  | 0.30 |

|              |      |      |      |      |      |                       |         |       |      |      |      |

Figure 3 nRF24L01 Package Outline.

\_

<sup>13</sup> BSC: Basic Spacing between Centers, ref. JEDEC standard 95, page 4 17-11/A

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

# Package marking:

| n | R | F |   | В | Χ |

|---|---|---|---|---|---|

| 2 | 4 | L | 0 | 1 |   |

| Υ | Υ | W | W | L | L |

#### Abbreviations:

B – Build Code, i.e. unique code for production sites,

package type and test platform

X – "X" grade, i.e. Engineering Samples (optional)

YY – 2 digit Year number WW – 2 digit Week number LL – 2 letter wafer lot number code

# **Absolute Maximum Ratings**

**Supply voltages**

VDD..... - 0.3V to + 3.6V

VSS ...... 0V

Input voltage

V<sub>I</sub>..... - 0.3V to 5.25V

**Output voltage**

V<sub>0</sub>......VSS to VDD

**Total Power Dissipation**

$P_D(T_A=85^{\circ}C)$ ......60mW

**Temperatures**

Operating Temperature.... -  $40^{\circ}$ C to +  $85^{\circ}$ C Storage Temperature..... -  $40^{\circ}$ C to +  $125^{\circ}$ C

Note: Stress exceeding one or more of the limiting values may cause permanent damage to the device.

#### **ATTENTION!**

Electrostatic Sensitive Device Observe Precaution for handling.

# **Glossary of Terms**

| Term    | Description                                        |

|---------|----------------------------------------------------|

| ACK     | Acknowledgement                                    |

| ART     | Auto Re-Transmit                                   |

| CE      | Chip Enable                                        |

| CLK     | Clock                                              |

| CRC     | Cyclic Redundancy Check                            |

| CSN     | Chip Select NOT                                    |

| ESB     | Enhanced ShockBurst <sup>TM</sup>                  |

| GFSK    | Gaussian Frequency Shift Keying                    |

| IRQ     | Interrupt Request                                  |

| ISM     | Industrial-Scientific-Medical                      |

| LNA     | Low Noise Amplifier                                |

| LSB     | Least Significant Bit                              |

| LSByte  | Least Significant Byte                             |

| Mbps    | Megabit per second                                 |

| MCU     | Micro Controller Unit                              |

| MISO    | Master In Slave Out                                |

| MOSI    | Master Out Slave In                                |

| MSB     | Most Significant Bit                               |

| MSByte  | Most Significant Byte                              |

| PCB     | Printed Circuit Board                              |

| PER     | Packet Error Rate                                  |

| PID     | Packet Identity Bits                               |

| PLD     | Payload                                            |

| PRX     | Primary RX                                         |

| PTX     | Primary TX                                         |

| PWR_DWN | Power Down                                         |

| PWR_UP  | Power Up                                           |

| RoHS    | Restriction of use of Certain Hazardous Substances |

| RX      | Receive                                            |

| RX_DR   | Receive Data Ready                                 |

| SPI     | Serial Peripheral Interface                        |

| TX      | Transmit                                           |

| TX_DS   | Transmit Data Sent                                 |

Table 5 Glossary

nRF24L01 Single Chip 2.4 GHz Radio Transceiver

#### **FUNCTIONAL DESCRIPTION**

#### Modes of operation

The nRF24L01 can be set in the following main modes depending on the level of the following primary I/Os and configuration registers:

| Mode       | PWR_UP<br>register | PRIM_RX<br>register | CE           | FIFO state                                             |

|------------|--------------------|---------------------|--------------|--------------------------------------------------------|

| RX mode    | 1                  | 1                   | 1            | -                                                      |

| TX mode    | 1                  | 0                   | 1            | Data in TX FIFO                                        |

| TX mode    | 1                  | 0                   | 1 <b>→</b> 0 | Stays in TX mode until packet transmission is finished |

| Standby-II | 1                  | 0                   | 1            | TX FIFO empty                                          |

| Standby-I  | 1                  | -                   | 0            | No ongoing packet transmission                         |

| Power Down | 0                  | -                   | -            | -                                                      |

Table 6 nRF24L01 main modes

An overview of the nRF24L01 I/O pins in different modes is given in Table 7.

#### Pin functions in the different modes of nRF24L01

| Pin Name | Direction | TX Mode          | RX Mode                     | Standby Modes | Power Down |  |  |

|----------|-----------|------------------|-----------------------------|---------------|------------|--|--|

| CE       | Input     | High Pulse >10µs | High                        | Low           | -          |  |  |

| CSN      | Input     |                  | SPI Chip Select, active low |               |            |  |  |

| SCK      | Input     |                  | SPI (                       | Clock         |            |  |  |

| MOSI     | Input     |                  | SPI Ser                     | ial Input     |            |  |  |

| MISO     | Tri-state |                  | SPI Seria                   | al Output     |            |  |  |

|          | Output    | •                |                             |               |            |  |  |

| IRQ      | Output    |                  | Interrupt,                  | active low    |            |  |  |

Table 7 Pin functions of the nRF24L01

## Standby Modes

Standby-I mode is used to minimize average current consumption while maintaining short start up times. In this mode, part of the crystal oscillator is active. In Standby-II mode some extra clock buffers are active compared to Standby-I mode. Standby-II occurs when CE is held high on a PTX device with empty TX FIFO. The configuration word content is maintained during Standby modes. SPI interface may be activated. For start up time see Table 13.

#### Power Down Mode

In power down nRF24L01 is disabled with minimal current consumption. When entering this mode the device is not active, but all registers values available from the SPI interface are maintained during power down and the SPI interface may be activated (CSN=0). For start up time see Table 13. The power down is controlled by the PWR\_UP bit in the CONFIG register.

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

## Packet Handling Methods

nRF24L01 has the following Packet Handling Methods:

- ShockBurst<sup>TM</sup> (compatible with nRF2401, nRF24E1, nRF2402 and nRF24E2 with 1Mbps data rate, see page 26)

- Enhanced ShockBurst<sup>TM</sup>

#### ShockBurst<sup>TM</sup>

ShockBurst<sup>TM</sup> makes it possible to use the high data rate offered by nRF24L01 without the need of a costly, high-speed microcontroller (MCU) for data processing/clock recovery. By placing all high speed signal processing related to RF protocol on-chip, nRF24L01 offers the application microcontroller a simple SPI compatible interface, the data rate is decided by the interface-speed the micro controller itself sets up. By allowing the digital part of the application to run at low speed, while maximizing the data rate on the RF link, ShockBurst<sup>TM</sup> reduces the average current consumption in applications.

In ShockBurst<sup>TM</sup> RX, IRQ notifies the MCU when a valid address and payload is received respectively. The MCU can then clock out the received payload from an nRF24L01 RX FIFO.

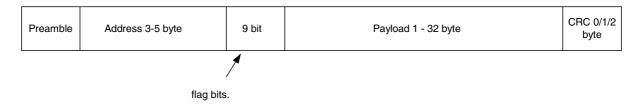

In ShockBurst<sup>TM</sup> TX, nRF24L01 automatically generates preamble and CRC, see Table 12. IRQ notifies the MCU that the transmission is completed. All together, this means reduced memory demand in the MCU resulting in a low cost MCU, as well as reduced software development time. nRF24L01 has a three level deep RX FIFO (shared between 6 pipes) and a three level deep TX FIFO. The MCU can access the FIFOs at any time, in power down mode, in standby modes, and during RF packet transmission. This allows the slowest possible SPI interface compared to the average data-rate, and may enable usage of an MCU without hardware SPI.

#### Enhanced ShockBurst<sup>TM</sup>

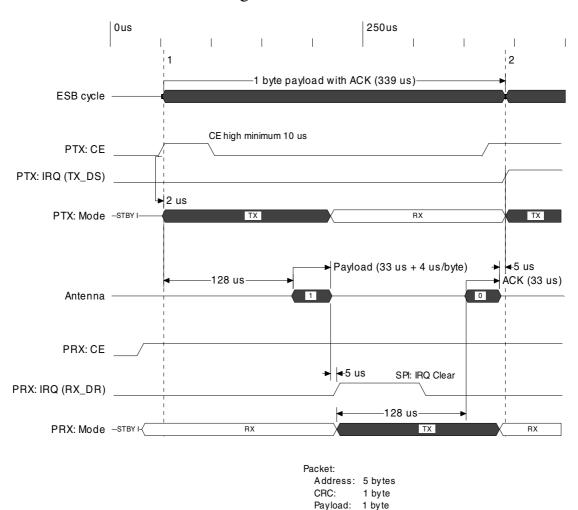

Enhanced ShockBurst<sup>TM</sup> is a packet handling method with functionality that makes bidirectional link protocol implementation easier and more efficient. In a typical bidirectional link, one will let the terminating part acknowledge received packets from the originating part in order to make it possible to detect data loss. Data loss can then be recovered by retransmission. The idea with Enhanced ShockBurst<sup>TM</sup> is to let nRF24L01 handle both acknowledgement of received packets and retransmissions of lost packets, without involvement from the microcontroller.

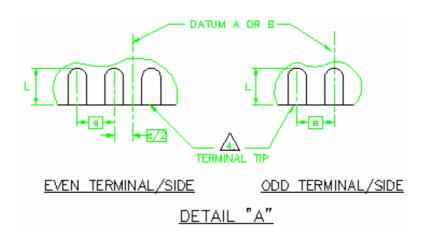

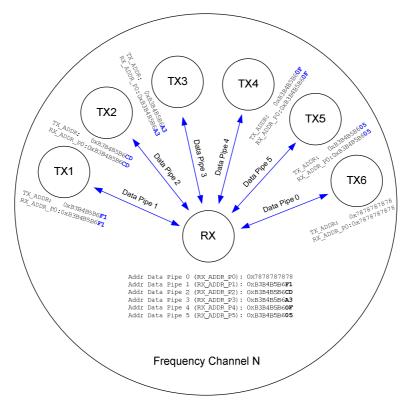

Figure 4: nRF24L01 in a star network configuration

An nRF24L01 configured as primary RX (PRX) will be able to receive data trough 6 different data pipes, see Figure 4. A data pipe will have a unique address but share the same frequency channel. This means that up to 6 different nRF24L01 configured as primary TX (PTX) can communicate with one nRF24L01 configured as PRX, and the nRF24L01 configured as PRX will be able to distinguish between them. Data pipe 0 has a unique 40 bit configurable address. Each of data pipe 1-5 has an 8 bit unique address and shares the 32 most significant address bits. All data pipes can perform full Enhanced ShockBurst<sup>TM</sup> functionality.

nRF24L01 will use the data pipe address when acknowledging a received packet. This means that nRF24L01 will transmit ACK with the same address as it receives payload at. In the PTX device data pipe 0 is used to received the acknowledgement, and therefore the receive address for data pipe 0 has to be equal to the transmit address to be able to receive the acknowledgement. See Figure 5 for addressing example.

Figure 5: Example on how the acknowledgement addressing is done

An nRF24L01 configured as PTX with Enhanced ShockBurst<sup>TM</sup> enabled, will use the ShockBurst<sup>TM</sup> feature to send a packet whenever the microcontroller wants to. After the packet has been transmitted, nRF24L01 will switch on its receiver and expect an acknowledgement to arrive from the terminating part. If this acknowledgement fails to arrive, nRF24L01 will retransmit the same packet until it receives an acknowledgement or the number of retries exceeds the number of allowed retries given in the SETUP\_RETR\_ARC register. If the number of retries exceeds the number of allowed retries, this will be showed by the STATUS register bit MAX\_RT which gives an interrupt.

Whenever an acknowledgement is received by an nRF24L01 it will consider the last transmitted packet as delivered. It will then be cleared from the TX FIFO, and the TX DS IRO source will be set high.

With Enhanced ShockBurst<sup>TM</sup> nRF24L01 offers the following benefits:

- Highly reduced current consumption due to short time on air and sharp timing when operating with acknowledgement traffic

- Lower system cost. Since the nRF24L01 handles all the high-speed link layer operations, like re-transmission of lost packet and generating acknowledgement to received packets, it is no need for hardware SPI on the system microcontroller to interface the nRF24L01. The interface can be done by using general purpose IO pins on a low cost microcontroller where the SPI is emulated in firmware. With the nRF24L01 this will be sufficient speed even when running a bi-directional link.

- Greatly reduced risk of "on-air" collisions due to short time on air

- Easier firmware development since the link layer is integrated on chip

## nRF24L01 Single Chip 2.4 GHz Radio Transceiver

# Enhanced ShockBurst<sup>TM</sup> Transmitting Payload:

- 1. The configuration bit PRIM\_RX has to be low.

- 2. When the application MCU has data to send, the address for receiving node (TX\_ADDR) and payload data (TX\_PLD) has to be clocked into nRF24L01 via the SPI interface. The width of TX-payload is counted from number of bytes written into the TX FIFO from the MCU. TX\_PLD must be written continuously while holding CSN low. TX\_ADDR does not have to be rewritten if it is unchanged from last transmit. If the PTX device shall receive acknowledge, data pipe 0 has to be configured to receive the acknowledgement. The receive address for data pipe 0 (RX\_ADDR\_P0) has to be equal to the transmit address (TX\_ADDR) in the PTX device. For the example in Figure 5 the following address settings have to be performed for the TX5 device and the RX device:

TX5 device: TX\_ADDR = 0xB3B4B5B605 TX5 device: RX\_ADDR\_P0 = 0xB3B4B5B605 RX device: RX\_ADDR\_P5 = 0xB3B4B5B605

- 3. A high pulse on CE starts the transmission. The minimum pulse width on CE is 10 µs.

- 4. nRF24L01 ShockBurst<sup>TM</sup>:

- Radio is powered up

- 16 MHz internal clock is started.

- RF packet is completed (see the packet description)

- Data is transmitted at high speed (1 Mbps or 2 Mbps configured by MCU).

- 5. If auto acknowledgement is activated (ENAA P0=1) the radio goes into RX mode immediately. If a valid packet has been received in the valid acknowledgement time window, the transmission is considered a success. The TX DS bit in the status register is set high and the payload is removed from TX FIFO. If a valid acknowledgement is not received in the specified time window, the payload is resent (if auto retransmit is enabled). If the auto retransmit counter (ARC\_CNT) exceeds the programmed maximum limit (ARC), the MAX\_RT bit in the status register is set high. The payload in TX FIFO is NOT removed. The IRQ pin will be active when MAX\_RT or TX\_DS is high. To turn off the IRQ pin, the interrupt source must be reset by writing to the status register (see Interrupt chapter). If no acknowledgement is received for a packet after the maximum number of retries, no further packets can be sent before the MAX RX interrupt is cleared. The packet loss counter (PLOS CNT) is incremented at each MAX RT interrupt. I.e. ARC\_CNT counts the number of retries that was required to get a single packet through. PLOS\_CNT counts the number of packets that did not get through after maximum number of retries.

- 6. The device goes into Standby-I mode if CE is low. Otherwise next payload in TX FIFO will be sent. If TX FIFO is empty and CE is still high, the device will enter Standby-II mode.

- 7. If the device is in Standby-II mode, it will go to Standby-I mode immediately if CE is set low.

# Enhanced ShockBurst<sup>TM</sup> Receive Payload:

1. RX is selected by setting the PRIM\_RX bit in the configuration register to high. All data pipes that shall receive data must be enabled (EN\_RXADDR register),

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

auto acknowledgement for all pipes running Enhanced ShockBurst<sup>TM</sup> has to be enabled (EN\_AA register), and the correct payload widths must be set (RX\_PW\_Px registers). Addresses have to be set up as described in item 2 in the Enhanced ShockBurst<sup>TM</sup> transmit payload chapter above.

- 2. Active RX mode is started by setting CE high.

- 3. After 130µs nRF24L01 is monitoring the air for incoming communication.

- 4. When a valid packet has been received (matching address and correct CRC), the payload is stored in the RX-FIFO, and the RX\_DR bit in status register is set high. The IRQ pin will be active when RX\_DR is high. RX\_P\_NO in status register will indicate what data pipe the payload has been received in.

- 5. If auto acknowledgement is enabled, an acknowledgement is sent back.

- 6. MCU sets the CE pin low to enter Standby-I mode (low current mode).

- 7. MCU can clock out the payload data at a suitable rate via the SPI interface.

- 8. The device is now ready for entering TX or RX mode or power down mode.

# Two way communication with payload in both directions

If payload shall be sent in both directions, the PRIM\_RX register must be toggled by redefining the device from PRX to PTX or vice versa. The controlling processors must handle the synchronicity between a PTX and a PRX. Data buffering in both RX FIFO and TX FIFO simultaneously is possible, but restricted to data pipes 1 to 5. The third level in TX FIFO shall only be written in RX, TX or Standby-II mode if data is stored in RX FIFO

## Auto Acknowledgement (RX)

The auto acknowledgement function reduces the load of the external microcontroller, and may remove the need for dedicated SPI hardware in a mouse/keyboard or comparable systems, and hence reduce cost and average current consumption. Auto acknowledgement can be configured individually for each data pipe via the SPI interface.

If auto acknowledgement is enabled and a valid packet (correct data pipe address and CRC) is received, the device will enter TX mode and send an acknowledgement packet. After the device has sent the acknowledgement packet, normal operation resumes, and the mode is determined by the PRIM\_RX register and CE pin.

# Auto Re-Transmission (ART) (TX)

An auto retransmission function is available. It will be used at the TX side in an auto acknowledgement system. In the SETUP\_RETR register it will be possible to state how many times the data in the data register will be resent if data is not acknowledged. After each sending, the device will enter RX mode and wait a specified time period for acknowledgement. When the acknowledgement packet is received, the device will return to normal transmit function. If there is no more unsent data in the TX FIFO and the CE pin is low, the device will go into Standby-I mode. If the acknowledgement is not received, the device will go back to TX mode and resend the data. This will continue until acknowledgement is received, or a time out occurs

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

(i.e. the maximum number of sending is reached). The only way to reset this is to set the PWR\_UP bit low or let the auto retransmission finish. A packet loss counter will be incremented each time a packet does not succeed to reach the destination before time out. (Time out is indicated by the MAX\_RT interrupt.) The packet loss counter is reset when writing to the RF channel register.

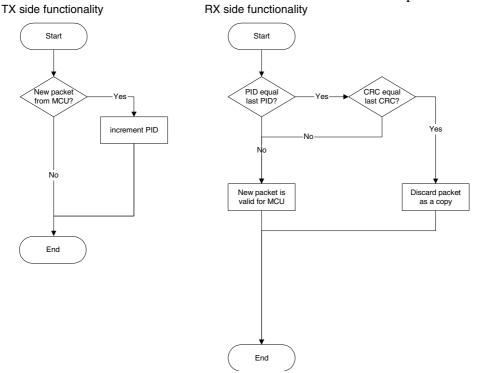

# Packet Identity (PID) and CRC used by Enhanced ShockBurst<sup>TM</sup>

Each packet contains a two bit wide PID field to detect if the received packet is new or resent. The PID will prevent that the PRX device presents the same payload more than once to the microcontroller. This PID field is incremented at the TX side for each new packet received via the SPI interface. The PID and CRC field is used by the PRX device to determine whether a packet is resent or new. When several data is lost on the link, the PID fields may in some cases become equal to last received PID. If a packet has the same PID as the previous packet, nRF24L01 will compare the CRC sums from both packets. If they also are equal, the last received packet is considered as a copy of the previous and is discarded.

#### 1: PRX device:

The PRX device compares the received PID with the last PID. If the PID fields are different, the packet is considered to be new. If the PID is equal to last received PID, the received packet might be the same as last time. The receiver must check if the CRC is equal to the previous CRC. If the CRC is equal to the previous one, the packet is probably the same, and will be discarded.

#### 2: PTX device:

The transmitter increments the PID field each time it sends a new packet.

Figure 6 PID generation/detection

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

The length of the CRC is configurable through the SPI interface. It is important to notice that the CRC is calculated over the whole packet including address, PID and payload. No packet is accepted as correct if the CRC fails. This is an extra requirement for packet acceptance that is not illustrated in the figure above.

# Stationary Disturbance Detection – CD

Carrier Detect (CD) is set high when an in-band RF signal is detected in RX mode, otherwise CD is low. The internal CD signal is filtered before presented to CD register. The internal CD signal must be high for at least 128 $\mu$ s. In Enhanced ShockBurst<sup>TM</sup> it is recommended to use the Carrier Detect functionality only when the PTX device does not succeed to get packets through, as indicated by the MAX\_RT interrupt for single packets and by the packet loss counter (PLOS\_CNT) if several packets are lost. If the PLOS\_CNT in the PTX device indicates to high rate of packet losses, the device can be configured to a PRX device for a short time ( $T_{\text{stbt2a}}$  + CD-filter delay = 130 $\mu$ s+128 $\mu$ s = 258 $\mu$ s) to check CD. If CD was high (jam situation), the frequency channel should be changed. If CD was low (out of range), it may continue on the same frequency channel, but perform other adjustments. (A dummy write to the RF\_CH will clear the PLOS\_CNT.)

## **Data Pipes**

nRF24L01 configured as PRX can receive data addressed to 6 different data pipes in one physical frequency channel. Each data pipe has its own unique address and can be configured to have individual behavior.

The data pipes are enabled with the bits in the EN\_RXADDR register. By default only data pipe 0 and 1 are enabled.

The address for each data pipe is configured in the RX\_ADDR\_Px registers. Always ensure that none of the data pipes have the exact same address.

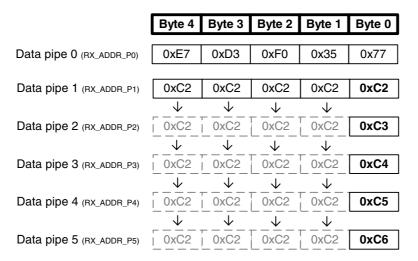

Data pipe 0 has a unique 40 bit configurable address. Data pipes 1-5 share the 32 most significant address bits and have only the LSByte unique for each data pipe. Figure 7 shows an example of how data pipes 0-5 are addressed. All pipes can have up to 40 bit address, but for pipe 1-5 only the LSByte is different, and the LSByte must be unique for all pipes.

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

Figure 7: Addressing data pipes 0-5

When a packet has been received at one of the data pipes and the data pipe is setup to generate acknowledgement, nRF24L01 will generate an acknowledgement with an address that equals the data pipe address where the packet was received.

Some configuration settings are common to all data pipes and some are individual. The following settings are common to all data pipes:

- CRC enabled/disabled (CRC always enabled when ESB is enabled)

- CRC encoding scheme

- RX address width

- Frequency channel

- RF data rate

- LNA gain

- RF output power

nRF24L01 Single Chip 2.4 GHz Radio Transceiver

#### **DEVICE CONFIGURATION**

All configuration of nRF24L01 is defined by values in some configuration registers. All these registers are writable via the SPI interface.

#### **SPI** Interface

The SPI interface is a standard SPI interface with a maximum data rate of 10Mbps. Most registers are readable.

#### **SPI Instruction Set**

The available commands to be used on the SPI interface are shown below. Whenever CSN is set low the interface expects an instruction. Every new instruction must be started by a high to low transition on CSN.

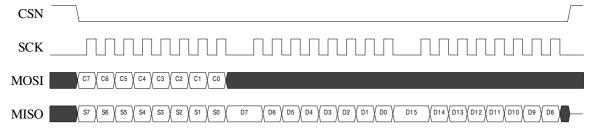

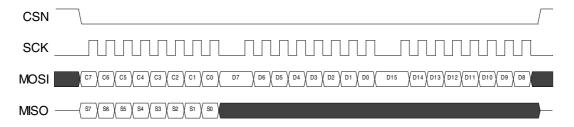

In parallel to the SPI instruction word applied on the MOSI pin, the STATUS register is shifted serially out on the MISO pin.

The serial shifting SPI commands is on the format:

<Instruction word: MSBit to LSBit (one byte)>

< Data bytes: LSByte to MSByte, MSBit in each byte first>

See Figure 8 and Figure 9.

| <b>Instruction Name</b> | Instruction     | # Data                  | Operation                                                                                                                                                                                                                                                        |

|-------------------------|-----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Format [binary] | Bytes                   |                                                                                                                                                                                                                                                                  |

| R_REGISTER              | 000A AAAA       | 1 to 5<br>LSByte first  | Read registers. AAAAA = 5 bit Memory Map Address                                                                                                                                                                                                                 |

| W_REGISTER              | 001A AAAA       | 1 to 5<br>LSByte first  | Write registers. AAAAA = 5 bit Memory Map Address<br>Executable in power down or standby modes only.                                                                                                                                                             |

| R_RX_PAYLOAD            | 0110 0001       | 1 to 32<br>LSByte first | Read RX-payload: 1 – 32 bytes. A read operation will always start at byte 0. Payload will be deleted from FIFO after it is read. Used in RX mode.                                                                                                                |

| W_TX_PAYLOAD            | 1010 0000       | 1 to 32<br>LSByte first | Used in TX mode. Write TX-payload: 1 – 32 bytes. A write operation will always start at byte 0.                                                                                                                                                                  |

| FLUSH_TX                | 1110 0001       | 0                       | Flush TX FIFO, used in TX mode                                                                                                                                                                                                                                   |

| FLUSH_RX                | 1110 0010       | 0                       | Flush RX FIFO, used in RX mode Should not be executed during transmission of acknowledge, i.e. acknowledge package will not be completed.                                                                                                                        |

| REUSE_TX_PL             | 1110 0011       | 0                       | Used for a PTX device Reuse last sent payload. Packets will be repeatedly resent as long as CE is high. TX payload reuse is active until W_TX_PAYLOAD or FLUSH TX is executed. TX payload reuse must not be activated or deactivated during package transmission |

| NOP                     | 1111 1111       | 0                       | No Operation. Might be used to read the STATUS register                                                                                                                                                                                                          |

Table 8 Instruction set for the nRF24L01 SPI interface.

The W\_REGISTER and R\_REGISTER may operate on single or multi-byte registers. When accessing multi-byte registers one will read or write MSBit of LSByte first. The

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

writing can be terminated before all bytes in a multi-byte register has been written. In this case the unwritten MSByte(s) will remain unchanged. E.g. the LSByte of RX\_ADDR\_P0 can be modified by writing only one byte to the RX\_ADDR\_P0 register. The content of the status register will always be read to MISO after a high to low transition on CSN.

## Interrupt

The nRF24L01 has an active low interrupt pin (IRQ). The interrupt pin is activated when TX\_DS, RX\_DR or MAX\_RT is set high in status register. When MCU writes '1' to the interrupt source, the IRQ pin will go inactive. The interrupt mask part of the CONFIG register is used to mask out the interrupt sources that are allowed to set the IRQ pin low. By setting one of the MASK bits high, the corresponding interrupt source will be disabled. By default all interrupt sources are enabled.

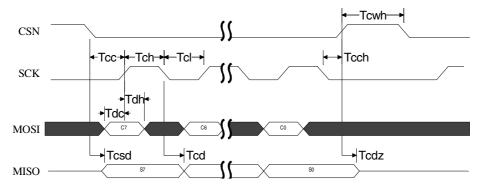

# **SPI** Timing

The interface supports SPI. SPI operation and timing is given in Figure 8 to Figure 10 and in Table 9 and Table 10. The device must be in one of the standby modes or power down mode before writing to the configuration registers. In Figure 8 to Figure 10 the following notations are used:

Cn - SPI Instruction Bit

Sn – Status Register Bit

Dn – Data Bit (note: LSByte to MSByte, MSBit in each byte first)

Figure 8 SPI read operation.

Figure 9 SPI write operation.

Figure 10 SPI NOP timing diagram.

| PARAMETER            | SYMBOL | MIN | MAX | UNITS |

|----------------------|--------|-----|-----|-------|

| Data to SCK Setup    | Tdc    | 2   |     | ns    |

| SCK to Data Hold     | Tdh    | 2   |     | ns    |

| CSN to Data Valid    | Tesd   |     | 38  | ns    |

| SCK to Data Valid    | Tcd    |     | 55  | ns    |

| SCK Low Time         | Tcl    | 40  |     | ns    |

| SCK High Time        | Tch    | 40  |     | ns    |

| SCK Frequency        | Fsck   | 0   | 8   | MHz   |

| SCK Rise and Fall    | Tr,Tf  |     | 100 | ns    |

| CSN to SCK Setup     | Tcc    | 2   |     | ns    |

| SCK to CSN Hold      | Tech   | 2   |     | ns    |

| CSN Inactive time    | Tcwh   | 50  |     | ns    |

| CSN to Output High Z | Tcdz   |     | 38  | ns    |

Table 9 SPI timing parameters ( $C_{Load} = 5pF$ ).

| PARAMETER            | SYMBOL | MIN | MAX | UNITS |

|----------------------|--------|-----|-----|-------|

| Data to SCK Setup    | Tdc    | 2   |     | ns    |

| SCK to Data Hold     | Tdh    | 2   |     | ns    |

| CSN to Data Valid    | Tcsd   |     | 42  | ns    |

| SCK to Data Valid    | Tcd    |     | 58  | ns    |

| SCK Low Time         | Tcl    | 40  |     | ns    |

| SCK High Time        | Tch    | 40  |     | ns    |

| SCK Frequency        | Fsck   | 0   | 8   | MHz   |

| SCK Rise and Fall    | Tr,Tf  |     | 100 | ns    |

| CSN to SCK Setup     | Tcc    | 2   |     | ns    |

| SCK to CSN Hold      | Tcch   | 2   |     | ns    |

| CSN Inactive time    | Tcwh   | 50  |     | ns    |

| CSN to Output High Z | Tcdz   |     | 42  | ns    |

Table 10 SPI timing parameters ( $C_{Load} = 10 pF$ ).

# nRF24L01 Single Chip 2.4 GHz Radio Transceiver

# **MEMORY MAP**

All undefined bits in the table below are redundant. They will be read out as '0'.

| Address<br>(Hex) | Mnemonic                 | Bit | Reset<br>Value | Type       | Description                                                               |

|------------------|--------------------------|-----|----------------|------------|---------------------------------------------------------------------------|

|                  | T                        | 1   |                |            |                                                                           |

| 00               | CONFIG                   | _   |                |            | Configuration Register                                                    |

|                  | Reserved                 | 7   | 0              | R/W        | Only '0' allowed                                                          |

|                  | MASK_RX_DR               | 6   | 0              | R/W        | Mask interrupt caused by RX_DR                                            |

|                  |                          |     |                |            | 1: Interrupt not reflected on the IRQ pin                                 |

|                  |                          |     |                |            | 0: Reflect RX_DR as active low interrupt                                  |

|                  | MACK TW DO               | -   | 0              | R/W        | on the IRQ pin                                                            |

|                  | MASK_TX_DS               | 5   | 0              | K/W        | Mask interrupt caused by TX_DS  1: Interrupt not reflected on the IRQ pin |

|                  |                          |     |                |            | 0: Reflect TX_DS as active low interrupt                                  |

|                  |                          |     |                |            | on the IRQ pin                                                            |

|                  | MASK_MAX_RT              | 4   | 0              | R/W        | Mask interrupt caused by MAX_RT                                           |

|                  | 1111 ISIL_1111 II L_111  |     | Ü              | 10 11      | 1: Interrupt not reflected on the IRQ pin                                 |

|                  |                          |     |                |            | 0: Reflect MAX_RT as active low                                           |

|                  |                          |     |                |            | interrupt on the IRQ pin                                                  |

|                  | EN_CRC                   | 3   | 1              | R/W        | Enable CRC. Forced high if one of the                                     |

|                  |                          |     |                |            | bits in the EN_AA is high                                                 |

|                  | CRCO                     | 2   | 0              | R/W        | CRC encoding scheme                                                       |

|                  |                          |     |                |            | '0' - 1 byte                                                              |

|                  |                          |     |                |            | '1' – 2 bytes                                                             |

|                  | PWR_UP                   | 1   | 0              | R/W        | 1: POWER UP, 0:POWER DOWN                                                 |

|                  | PRIM_RX                  | 0   | 0              | R/W        | 1: PRX, 0: PTX                                                            |

|                  |                          | 1   |                |            |                                                                           |

| 01               | EN_AA                    |     |                |            | Enable 'Auto Acknowledgment' Function                                     |

|                  | Enhanced                 |     |                |            | Disable this functionality to be                                          |

|                  | ShockBurst <sup>TM</sup> | 7.6 | 0.0            | D WY       | compatible with nRF2401, see page 26                                      |

|                  | Reserved                 | 7:6 | 00             | R/W        | Only '00' allowed                                                         |

|                  | ENAA_P5                  | 5   | 1              | R/W        | Enable auto ack. data pipe 5                                              |

|                  | ENAA_P4                  | 4   | 1              | R/W        | Enable auto ack. data pipe 4                                              |

|                  | ENAA_P3<br>ENAA_P2       | 2   | 1              | R/W<br>R/W | Enable auto ack. data pipe 3 Enable auto ack. data pipe 2                 |

|                  | ENAA_P2<br>ENAA_P1       | 1   | 1              | R/W        | * *                                                                       |

|                  | ENAA_P1<br>ENAA P0       | 0   | 1              | R/W        | Enable auto ack. data pipe 1 Enable auto ack. data pipe 0                 |

|                  | ENAA_FU                  | U   | 1              | IX/W       | Enable auto ack. data pipe o                                              |

| 02               | EN_RXADDR                |     |                |            | Enabled RX Addresses                                                      |

| 02               | Reserved                 | 7:6 | 00             | R/W        | Only '00' allowed                                                         |

|                  | ERX_P5                   | 5   | 0              | R/W        | Enable data pipe 5.                                                       |

|                  | ERX_P4                   | 4   | 0              | R/W        | Enable data pipe 4.                                                       |

|                  | ERX_P3                   | 3   | 0              | R/W        | Enable data pipe 3.                                                       |

|                  | ERX_P2                   | 2   | 0              | R/W        | Enable data pipe 2.                                                       |

|                  | ERX_P1                   | 1   | 1              | R/W        | Enable data pipe 1.                                                       |

|                  | ERX_P0                   | 0   | 1              | R/W        | Enable data pipe 0.                                                       |

|                  | -                        |     |                | •          |                                                                           |

| 03               | SETUP_AW                 |     |                |            | Setup of Address Widths                                                   |

|                  |                          |     |                |            | (common for all data pipes)                                               |

|                  | Reserved                 | 7:2 | 000000         | R/W        | Only '000000' allowed                                                     |

|                  | AW                       | 1:0 | 11             | R/W        | RX/TX Address field width                                                 |

|                  |                          |     |                |            | '00' - Illegal                                                            |

|                  |                          |     |                |            | '01' - 3 bytes                                                            |

|                  |                          |     |                |            | '10' - 4 bytes                                                            |

|                  |                          |     |                |            | '11' – 5 bytes                                                            |

|                  |                          |     |                |            | LSByte will be used if address width                                      |

|                  |                          |     |                |            | below 5 bytes                                                             |

| 04               | CETID DETD               |     |                |            | Satur of Automatic Datranamicsion                                         |

| 04               | SETUP_RETR<br>ARD        | 7:4 | 0000           | R/W        | Setup of Automatic Retransmission Auto Re-transmit Delay                  |

|                  | AIND                     | /.4 | 0000           | 10/ 00     | '0000' – Wait 250+86uS                                                    |

|                  | 1                        |     |                |            | 0000 - Walt 230+0003                                                      |

| (Hex) Value             |                                                                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | '0001' – Wait 500+86uS<br>'0010' – Wait 750+86uS                                                                                                                    |

|                         | '1111' – Wait 4000+86uS<br>(Delay defined from end of transmission<br>to start of next transmission) <sup>14</sup>                                                  |

| ARC 3:0 0011 R/W A      | Auto Retransmit Count '0000' –Re-Transmit disabled '0001' – Up to 1 Re-Transmit on fail of AA '1111' – Up to 15 Re-Transmit on fail of AA                           |

| OF DE CH                | DE Charact                                                                                                                                                          |

|                         | RF Channel                                                                                                                                                          |

| RF_CH 6:0 0000010 R/W S | Only '0' allowed Sets the frequency channel nRF24L01 operates on                                                                                                    |

| O( DE CEMIN             | DEG . D                                                                                                                                                             |

|                         | RF Setup Register                                                                                                                                                   |

|                         | Only '000' allowed Force PLL lock signal. Only used in test                                                                                                         |

|                         | Data Rate                                                                                                                                                           |

| RF_DR   3   1   R/W   I | '0' – 1 Mbps '1' – 2 Mbps                                                                                                                                           |

| RF_PWR 2:1 11 R/W S     | Set RF output power in TX mode  '00'18 dBm  '01'12 dBm  '10'6 dBm  '11' - 0 dBm                                                                                     |

| LNA_HCURR 0 1 R/W S     | Setup LNA gain                                                                                                                                                      |

|                         |                                                                                                                                                                     |

| i                       | Status Register (In parallel to the SPI instruction word applied on the MOSI pin, the STATUS register is shifted serially out on the MISO pin)                      |

|                         | Only '0' allowed                                                                                                                                                    |

| v                       | Data Ready RX FIFO interrupt. Set high when new data arrives RX FIFO <sup>15</sup> .  Write 1 to clear bit.                                                         |

| i. v                    | Data Sent TX FIFO interrupt. Set high when packet sent on TX. If AUTO_ACK is activated, this bit will be set high only when ACK is received.  Write 1 to clear bit. |

| MAX_RT 4 0 R/W N        | Maximum number of TX retries interrupt Write 1 to clear bit. If MAX_RT is set it must be cleared to enable further communication.                                   |

|                         | Data pipe number for the payload                                                                                                                                    |

<sup>&</sup>lt;sup>14</sup> Accurate formula for delay from start of transmission, to start of re-transmission:

TRD (us) = 250us \* (ARD+1) + 4us \*(AW + PW + CRCW) +138,5us.

TRD= total retransmit delay, AW=Address Width (#bytes), PW=Payload Width(#bytes)

<sup>,</sup> CRCW= CRC Width (#bytes)

15 The Data Ready interrupt is set by a new packet arrival event. The procedure for handling this interrupt should be: 1) read payload via SPI, 2) clear RX\_DR interrupt, 3) read FIFO\_STATUS to check if there are more payloads available in RX FIFO, 4) if there are more data in RX FIFO, repeat from 1).

| Address<br>(Hex) | Mnemonic       | Bit  | Reset<br>Value                        | Type | Description                                                                                                                                                                                                                       |

|------------------|----------------|------|---------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                |      |                                       |      | available for reading from RX_FIFO 000-101: Data Pipe Number 110: Not Used 111: RX FIFO Empty                                                                                                                                     |

|                  | TX_FULL        | 0    | 0                                     | R    | TX FIFO full flag. 1: TX FIFO full. 0:<br>Available locations in TX FIFO.                                                                                                                                                         |

| 08               | OBSERVE_TX     |      |                                       |      | Transmit observe register                                                                                                                                                                                                         |

| 00               | PLOS_CNT       | 7:4  | 0                                     | R    | Count lost packets. The counter is overflow protected to 15, and discontinue at max until reset. The counter is reset by writing to RF_CH. See page 14 and 17.                                                                    |

|                  | ARC_CNT        | 3:0  | 0                                     | R    | Count resent packets. The counter is reset when transmission of a new packet starts. See page 14.                                                                                                                                 |

| 00               | CD             |      |                                       |      |                                                                                                                                                                                                                                   |

| 09               | CD<br>Reserved | 7:1  | 000000                                | R    |                                                                                                                                                                                                                                   |

|                  | CD             | 0    | 0                                     | R    | Carrier Detect. See page 17.                                                                                                                                                                                                      |

|                  |                |      | , , , , , , , , , , , , , , , , , , , |      |                                                                                                                                                                                                                                   |

| 0A               | RX_ADDR_P0     | 39:0 | 0xE7E7E7E7E7                          | R/W  | Receive address data pipe 0. 5 Bytes maximum length. (LSByte is written first. Write the number of bytes defined by SETUP_AW)                                                                                                     |

| 0B               | RX_ADDR_P1     | 39:0 | 0xC2C2C2C2C2                          | R/W  | Receive address data pipe 1. 5 Bytes maximum length. (LSByte is written first. Write the number of bytes defined by SETUP_AW)                                                                                                     |

| 0C               | RX_ADDR_P2     | 7:0  | 0xC3                                  | R/W  | Receive address data pipe 2. Only LSB. MSBytes will be equal to RX_ADDR_P1[39:8]                                                                                                                                                  |

| 0D               | RX_ADDR_P3     | 7:0  | 0xC4                                  | R/W  | Receive address data pipe 3. Only LSB. MSBytes will be equal to RX_ADDR_P1[39:8]                                                                                                                                                  |

| 0E               | RX_ADDR_P4     | 7:0  | 0xC5                                  | R/W  | Receive address data pipe 4. Only LSB. MSBytes will be equal to RX_ADDR_P1[39:8]                                                                                                                                                  |

| 0F               | RX_ADDR_P5     | 7:0  | 0xC6                                  | R/W  | Receive address data pipe 5. Only LSB. MSBytes will be equal to RX_ADDR_P1[39:8]                                                                                                                                                  |

| 10               | TX_ADDR        | 39:0 | 0xE7E7E7E7E7                          | R/W  | Transmit address. Used for a PTX device only. (LSByte is written first) Set RX_ADDR_P0 equal to this address to handle automatic acknowledge if this is a PTX device with Enhanced ShockBurst <sup>TM</sup> enabled. See page 14. |

| 11               | RX_PW_P0       |      |                                       |      |                                                                                                                                                                                                                                   |

| 11               | Reserved       | 7:6  | 00                                    | R/W  | Only '00' allowed                                                                                                                                                                                                                 |

|                  | RX_PW_P0       | 5:0  | 0                                     | R/W  | Number of bytes in RX payload in data pipe 0 (1 to 32 bytes).  0 Pipe not used  1 = 1 byte  32 = 32 bytes                                                                                                                         |

|                  | ı              |      | ı                                     |      | 1 02 02 03 000                                                                                                                                                                                                                    |

| 12               | RX_PW_P1       |      |                                       |      |                                                                                                                                                                                                                                   |

|                  | Reserved       | 7:6  | 00                                    | R/W  | Only '00' allowed                                                                                                                                                                                                                 |

|                  | RX_PW_P1       | 5:0  | 0                                     | R/W  | Number of bytes in RX payload in data pipe 1 (1 to 32 bytes).  0 Pipe not used                                                                                                                                                    |

| Address<br>(Hex) | Mnemonic             | Bit        | Reset<br>Value | Туре       | Description                                                                                                                                                                   |

|------------------|----------------------|------------|----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                      |            |                |            | 1 = 1 byte                                                                                                                                                                    |

|                  |                      |            |                |            | 32 = 32 bytes                                                                                                                                                                 |

| 13               | RX_PW_P2             |            |                |            |                                                                                                                                                                               |

| 13               | Reserved             | 7:6        | 00             | R/W        | Only '00' allowed                                                                                                                                                             |

|                  | RX_PW_P2             | 5:0        | 0              | R/W        | Number of bytes in RX payload in data                                                                                                                                         |

|                  |                      |            |                |            | pipe 2 (1 to 32 bytes). 0 Pipe not used 1 = 1 byte                                                                                                                            |

|                  |                      |            |                |            | 32 = 32 bytes                                                                                                                                                                 |

| 14               | RX_PW_P3             |            |                |            |                                                                                                                                                                               |

|                  | Reserved             | 7:6        | 00             | R/W        | Only '00' allowed                                                                                                                                                             |

|                  | RX_PW_P3             | 5:0        | 0              | R/W        | Number of bytes in RX payload in data                                                                                                                                         |

|                  |                      |            |                |            | pipe 3 (1 to 32 bytes).  0 Pipe not used  1 = 1 byte                                                                                                                          |

|                  |                      |            |                |            | 32 = 32  bytes                                                                                                                                                                |

| 15               | RX_PW_P4             |            |                |            |                                                                                                                                                                               |

| 13               | RX_PW_P4 Reserved    | 7:6        | 00             | R/W        | Only '00' allowed                                                                                                                                                             |

|                  | RX_PW_P4             | 5:0        | 0              | R/W        | Number of bytes in RX payload in data                                                                                                                                         |

|                  | 101_1 ,,_1 ,         | 3.0        | Ü              | 10,77      | pipe 4 (1 to 32 bytes).                                                                                                                                                       |

|                  |                      |            |                |            | 0 Pipe not used                                                                                                                                                               |

|                  |                      |            |                |            | $1 = \hat{1}$ byte                                                                                                                                                            |

|                  |                      |            |                |            | 32 = 32 bytes                                                                                                                                                                 |

|                  |                      |            |                |            | 22 52 6 jes                                                                                                                                                                   |

| 16               | RX_PW_P5             | 7.         |                | D 411      | 0.1.1001.11                                                                                                                                                                   |

|                  | Reserved<br>RX_PW_P5 | 7:6<br>5:0 | 00             | R/W<br>R/W | Only '00' allowed  Number of bytes in RX payload in data                                                                                                                      |

|                  | KA_FW_F3             | 3.0        | 0              | N/W        | pipe 5 (1 to 32 bytes).  0 Pipe not used  1 = 1 byte                                                                                                                          |

|                  |                      |            |                |            | 32 = 32 bytes                                                                                                                                                                 |

| 1.5              | EVEC COLUMN          |            |                |            |                                                                                                                                                                               |

| 17               | FIFO_STATUS          | 7          | 0              | D/W        | FIFO Status Register                                                                                                                                                          |

|                  | Reserved<br>TX_REUSE | 7          | 0              | R/W<br>R   | Only '0' allowed  Reuse last sent data packet if set high.                                                                                                                    |

|                  |                      | U          | Ü              | K          | The packet will be repeatedly resent as long as CE is high. TX_REUSE is set by the SPI instruction REUSE_TX_PL, and is reset by the SPI instructions W_TX_PAYLOAD or FLUSH TX |

|                  | TX_FULL              | 5          | 0              | R          | TX FIFO full flag. 1: TX FIFO full. 0: Available locations in TX FIFO.                                                                                                        |

|                  | TX_EMPTY             | 4          | 1              | R          | TX FIFO empty flag. 1: TX FIFO empty. 0: Data in TX FIFO.                                                                                                                     |

|                  | Reserved             | 3:2        | 00             | R/W        | Only '00' allowed                                                                                                                                                             |

|                  | RX_FULL              | 1          | 0              | R          | RX FIFO full flag. 1: RX FIFO full. 0:                                                                                                                                        |

|                  | DV EMDTY             | 0          | 1              | D          | Available locations in RX FIFO.                                                                                                                                               |

|                  | RX_EMPTY             | 0          | 1              | R          | RX FIFO empty flag. 1: RX FIFO empty. 0: Data in RX FIFO.                                                                                                                     |

| N/A              | TX_PLD               | 255:0      | X              | W          | Written by separate SPI command TX data payload register 1 - 32 bytes. This register is implemented as a FIFO with 3 levels. Used in TX mode only                             |

| N/A              | RX_PLD               | 255:0      | X              | R          | Written by separate SPI command<br>RX data payload register. 1 - 32 bytes.<br>This register is implemented as a FIFO                                                          |

#### nRF24L01 Single Chip 2.4 GHz Radio Transceiver

| Address<br>(Hex) | Mnemonic | Bit | Reset<br>Value | Type | Description                                             |

|------------------|----------|-----|----------------|------|---------------------------------------------------------|

|                  |          |     |                |      | with 3 levels. All receive channels share the same FIFO |

Table 11 Memory map of nRF24L01

## Configuration for compatibility with nRF24XX

How to setup nRF24L01 to receive from an nRF2401/nRF2402/nRF24E1/nRF24E2:

- Use same CRC configuration as the nRF2401/nRF2402/nRF24E1/nRF24E2 uses

- Set the PRIM\_RX bit to 1

- Disable auto acknowledgement on the data pipe that will be addressed

- Use the same address width as the PTX device

- Use the same frequency channel as the PTX device