# INTEGRATED CIRCUITS

PHILIPS

# HEF4069UB gates

### DESCRIPTION

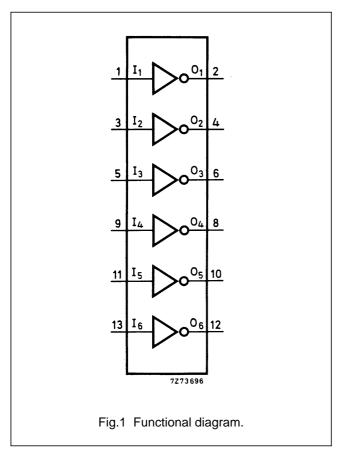

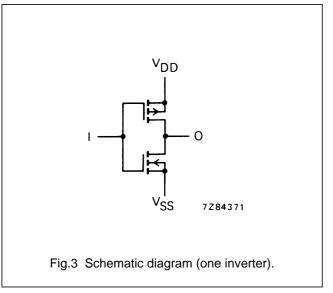

The HEF4069UB is a general purpose hex inverter. Each of the six inverters is a single stage.

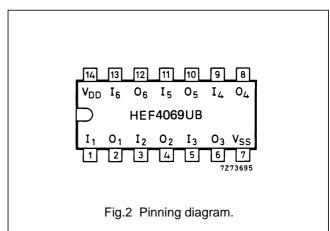

| HEF4069UBP(N):                       | 14-lead DIL; plastic          |  |  |  |

|--------------------------------------|-------------------------------|--|--|--|

|                                      | (SOT27-1)                     |  |  |  |

| HEF4069UBD(F):                       | 14-lead DIL; ceramic (cerdip) |  |  |  |

|                                      | (SOT73)                       |  |  |  |

| HEF4069UBT(D):                       | 14-lead SO; plastic           |  |  |  |

|                                      | (SOT108-1)                    |  |  |  |

| (): Package Designator North America |                               |  |  |  |

#### FAMILY DATA, I<sub>DD</sub> LIMITS category GATES

See Family Specifications for  $V_{IH}\!/V_{IL}$  unbuffered stages

### Product specification

# HEF4069UB gates

### AC CHARACTERISTICS

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                         | V <sub>DD</sub><br>V | SYMBOL           | TYP. | MAX.   | TYPICAL EXTRAPOLATION FORMULA       |

|-------------------------|----------------------|------------------|------|--------|-------------------------------------|

| Propagation delays      | 5                    |                  | 45   | 90 ns  | 18 ns + (0,55 ns/pF) C <sub>L</sub> |

| $I_n \to O_n$           | 10                   | t <sub>PHL</sub> | 20   | 40 ns  | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

| HIGH to LOW             | 15                   |                  | 15   | 25 ns  | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  | 40   | 80 ns  | 13 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> | 20   | 40 ns  | 9 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  | 15   | 30 ns  | 7 ns + (0,16 ns/pF) C <sub>L</sub>  |

| Output transition times | 5                    |                  | 60   | 120 ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| HIGH to LOW             | 10                   | t <sub>THL</sub> | 30   | 60 ns  | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  | 20   | 40 ns  | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  | 60   | 120 ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>  |

| LOW to HIGH             | 10                   | t <sub>TLH</sub> | 30   | 60 ns  | 9 ns + (0,42 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  | 20   | 40 ns  | 6 ns + (0,28 ns/pF) C <sub>L</sub>  |

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P ( $\mu$ W)                                                                            |                                   |

|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Dynamic power   | 5                    | $600 \text{ f}_{\text{i}} + \Sigma \text{ (f}_{\text{o}}\text{C}_{\text{L}}) \times \text{V}_{\text{DD}}^2$ | where                             |

| dissipation per | 10                   | $4~000~f_i + \Sigma~(f_oC_L) \times V_{DD}{}^2$                                                             | $f_i = input freq. (MHz)$         |

| package (P)     | 15                   | 22 000 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup>            | $f_o = output freq. (MHz)$        |

|                 |                      |                                                                                                             | $C_L$ = load capacitance (pF)     |

|                 |                      |                                                                                                             | $\sum (f_o C_L) = sum of outputs$ |

|                 |                      |                                                                                                             | $V_{DD}$ = supply voltage (V)     |

HEF4069UB

## Hex inverter

#### **APPLICATION INFORMATION**

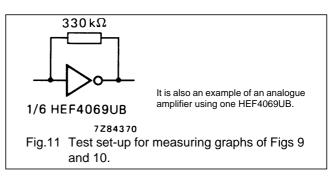

Some examples of applications for the HEF4069UB are shown below.

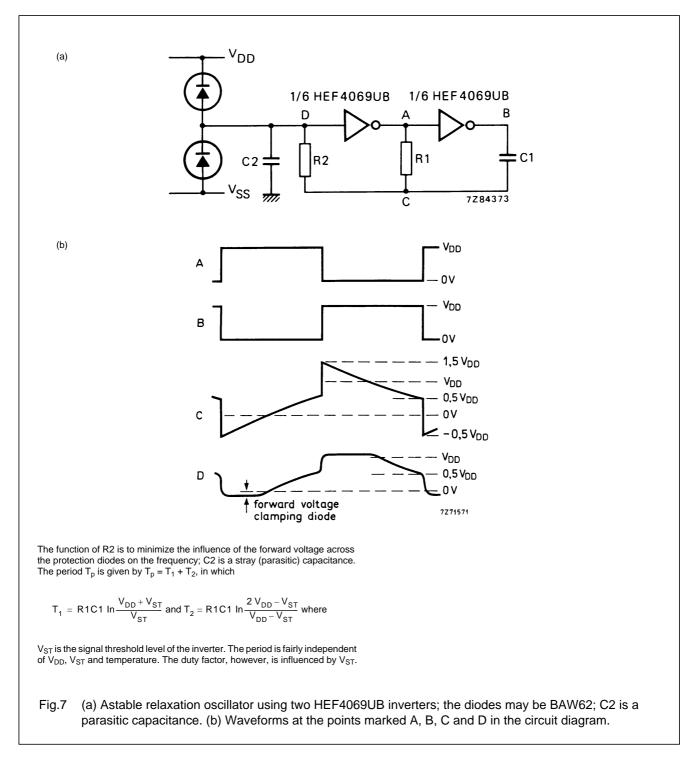

In Fig.7 an astable relaxation oscillator is given. The oscillation frequency is mainly determined by R1C1, provided R1 << R2 and R2C2 << R1C1.

# HEF4069UB gates

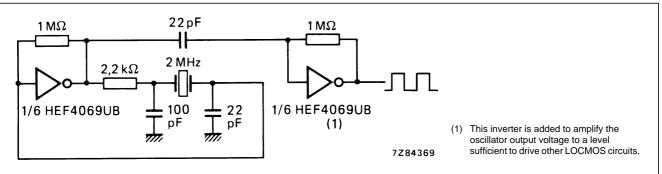

Fig.8 Crystal oscillator for frequencies up to 10 MHz, using two HEF4069UB inverters.

## HEF4069UB gates

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.