## Am29F400B Known Good Die

Data Sheet

July 2003

The following document specifies Spansion memory products that are now offered by both Advanced Micro Devices and Fujitsu. Although the document is marked with the name of the company that originally developed the specification, these products will be offered to customers of both AMD and Fujitsu.

## **Continuity of Specifications**

There is no change to this datasheet as a result of offering the device as a Spansion product. Any changes that have been made are the result of normal datasheet improvement and are noted in the document revision summary, where supported. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.

## **Continuity of Ordering Part Numbers**

AMD and Fujitsu continue to support existing part numbers beginning with "Am" and "MBM". To order these products, please use only the Ordering Part Numbers listed in this document.

## For More Information

Please contact your local AMD or Fujitsu sales office for additional information about Spansion memory solutions.

Publication Number 21258 Revision E Amendment +5 Issue Date June 27, 2001

#

## Am29F400B Known Good Die

## 4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS 5.0 Volt-only, Boot Sector Flash Memory—Die Revision 2

## **DISTINCTIVE CHARACTERISTICS**

### ■ Single power supply operation

- 5.0 volt-only operation for read, erase, and program operations

- Minimizes system level requirements

## ■ Manufactured on 0.32 µm process technology

Compatible with 0.5 µm Am29F400 device

## High performance

- Access time as fast as 70 ns

- Low power consumption (typical values at 5 MHz)

- 1 µA standby mode current

- 20 mA read current (byte mode)

- 28 mA read current (word mode)

- 30 mA program/erase current

## ■ Flexible sector architecture

- One 16 Kbyte, two 8 Kbyte, one 32 Kbyte, and seven 64 Kbyte sectors (byte mode)

- One 8 Kword, two 4 Kword, one 16 Kword, and seven 32 Kword sectors (word mode)

- Supports full chip erase

- Sector Protection features:

- A hardware method of locking a sector to prevent any program or erase operations within that sector

Sectors can be locked via programming equipment

Temporary Sector Unprotect feature allows code changes in previously locked sectors

## Top or bottom boot block configurations available

## Embedded Algorithms

- Embedded Erase algorithm automatically preprograms and erases the entire chip or any combination of designated sectors

- Embedded Program algorithm automatically writes and verifies data at specified addresses

- Minimum 1,000,000 write cycle per sector guaranteed

#### Compatibility with JEDEC standards

- Pinout and software compatible with singlepower-supply Flash

- Superior inadvertent write protection

#### Data# Polling and toggle bits

Provides a software method of detecting program or erase operation completion

#### Ready/Busy# pin (RY/BY#)

Provides a hardware method of detecting program or erase cycle completion

#### Erase Suspend/Erase Resume

Suspends an erase operation to read data from, or program data to, a sector that is not being erased, then resumes the erase operation

#### Hardware reset pin (RESET#)

- Hardware method to reset the device to reading array data

- 20-year data retention at 125°C

- Tested to datasheet specifications at temperature

- Contact AMD for higher temperature range devices

- Quality and reliability levels equivalent to standard packaged components

##

## **GENERAL DESCRIPTION**

The Am29F400B in Known Good Die (KGD) form is a 4 Mbit, 5.0 volt-only Flash memory. AMD defines KGD as standard product in die form, tested for functionality and speed. AMD KGD products have the same reliability and quality as AMD products in packaged form.

## Am29F400B Features

The Am29F400B is a 4 Mbit, 5.0 volt-only Flash memory organized as 524,288 bytes or 262,144 words. The word-wide data (x16) appears on DQ15–DQ0; the byte-wide (x8) data appears on DQ7–DQ0. This device is designed to be programmed in-system with the standard system 5.0 volt  $V_{CC}$  supply. A 12.0 V  $V_{PP}$  is not required for write or erase operations. The device can also be programmed in standard EPROM programmers.

This device is manufactured using AMD's  $0.32 \mu m$  process technology, and offers all the features and benefits of the Am29F400, which was manufactured using  $0.5 \mu m$  process technology.

To eliminate bus contention the device has separate chip enable (CE#), write enable (WE#) and output enable (OE#) controls.

The device requires only a **single 5.0 volt power sup-ply** for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations.

The device is entirely command set compatible with the **JEDEC single-power-supply Flash standard**. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-machine that controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from other Flash or EPROM devices.

Device programming occurs by executing the program command sequence. This initiates the **Embedded Program** algorithm—an internal algorithm that automatically times the program pulse widths and verifies proper cell margin.

Device erasure occurs by executing the erase command sequence. This initiates the **Embedded Erase** algorithm—an internal algorithm that automatically preprograms the array (if it is not already programmed) before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.

The host system can detect whether a program or erase operation is complete by observing the RY/BY# pin, or by reading the DQ7 (Data# Polling) and DQ6 (toggle) **status bits**. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.

The **sector erase architecture** allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully erased when shipped from the factory.

Hardware data protection measures include a low  $V_{CC}$  detector that automatically inhibits write operations during power transitions. The hardware sector protection feature disables both program and erase operations in any combination of the sectors of memory. This can be achieved via programming equipment.

The **Erase Suspend** feature enables the user to put erase on hold for any period of time to read data from, or program data to, any sector that is not selected for erasure. True background erase can thus be achieved.

The **hardware RESET# pin** terminates any operation in progress and resets the internal state machine to reading array data. The RESET# pin may be tied to the system reset circuitry. A system reset would thus also reset the device, enabling the system microprocessor to read the boot-up firmware from the Flash memory.

The system can place the device into the **standby mode**. Power consumption is greatly reduced in this mode.

AMD's Flash technology combines years of Flash memory manufacturing experience to produce the highest levels of quality, reliability and cost effectiveness. The device electrically erases all bits within a sector simultaneously via Fowler-Nordheim tunneling. The data is programmed using hot electron injection.

## **Electrical Specifications**

Refer to the Am29F400B data sheet, document number 21505, for full electrical specifications on the Am29F400B in KGD form.

## **PRODUCT SELECTOR GUIDE**

| Family Part Number                         |                                   |     | Am29F400B KGD |      |  |

|--------------------------------------------|-----------------------------------|-----|---------------|------|--|

| Speed Option                               | $V_{CC}$ = 5.0 V ± 5%             | -75 |               |      |  |

|                                            | $V_{CC} = 5.0 \text{ V} \pm 10\%$ |     | -90           | -120 |  |

| Max access time, ns (t <sub>ACC</sub> )    |                                   | 70  | 90            | 120  |  |

| Max CE# access time, ns (t <sub>CE</sub> ) |                                   | 70  | 90            | 120  |  |

| Max OE# access time, ns (t <sub>OE</sub> ) |                                   | 30  | 35            | 50   |  |

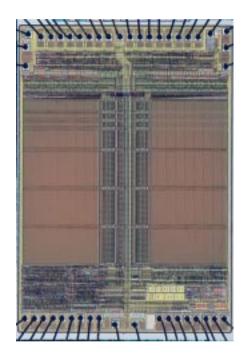

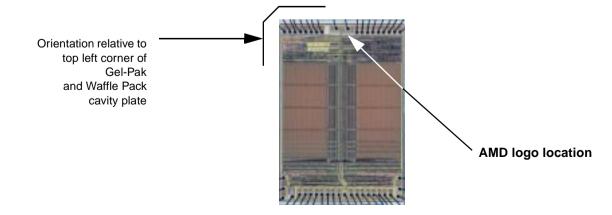

## **DIE PHOTOGRAPH**

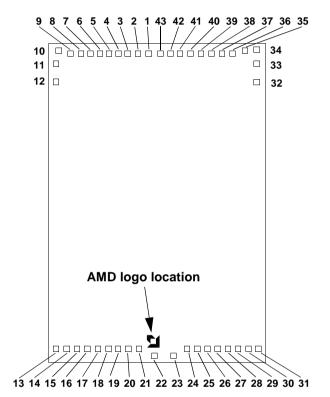

## **DIE PAD LOCATIONS**

Am29F400B Known Good Die

## PAD DESCRIPTION

| Ded | Circul          | Pad Ce | nter (mils) | Pad Center (millimeters) |         |

|-----|-----------------|--------|-------------|--------------------------|---------|

| Pad | Signal          | X      | Y           | X                        | Y       |

| 1   | V <sub>CC</sub> | 0.00   | 0.00        | 0.0000                   | 0.0000  |

| 2   | DQ4             | 6.87   | 0.00        | 0.1745                   | 0.0000  |

| 3   | DQ12            | 12.78  | 0.00        | 0.3246                   | 0.0000  |

| 4   | DQ5             | 18.62  | 0.00        | 0.4729                   | 0.0000  |

| 5   | DQ13            | 24.53  | 0.00        | 0.6231                   | 0.0000  |

| 6   | DQ6             | 30.37  | 0.00        | 0.7714                   | 0.0000  |

| 7   | DQ14            | 36.29  | 0.00        | 0.9218                   | 0.0000  |

| 8   | DQ7             | 42.12  | 0.00        | 1.0698                   | 0.0000  |

| 9   | DQ15/A-1        | 48.04  | 0.00        | 1.2202                   | 0.0000  |

| 10  | V <sub>SS</sub> | 55.68  | -1.35       | 1.4143                   | -0.0343 |

| 11  | BYTE#           | 57.48  | 6.50        | 1.4600                   | 0.1651  |

| 12  | A16             | 57.48  | 18.04       | 1.4600                   | 0.4582  |

| 13  | A15             | 57.13  | 172.01      | 1.4511                   | 4.3691  |

| 14  | A14             | 51.29  | 172.01      | 1.3028                   | 4.3691  |

| 15  | A13             | 45.87  | 172.01      | 1.1651                   | 4.3691  |

| 16  | A12             | 40.04  | 172.01      | 1.0170                   | 4.3691  |

| 17  | A11             | 34.61  | 172.01      | 0.8791                   | 4.3691  |

| 18  | A10             | 28.78  | 172.01      | 0.7310                   | 4.3691  |

| 19  | A9              | 23.36  | 171.76      | 0.5933                   | 4.3627  |

| 20  | A8              | 17.43  | 172.01      | 0.4427                   | 4.3691  |

| 21  | WE#             | 12.00  | 172.01      | 0.3048                   | 4.3691  |

| 22  | RESET#          | 2.42   | 175.78      | 0.0615                   | 4.4648  |

| 23  | RY/BY#          | -9.49  | 175.78      | -0.2411                  | 4.4648  |

| 24  | A17             | -24.48 | 172.01      | -0.6218                  | 4.3691  |

| 25  | A7              | -30.32 | 172.01      | -0.7701                  | 4.3691  |

| 26  | A6              | -35.74 | 172.01      | -0.9078                  | 4.3691  |

| 27  | A5              | -41.57 | 172.01      | -1.0559                  | 4.3691  |

| 28  | A4              | -47.00 | 172.01      | -1.1938                  | 4.3691  |

| 29  | A3              | -52.83 | 172.01      | -1.3419                  | 4.3691  |

| 30  | A2              | -58.25 | 172.01      | -1.4796                  | 4.3691  |

| 31  | A1              | -64.09 | 172.01      | -1.6279                  | 4.3691  |

| 32  | A0              | -64.44 | 18.04       | -1.6368                  | 0.4582  |

| 33  | CE#             | -64.44 | 6.50        | -1.6368                  | 0.1651  |

| 34  | V <sub>SS</sub> | -64.44 | -3.79       | -1.6368                  | -0.0962 |

| 35  | OE#             | -54.94 | -2.27       | -1.3955                  | -0.0576 |

| 36  | DQ0             | -47.36 | 0.00        | -1.2030                  | 0.0000  |

| 37  | DQ8             | -41.45 | 0.00        | -1.0528                  | 0.0000  |

| 38  | DQ1             | -35.61 | 0.00        | -0.9045                  | 0.0000  |

| 39  | DQ9             | -29.69 | 0.00        | -0.7541                  | 0.0000  |

| 40  | DQ2             | -23.86 | 0.00        | -0.6061                  | 0.0000  |

| 41  | DQ10            | -17.94 | 0.00        | -0.4557                  | 0.0000  |

| 42  | DQ3             | -12.11 | 0.00        | -0.3076                  | 0.0000  |

| 43  | DQ11            | -6.19  | 0.00        | -0.1572                  | 0.0000  |

*Note:* The coordinates above are relative to the center of pad 1 and can be used to operate wire bonding equipment.

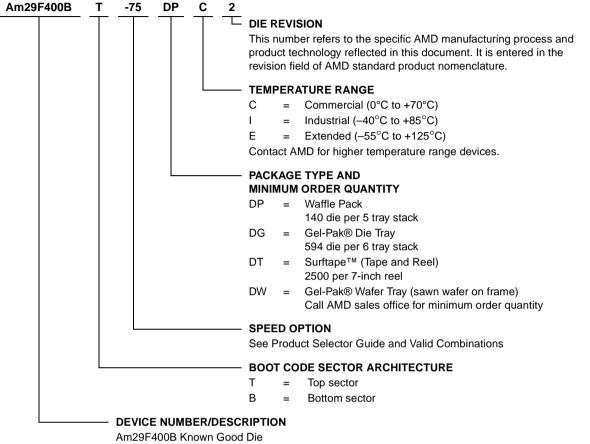

## **ORDERING INFORMATION**

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following:

4 Megabit (512 K x 8-Bit/256 K x 16-Bit) CMOS Flash Memory—Die Revision 2 5.0 Volt-only Program and Erase

| Valid C                          | combinations                                 |

|----------------------------------|----------------------------------------------|

| AM29F400BT-75<br>AM29F400BB-75   | DPC 2. DPI 2. DPE 2.                         |

| AM29F400BT-90<br>AM29F400BB-90   | DGC 2, DGI 2, DGE 2,<br>DTC 2, DTI 2, DTE 2, |

| AM29F400BT-120<br>AM29F400BB-120 | DWC 2, DWI 2, DWE 2                          |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

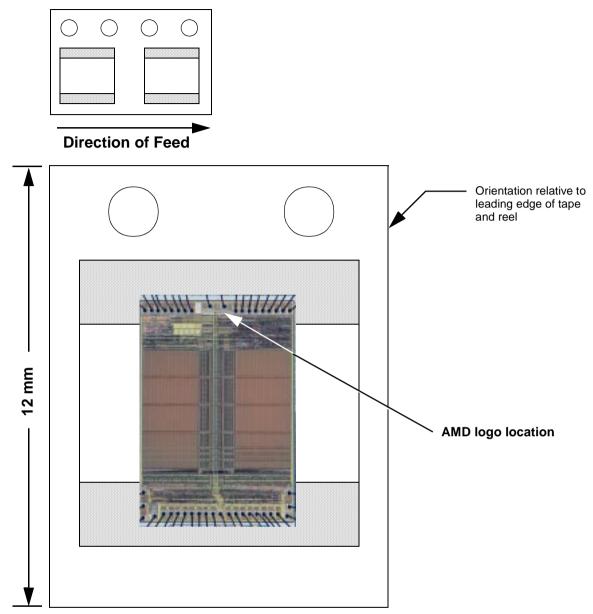

## **PACKAGING INFORMATION**

## Surftape Packaging

## Gel-Pak and Waffle Pack Packaging

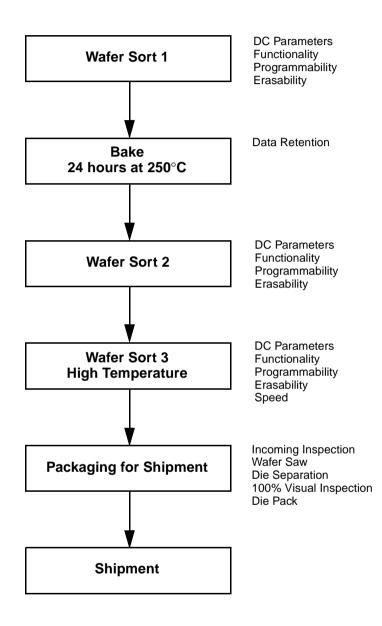

## **PRODUCT TEST FLOW**

Figure 1 provides an overview of AMD's Known Good Die test flow. For more detailed information, refer to the Am29F400B product qualification database supplement for KGD. AMD implements quality assurance procedures throughout the product test flow. In addition, an off-line quality monitoring program (QMP) further guarantees AMD quality standards are met on Known Good Die products. These QA procedures also allow AMD to produce KGD products without requiring or implementing burn-in.

Figure 1. AMD KGD Product Test Flow

## PHYSICAL SPECIFICATIONS

| Die Dimensions                                            |

|-----------------------------------------------------------|

| Die Thickness                                             |

|                                                           |

| Bond Pad Size 4.69 mils x 4.69 mils                       |

| 115.9 μm x 115.9 μm                                       |

| Pad Area Free of Passivation $\dots 13.98 \text{ mils}^2$ |

|                                                           |

| Pads Per Die43                                            |

| Bond Pad Metallization Al/Cu                              |

| Die Backside No metal,                                    |

| may be grounded (optional)                                |

| Passivation SiN/SOG/SiN                                   |

## **DC OPERATING CONDITIONS**

| V <sub>CC</sub> (Supply Voltage)   | .4.5 V to 5.5 V |

|------------------------------------|-----------------|

| Junction Temperature Under Bias T. | (max) = 130°C   |

Operating Temperature

| Commercial | 0°C to +70°C     |

|------------|------------------|

| Industrial | . −40°C to +85°C |

| Extended   | –55°C to +125°C  |

|            |                  |

Contact AMD for higher temperature range devices.

## MANUFACTURING INFORMATION

| ManufacturingFASL                            |

|----------------------------------------------|

| Test Sunnyvale, CA, USA,and Penang, Malaysia |

| Manufacturing ID (Top Boot)                  |

| Preparation for Shipment Penang, Malaysia    |

| Fabrication Process CS39S                    |

| Die Revision                                 |

## SPECIAL HANDLING INSTRUCTIONS

#### Processing

Do not expose KGD products to ultraviolet light or process them at temperatures greater than 250°C. Failure to adhere to these handling instructions will result in irreparable damage to the devices. For best yield, AMD recommends assembly in a Class 10K clean room with 30% to 60% relative humidity.

#### Storage

Store at a maximum temperature of 30°C in a nitrogenpurged cabinet or vacuum-sealed bag. Observe all standard ESD handling procedures.

## TERMS AND CONDITIONS OF SALE FOR AMD NON-VOLATILE MEMORY DIE

All transactions relating to unpackaged die under this agreement shall be subject to AMD's standard terms and conditions of sale, or any revisions thereof, which revisions AMD reserves the right to make at any time and from time to time. In the event of conflict between the provisions of AMD's standard terms and conditions of sale and this agreement, the terms of this agreement shall be controlling.

AMD warrants unpackaged die of its manufacture ("Known Good Die" or "Die") against defective materials or workmanship for a period of one (1) year from date of shipment. This warranty does not extend beyond the first purchaser of said Die. Buyer assumes full responsibility to ensure compliance with the appropriate handling, assembly and processing of Known Good Die (including but not limited to proper Die preparation, Die attach, wire bonding and related assembly and test activities), and compliance with all guidelines set forth in AMD's specifications for Known Good Die, and AMD assumes no responsibility for environmental effects on Known Good Die or for any activity of Buyer or a third party that damages the Die due to improper use, abuse, negligence, improper installation, accident, loss, damage in transit, or unauthorized repair or alteration by a person or entity other than AMD ("Warranty Exclusions").

The liability of AMD under this warranty is limited, at AMD's option, solely to repair the Die, to send replacement Die, or to make an appropriate credit adjustment or refund in an amount not to exceed the original purchase price actually paid for the Die returned to AMD, provided that: (a) AMD is promptly notified by Buyer in writing during the applicable warranty period of any defect or nonconformity in the Known Good Die; (b) Buyer obtains authorization from AMD to return the defective Die; (c) the defective Die is returned to AMD by Buyer in accordance with AMD's shipping instructions set forth below; and (d) Buyer shows to AMD's satisfaction that such alleged defect or nonconformity actually exists and was not caused by any of the abovereferenced Warranty Exclusions. Buyer shall ship such defective Die to AMD via AMD's carrier, collect. Risk of loss will transfer to AMD when the defective Die is provided to AMD's carrier. If Buyer fails to adhere to these warranty returns guidelines, Buyer shall assume all risk of loss and shall pay for all freight to AMD's specified location. The aforementioned provisions do not extend the original warranty period of any Known Good Die that has either been repaired or replaced by AMD.

WITHOUT LIMITING THE FOREGOING, EXCEPT TO THE EXTENT THAT AMD EXPRESSLY WARRANTS TO BUYER IN A SEPARATE AGREEMENT SIGNED BY AMD, AMD MAKES NO WARRANTY WITH RESPECT TO THE DIE'S PROCESSING OF DATE DATA, AND SHALL HAVE NO LIABILITY FOR DAMAGES OF ANY KIND, UNDER EQUITY, LAW, OR ANY OTHER THEORY, DUE TO THE FAILURE OF SUCH KNOWN GOOD DIE TO PROCESS ANY PAR-TICULAR DATA CONTAINING DATES, INCLUDING DATES IN AND AFTER THE YEAR 2000, WHETHER OR NOT AMD RECEIVED NOTICE OF THE POSSI-BILITY OF SUCH DAMAGES.

THIS WARRANTY IS EXPRESSED IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING THE IMPLIED WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE, THE IMPLIED WARRANTY OF MERCHANTABILITY AND OF ALL OTHER OBLIGATIONS OR LIABILITIES ON AMD's PART, AND IT NEITHER ASSUMES NOR AUTHO-RIZES ANY OTHER PERSON TO ASSUME FOR AMD ANY OTHER LIABILITIES. THE FOREGOING CONSTITUTES THE BUYER'S SOLE AND EXCLU-SIVE REMEDY FOR THE FURNISHING OF DEFEC-TIVE OR NON CONFORMING KNOWN GOOD DIE AND AMD SHALL NOT IN ANY EVENT BE LIABLE FOR INCREASED MANUFACTURING COSTS, DOWNTIME COSTS, DAMAGES RELATING TO BUYER'S PROCUREMENT OF SUBSTITUTE DIE (i.e., "COST OF COVER"), LOSS OF PROFITS, REV-ENUES OR GOODWILL, LOSS OF USE OF OR DAMAGE TO ANY ASSOCIATED EQUIPMENT, OR ANY OTHER INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES BY REASON OF THE FACT THAT SUCH KNOWN GOOD DIE SHALL HAVE BEEN DETERMINED TO BE DEFECTIVE OR NON CONFORMING.

Buyer agrees that it will make no warranty representations to its customers which exceed those given by AMD to Buyer unless and until Buyer shall agree to indemnify AMD in writing for any claims which exceed AMD's warranty.

Known Good Die are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of the Die can reasonably be expected to result in a personal injury. Buyer's use of Known Good Die for use in life support applications is at Buyer's own risk and Buyer agrees to fully indemnify AMD for any damages resulting in such use or sale.

## **REVISION SUMMARY**

## Revision A (May 1997)

Initial release.

## **Revision B (January 1998)**

Formatted to match current template. Updated Distinctive Characteristics and General Description sections using the current main data sheet. Updated for CS39 process technology.

## Revision B+1 (February 1998)

#### **Distinctive Characteristics**

The minimum guarantee per sector is now 1 million cycles.

## Global

Added -75 and -90 speed options.

#### **Pad Description**

Corrected coordinates for pads 2, 19, 22, 35, 40, and 42.

#### **Physical Specifications**

Changed die thickness specification to ~20 mils.

## Revision B+2 (May 1998)

#### **Die Pad Locations**

Moved AMD logo to above pad 23.

## **Revision C (June 1998)**

### **Distinctive Characteristics**

Changed "Manufactured on 0.35 µm process technology" to "Manufactured on 0.32 µm process technology".

#### **General Description**

*Third paragraph:* Changed "AMD's 0.35 µm process technology" to "AMD's 0.32 µm process technology".

#### **Die Photograph**

Replaced with photograph of Die Revision 2.

#### **Die Pad Locations**

Corrected the location of the AMD logo to above pad 22 from pad above pad 13. Modified figure to match new die photograph.

#### **Pad Description**

Replaced table with new pad coordinates.

#### **Physical Specifications**

Die Dimensions: Changed to 135 mils x 198 mils, 3.43 mm x 5.03 mm from 141.34 mils x 207.48 mils, 3.59 mm x 5.27 mm.

Die Thickness: Added ~500 µm.

Pad Area Free of Passivation: Changed to 20.85 mils<sup>2</sup> and 13,433  $\mu$ m<sup>2</sup> from 15.52 mils<sup>2</sup> and 10,000  $\mu$ m<sup>2</sup>.

Passivation: Changed to SiN/SOG/SiN from Nitride/SOG/Nitride.

### **Manufacturing Information**

*Manufacturing ID:* Changed to 98F02AK (top boot) and 98F02ABK (bottom boot) from 98965AK (top boot) and 98965ABK (bottom boot).

Fabrication Process: Changed to CS39S from CS39.

Die Revision: Changed to 2 from 1.

## Revision C+1 (September 1998)

### Page 5, Ordering Information

Package Type and Minimum Order Quantity: Changed Waffle Pack to 140 die per 5 tray stack from 180 die per 5 tray stack. Changed Gel-Pak<sup>®</sup> Die Tray to 594 die per 6 tray stack from 378 die per 6 tray stack. Changed Surftape<sup>™</sup> (Tape and Reel) to 2500 per 7-inch reel from 1800 per 7-inch reel.

#### Page 7, Physical Specifications

Die Dimensions: Changed to 3.42 mm x 5.02 mm from 3.43 mm x 5.03 mm.

Bond Pad Size: Changed to 4.7 mils x 4.7 mils and 119.7  $\mu m$  x 119.7  $\mu m$  from 3.74 mils x 3.74 mils and 95  $\mu m$  x 95  $\mu m.$

Pad Area Free of Passivation: Changed to 13.98 mils<sup>2</sup> and 9,025  $\mu$ m<sup>2</sup> from 20.85 mils<sup>2</sup> and 13,433  $\mu$ m<sup>2</sup>.

Bond Pad Metallization: Changed to Al/Cu from Al/Cu/Si.

#### Page 7, Manufacturing Information

*Manufacturing ID (Top Boot)*: Changed to 98F02AK from 98F02A.

## **Revision D (November 1998)**

#### Global

Revised document specifications for die shrink from 0.35  $\mu$ m to 0.32  $\mu$ m process technology.

#### **Terms and Conditions**

Replaced warranty with new version.

## **Revision E (December 1998)**

#### **Packaging Information**

Added section. Moved orientation information from die photograph section into this section.

## Revision E+1 (February 1999)

#### **Die Pad Locations**

Corrected top row of pad callouts.

## Revision E+2 (June 14, 1999)

## **Physical Specifications**

Corrected the bond pad dimensions.

## Revision E+3 (July 12, 1999)

### **Ordering Information**

Corrected the die revision indicated in the example and the valid combinations to 2.

## Revision E+4 (November 17, 1999)

## Distinctive Characteristics, Ordering Information, DC Operating Conditions

Added note to contact AMD for higher temperatrure range.

## Revision E+5 (June 27, 2001)

#### **Manufacturing Information**

Added Penang, Malaysia as a test facility (ACN2016).

#### Trademarks

Copyright © 2001 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are registered trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.