# HD63705V0, HD637A05V0, HD637B05V0 (Limiting Supplies.

(Limiting Supplies. For Development Only.)

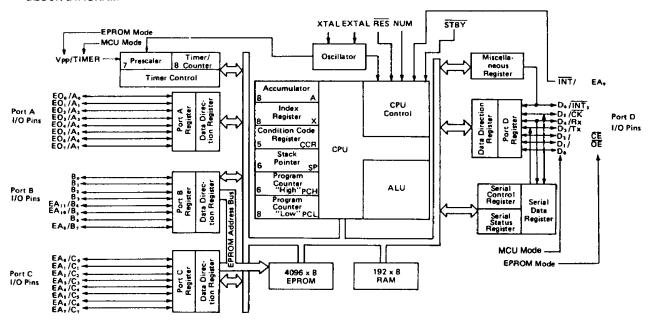

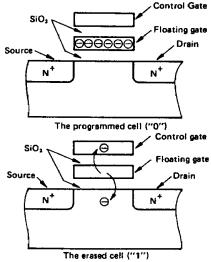

The HD63705V0 is an 8-bit CMOS single chip microcomputer unit (MCU) which includes 4k bytes of EPROM and is object code compatible with the HD6305V0.

This MCU contains a CPU, clock oscillator, 4k bytes of EPROM, 192 bytes of RAM, 31 parallel I/O pins, two timers and a serial communication interface (SCI).

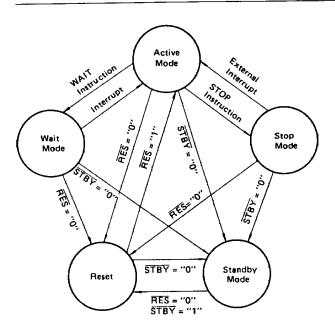

In addition to CMOS technology, it provides power saving STOP, WAIT and STANDBY modes, further reducing its already low power consumption.

The HD63705V0 is available in a hermetically sealed 40pin ceramic package with a glass window. This glass window allows for programming and EPROM erasure in the same sway as 27256 type EPROM.

#### **■ HARDWARE FEATURES**

- Pin compatible with HD6305V0 and HD6305UO

- 4096 bytes of EPROM

- 192 bytes of RAM

- 31 I/O terminals

- Two Timers

- a 8-bit timer with a 7-bit prescaler (software programmable prescaler; event counter)

- a 15-bit timer (capable of being used as the SCI clock divider)

- On-chip serial interface circuit (synchronized with clock)

- Six interrupts (two external, two timer, one serial and one software)

- Low power mode

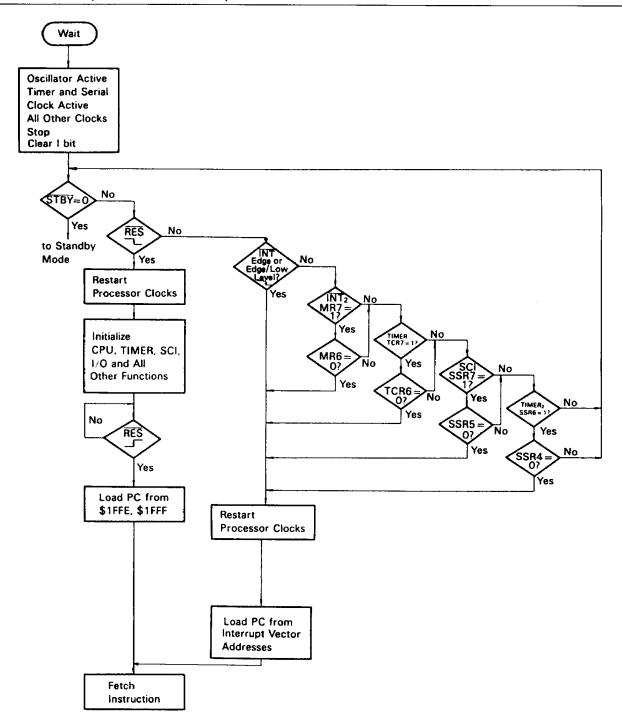

Wait mode . . . . Internal oscillator remains active. The CPU processing is halted. The timer, the SCI, and interrupts can function normally. The contents of all registers remain unchanged, except that I bit of

remain unchanged, except that I bit of the condition code register is cleared.

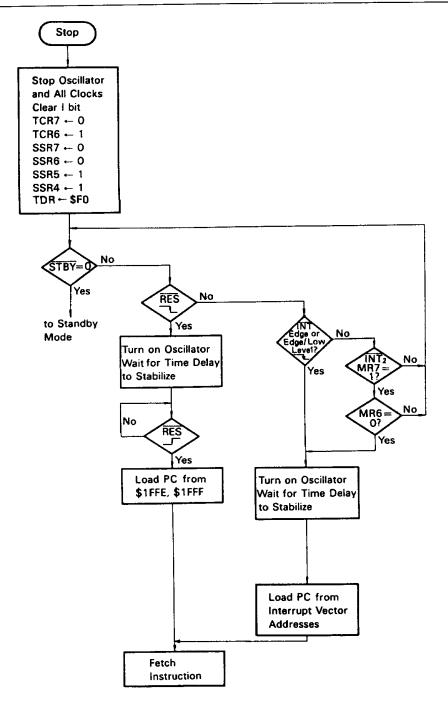

— Stop mode . . . . . . Internal oscillator is halted. RAM, I/O

terminals and all registers except I bit of the condition code register, bits 6 and 7 of the timer control register, and bits 4, 5, 6 and 7 of the SCI status regis-

ter remain unchanged.

Standby mode . . . . Internal oscillator is halted. The data of RAM is unchanged. The MCU internal

registers are reset.

Minimum instruction cycle time

HD63705V0 1μs (f = 1MHz) HD637A05V0 0.67μs (f = 1.5MHz)

$0.5\mu s (f = 2MHz)$

Wide operating range

HD637B05V0

HD63705V0  $f = 0.1 \sim 1 \text{MHz} \ (V_{CC} = 5V \pm 10\%)$ HD637A05V0  $f = 0.1 \sim 1 \text{MHz} \ (V_{CC} = 1.5V \pm 10\%)$ HD637B05V0  $f = 0.1 \sim 2 \text{MHz} \ (V_{CC} = 5V \pm 10\%)$

Operating modes . . . MCU mode

**EPROM** mode

#### **■ SOFTWARE FEATURES**

- Similar to the HD6800

- Byte efficient instruction set

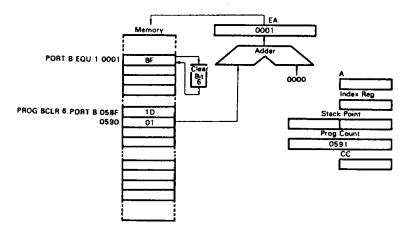

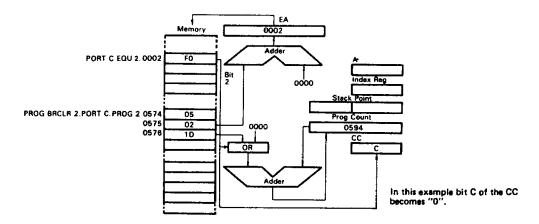

- Powerful bit manipulation instructions (Bit set, bit clear and bit test and branch are available for all RAM bits and all I/O terminals)

- Versatile interrupt handling

- Powerful indexed addressing for tables

- Full set of conditional branches

- 10 powerful addressing modes

- All addressing modes apply to ROM, RAM and I/O instructions

- 3 new instructions, STOP, WAIT and DDA, added to the HD6805 family instruction set

- Instruction set which is compatible with that of the HD6305V

#### PROGRAM DEVELOPMENT SUPPORT TOOLS

- Cross assembler software for use with IBM PC and compatibles

- In circuit emulator for use with IBM PCs and compatibles

- Programming socket adapter for programming the EPROM-on-chip device.

#### BLOCK DIAGRAM

(Precaution in Using a Single-Chip Microcomputer with EPROM)

- (1) If the MCU is exposed to strong light especially a fluorescent light or the sunlight, EPROM data may be erased or the MCU malfunctions is caused by photocurrent. Therefore, after programming, it is recommended to put a shielding label on the glass window in the applications which expose the LSI to ambient light.

- (2) Be careful not to rub the glass window with plastic or other materials that may generate electricity leading to malfunction of the LSI. Use conductive shielding labels that can distribute charge evenly.

#### **ABSOLUTE MAXIMUM RATING**

| ltem                | Symbol           | Value                        | Unit | Note |

|---------------------|------------------|------------------------------|------|------|

| Supply Voltage      | V <sub>cc</sub>  | <b>−0.3 ~ +7.0</b>           | v    |      |

| Programming Voltage | V <sub>PP</sub>  | <b>−0.3 ∼ +15.0</b>          | V    | 1    |

| Input Voltage       | V <sub>in</sub>  | $-0.3 \sim V_{\rm CC} + 0.3$ | V    | 2    |

| Operating Voltage   | T <sub>opr</sub> | 0 ~ +70                      | °C   |      |

| Storage Voltage     | T <sub>str</sub> | <b>-55</b> ∼ +125            | °C   |      |

(NOTE 1) Applies to TIMER/Vpp pin.

(NOTE 2) Applies to all other pins except for TIMER/Vpp.

#### (Precaution)

These devices contain circuits to protect the inputs against high static voltages or high electric fields. Be careful not to apply any voltage higher than the absolute maximum rating to these high input impedance circuits. For normal operation, we recommend the  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \le \{V_{in} \text{ or } V_{out}\} \le V_{CC}$ .

### ■ MCU MODE ELECTRICAL CHARACTERISTICS

◆ DC Characteristics (V<sub>CC</sub> = 5.0V ± 10%, V<sub>SS</sub> = GND, Ta = 0 ~ +70 °C, TIMER/V<sub>PP</sub> = GND ~ V<sub>CC</sub>, unless otherwise noted)

| ltem                   |                                                                            | Symbol           | Test<br>Condition                                | min                  | typ | max                  | unit |

|------------------------|----------------------------------------------------------------------------|------------------|--------------------------------------------------|----------------------|-----|----------------------|------|

|                        | RES, STBY                                                                  |                  |                                                  | V <sub>cc</sub> -0.5 |     | V <sub>cc</sub> +0.3 |      |

| Input "High" Voltage   |                                                                            | ViH              |                                                  | V <sub>CC</sub> ×0.7 |     | V <sub>cc</sub> +0.3 | V    |

| ,                      | All Others                                                                 |                  |                                                  | 2.0                  |     | V <sub>cc</sub> +0.3 |      |

| Input "Low" Voltage    | All Inputs                                                                 | ViL              |                                                  | -0.3                 |     | 0.8                  | V    |

| Input Leakage          | TIMER/V <sub>PP</sub>                                                      | 1. 1             |                                                  | -                    | 1   | 100                  |      |

| Current                | INT, STBY                                                                  | 1112             |                                                  | _                    |     | 1.0                  | μΑ   |

| Three State<br>Current | $A_0 \sim A_7$ ,<br>$B_0 \sim B_7$ ,<br>$C_0 \sim C_7$ ,<br>$D_0 \sim D_6$ | I <sub>TSI</sub> | V <sub>in</sub> = 0.5 ∼<br>V <sub>CC</sub> −0.5V | _                    | _   | 1.0                  |      |

|                        | Operating                                                                  |                  |                                                  | - }                  | 5   | 10                   | mA   |

|                        | Wait                                                                       |                  |                                                  | _                    | 2   | 5                    | mA   |

| Current Dissipation*** | Stop                                                                       | Icc              | f = 1MHz*                                        | -                    | 2   | 10                   | μΑ   |

|                        | Standby                                                                    |                  |                                                  | _                    | 2   | 10                   | μΑ   |

| Input capacitance      | TIMER/VPP                                                                  |                  | f = 1MHz,                                        | -                    |     | 100                  | pF   |

|                        | All Terminals<br>except<br>TIMER/V <sub>PP</sub>                           | C <sub>in</sub>  | V <sub>in</sub> = 0V                             | _                    | _   | 15                   | pF   |

<sup>\*</sup>The value at f = XMHz is given by  $I_{CC} = \{f = XMHz\} = I_{CC} \{f = 1 \text{ MHz}\} \times X$ \*\*At Standby Mode

• AC Characteristics ( $V_{CC}$  = 5.0V  $\pm$  10%,  $V_{SS}$  = GND, Ta = 0  $\sim$  +70°C, unless otherwise noted)

|                                        |                  | Test                              | н                        | D63705\ | /0  | HD                       | 637A05 | vo  | HE                       | 637B05 | V0  | Unit             |

|----------------------------------------|------------------|-----------------------------------|--------------------------|---------|-----|--------------------------|--------|-----|--------------------------|--------|-----|------------------|

| Item                                   | Symbol           | Condition                         | min                      | typ     | max | min                      | typ    | max | min                      | typ    | max | Onit             |

| Clock<br>Frequency                     | f <sub>cl</sub>  |                                   | 0.4                      | _       | 4   | 0.4                      | -      | 6   | 0.4                      | -      | 8   | MHz              |

| Cycle Time                             | t <sub>cyc</sub> |                                   | 1.0                      | _       | 10  | 0.666                    | _      | 10  | 0.5                      |        | 10  | μs               |

| INT<br>Pulse Width                     | t <sub>IWL</sub> |                                   | t <sub>cyc</sub><br>+250 | _       |     | t <sub>cyc</sub><br>+200 | _      | _   | t <sub>cyc</sub><br>+200 | _      | -   | ns               |

| INT <sub>2</sub> Pulse Width           | ₹wL2             |                                   | t <sub>cyc</sub><br>+250 |         | -   | t <sub>cyc</sub><br>+200 | _      | _   | † <sub>cyc</sub><br>+200 |        | _   | ns               |

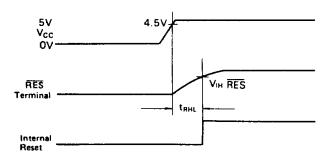

| RES<br>Pulse Width                     | t <sub>RWL</sub> |                                   | 5                        | _       | -   | 5                        | -      | _   | 5                        | _      | _   | t <sub>cyc</sub> |

| TIMER Pulse Width                      | t <sub>TWL</sub> |                                   | t <sub>cyc</sub><br>+250 | -       | -   | t <sub>eye</sub><br>+200 | _      | _   | t <sub>cyc</sub><br>+200 | _      | -   | ns               |

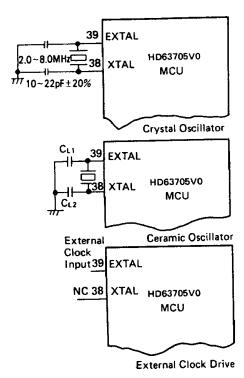

| Oscillation<br>Start Time<br>(Crystal) | tosc             | CL=22pF 20%<br>Rs = 60Ω max       | _                        |         | 20  | _                        | _      | 20  |                          | _      | 20  | ms               |

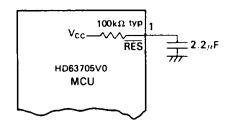

| Reset<br>Delay Time                    | t <sub>RHL</sub> | external<br>capacitance<br>2.2 μF | 80                       | _       | _   | 80                       | _      | -   | 80                       | _      | _   | m                |

<sup>\*\*\*</sup>V<sub>IH</sub> min. = V<sub>CC</sub>-1.0V, V<sub>IL</sub>max. = 0.8V, Penetrate current is not included.

### • Port Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND, Ta = 0 $\sim$ +70, unless otherwise noted)

| item                  |                 | Symbol          | Test Condition                                   | min                 | typ | max                  | Unit |

|-----------------------|-----------------|-----------------|--------------------------------------------------|---------------------|-----|----------------------|------|

| Output "High" Voltage |                 | VoH             | I <sub>OH</sub> = -200μA                         | 2.4                 | _   | -                    | ٧    |

| Cocput Ingil Voltage  | Port A, B, C, D | 1 *0#           | l <sub>OH</sub> = -10μA                          | V <sub>CC</sub> 0.7 | _   | _                    | ٧    |

| Output "Low" Voltage  |                 | VoL             | l <sub>OL</sub> = 1.6mA                          | - 1                 | -   | 0.55                 | ٧    |

| Input "High" Voltage  |                 | V <sub>IH</sub> |                                                  | 2.0                 | _   | V <sub>cc</sub> +0.3 | ٧    |

| Input "Low" Voltage   |                 | VIL             |                                                  | -0.3                | -   | 0.8                  | ٧    |

| Input Leakage Current | Port A, B, C, D | 114             | V <sub>in</sub> = 0.5 ~<br>V <sub>CC</sub> -0.5V | -                   | _   | 1                    | μА   |

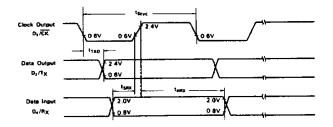

# • SCI Timing ( $V_{CC}$ = 5.0V $\pm$ 10%, $V_{SS}$ = GND, Ta = 0 $\sim$ +70°C, unless otherwise noted)

|                           |                   | Test<br>Condition | Н   | HD63705V0 |       | HD637A05V0 |     |       | HD637B05∨0 |     |       | Unit |

|---------------------------|-------------------|-------------------|-----|-----------|-------|------------|-----|-------|------------|-----|-------|------|

| ltem                      | Symbol            |                   | min | typ       | max   | min        | typ | max   | min        | typ | max   | Unit |

| Clock Cycle<br>Time       | t <sub>Scyc</sub> |                   | 1   | _         | 32768 | 0.67       | -   | 21845 | 0.5        |     | 16384 | μς   |

| Data Output<br>Delay Time | t <sub>TXD</sub>  | Fig. 1            | -   | _         | 250   | 1          | -   | 250   | -          | _   | 250   | ns   |

| Data Set-up<br>Time       | t <sub>sax</sub>  | Fig. 2            | 200 |           | -     | 200        | _   | _     | 200        | -   | _     | ns   |

| Data Hold<br>Time         | t <sub>HRX</sub>  |                   | 100 | -         | _     | 100        | -   | _     | 100        | -   | _     | ns   |

| Deta | Input | Deta

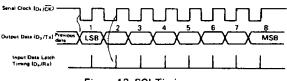

Figure 1 SCI Timing (Internal Clock)

Figure 2 SCI Timing (External Clock)

### ■ EPROM MODE ELECTRICAL CHARACTERISTICS

#### ■ PROGRAM OPERATION

• DC Characteristics ( $V_{CC}$  = 6V ± 0.25V,  $V_{PP}$  = 12.5V ± 0.3V, Ta = 25°C ± 5°C)

| ltem                          | Symbol          | Test Condition                | min  | typ | max                  | Unit |

|-------------------------------|-----------------|-------------------------------|------|-----|----------------------|------|

| Input Leakage Current         | I <sub>L1</sub> | V <sub>IN</sub> = 6.25V/0.45V | -    | _   | 2                    | μА   |

| Output Voltage                | V <sub>OL</sub> | l <sub>OL</sub> = 2.1mA       | _    | -   | 0.45                 | ٧    |

|                               | V <sub>OH</sub> | I <sub>OH</sub> =400μA        | 2.4  |     | -                    | ٧    |

| Power Supply Current (Active) | Ícc             |                               | _    | _   | 30                   | mA   |

|                               | VIL             |                               | -0.1 | _   | 0.8                  | ٧    |

| Input Voitage                 | VIH             |                               | 2.2  |     | V <sub>CC</sub> +0.3 | ٧    |

| Programming Current           | lpp             | CE = VIL                      | _    | _   | 40                   | mA   |

(Note) 1. Vpp (+12.5V) must be applied after VCC (6V) is settled and must be removed before VCC.

- 2. Vpp must not exceed + 15V. Be careful to prevent overshoot of the Vpp when switching to 12.5V.

- 3. The device must not be inserted into a board with Vpp at 12.5V to prevent damage to the reliability of the device.

- 4. When CE=VIL, Vpp must not be changed from VCC ~ 12.5V or from 12.5V ~ VCC-

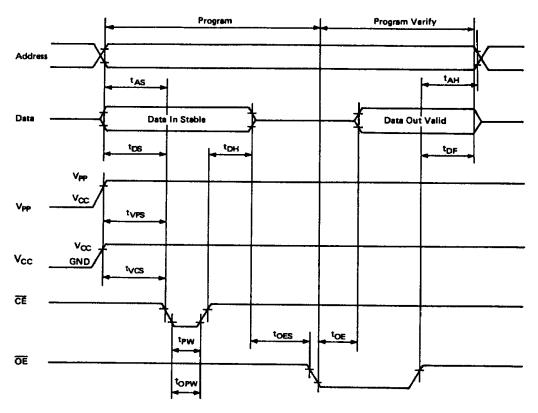

# • AC Characteristics ( $V_{CC}$ = 6V $\pm$ 0.25V, $V_{PP}$ = 12.5V $\pm$ 0.3V, Ta = 25°C $\pm$ 5°C)

| Item                           | Symbol            | <b>Test Condition</b> | min  | typ | max   | Unit |

|--------------------------------|-------------------|-----------------------|------|-----|-------|------|

| Address Set-up Time            | tas               | <del></del>           | 2    | -   | 1     | μs   |

| OE Set-up Time                 | toes              |                       | 2    | _   | -     | μs   |

| Data Set-up Time               | t <sub>DS</sub>   |                       | 2    | _   | _     | μs   |

| Address Hold Time              | t <sub>AH</sub>   |                       | 0    |     | -     | μς   |

| Data Hold Time                 | T <sub>DH</sub>   |                       | 2    | -   | -     | μs   |

| Output Disable Delay Time      | t <sub>DF</sub> * |                       | 0    |     | 130   | ns   |

| V <sub>PP</sub> Set-up Time    | t <sub>VPS</sub>  |                       | 2    | _   | _     | μs   |

| Program Pulse Width            | t <sub>PW</sub>   |                       | 0.95 | 1.0 | 1.05  | ms   |

| V <sub>CC</sub> Set-up Time    | tvcs              |                       | 2    | -   | -     | μs   |

| OE Output Delay Time           | tos               |                       | 0    |     | 500   | ns   |

| Overprogramming CE Pulse Width | topw              |                       | 2.85 | _   | 78.75 | ms   |

tDF is defined when any lines are not connected to output and the output level can not be referred.

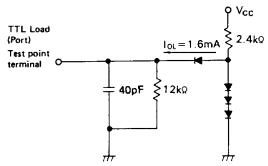

### Switching Characteristics

Test Condition Input pulse level . . . . 0.8V ~ 2.2V

Input rise/fall time . . . .  $\leq$  20 ns I/O timing reference level . . . . input output 0.8V, 2V

Figure 3 EPROM Program/Verify Timing

Figure 4 Not Applicable to this Product Line.

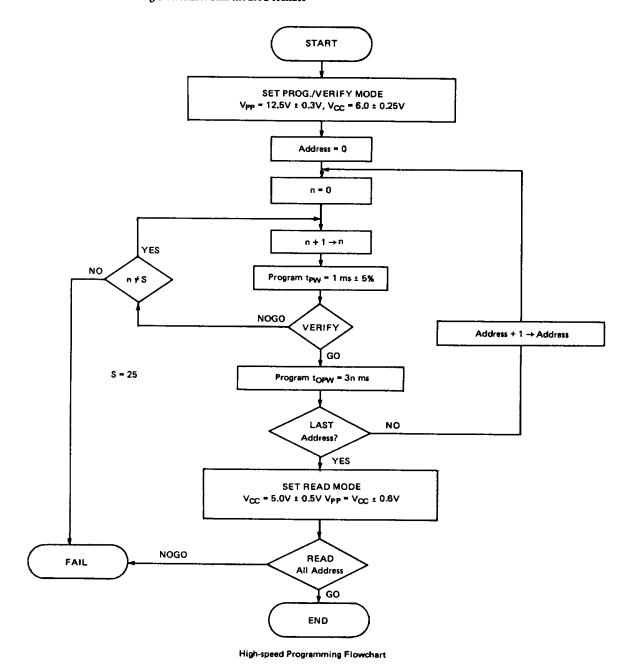

### ■ HIGH-SPEED PROGRAMMING

The HD63705V0 is applied to the high-speed programming method shown in the following flowchart. This method realizes

faster programming without any voltage stress to the device nor deterioration in reliability of programmed data.

(NOTE) 1. The load capacitance includes stray capacitance caused by the probe, jig, etc.

2. All diodes are 1S2074 H .

Figure 5 Test Load

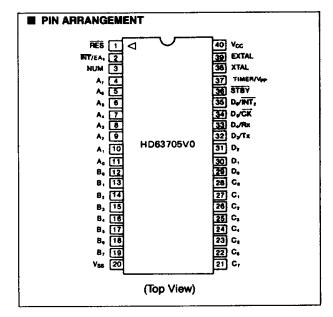

#### FUNCTIONAL PIN DESCRIPTION

The following paragraphs provide a brief description of HD63705V0 MCU input and output signals.

V<sub>CC</sub>, V<sub>SS</sub>

These are the power supply inputs.  $V_{CC} = 5.0V \pm 10\%$ ,  $V_{SS} = 0V$  (ground).

INT/EA<sub>9</sub>, INT₂

The MCU receives an external interrupt through these terminals. For details, see "INTERRUPT". The  $\overline{INT_2}$  is used as the Port D<sub>6</sub> pin. In the EPROM mode, the  $\overline{INT}$  is used as input of EA<sub>9</sub>.

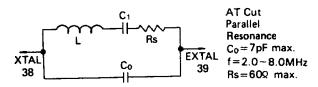

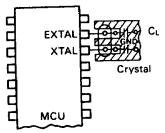

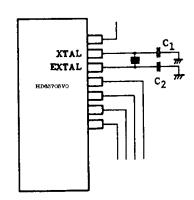

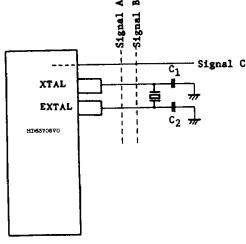

#### XTAL, EXTAL

These pins are inputs of the internal oscillator circuit. A crystal (AT cut,  $2.0 \sim 8.0$  MHz) or ceramic resonator is connected to these pins. Refer to "INTERNAL OSCILLATOR" for using these inputs.

#### . TIMER/VPP

This is an external input to control the internal timer circuit. See "TIMER" for details of the timer circuit.

In the EPROM mode, this pin is used when programming EPROM. The programming voltage  $V_{PP}$  is applied to this pin.

Once the voltage of 12.5V  $\pm$  0.3V is applied to this pin and  $\overline{CE}$  and  $\overline{OE}$  are set low and high respectively, data are written into EPROM through Port A (EO<sub>0</sub>  $\sim$  EO<sub>7</sub>). EPROM addresses are input through the Port C (EA<sub>0</sub>  $\sim$  EA<sub>7</sub>), Port B (EA<sub>8</sub>, EA<sub>10</sub>  $\sim$  EA<sub>11</sub>) and  $\overline{INT}$  (EA<sub>9</sub>).

#### • RES

This is used to reset the MCU. For details, see "RESET".

#### NUM

This is not for user applications. Connect this pin to the  $V_{SS}$  in the MCU mode and to the  $V_{CC}$  in the EPROM mode.

# • Input/output pins (A $_0 \sim A_7$ , B $_0 \sim B_7$ , C $_0 \sim C_7$ , D $_0 \sim D_6$ )

These 31 pins consist of three 8-bit I/O ports (A, B, C) and a 7-bit I/O port (D). Any pin may be programmed as an input or output by the state of the corresponding bit in the data direction register. The  $D_6$  is also used as the  $\overline{INT_2}$ . When using the  $D_6$  as a port, set the  $\overline{INT_2}$  interrupt mask bit in the miscellaneous register to "1" to prevent the  $\overline{INT_2}$  interrupt. For

details, see "INPUT/OUTPUT PORTS".

#### • STBY

This is used to put the MCU into the stand-by mode. Setting this pin to "low" level stops the internal oscillator and resets the MCU internal state. See "Stand-by Mode" for additional information.

The following are input/output pins for serial communication interface (SCI). These are used as  $D_3$ ,  $D_4$ , or  $D_5$ . For details, see "SERIAL COMMUNICATION INTERFACE".

#### • CK (D.)

This is used to input or output clocks when receiving or transmitting serial data.

#### R<sub>x</sub> (D<sub>4</sub>)

This is used to receive serial data.

#### T<sub>x</sub> (D<sub>3</sub>)

This is used to transmit serial data.

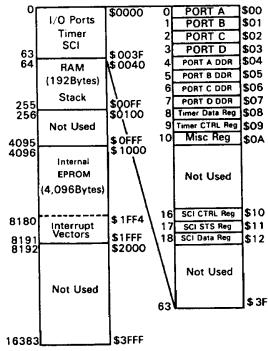

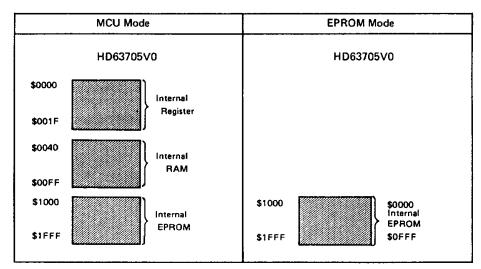

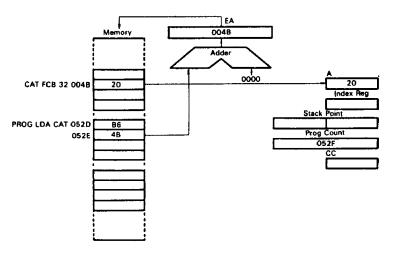

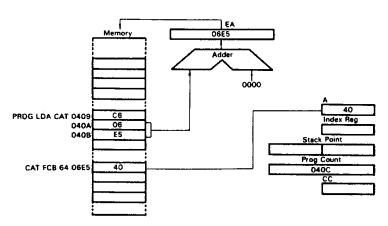

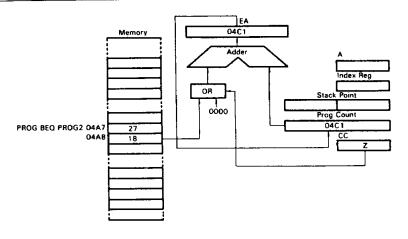

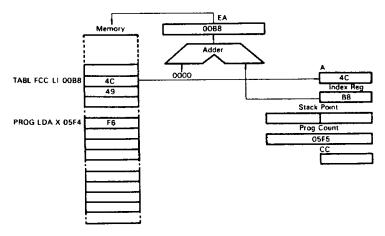

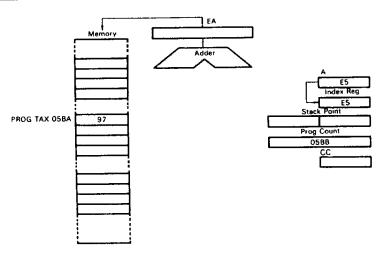

#### MEMORY MAP

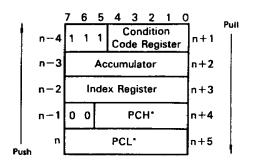

The memory map of the HD63705V0 MCU is shown in Fig. 6. During the processing of the interrupt, the register contents are pushed onto the stack in the order shown in Fig. 7. The stack pointer decrements. The low order byte (PCL) of the program counter is stacked first and the high order byte (PCH) of the program, the index register (X), the accumulator (A) and the condition code register (CCR) are stacked in that order. For subroutine calls, program counter (PCH, PCL) contents are pushed onto the stack.

Figure 6 HD63705V0 MCU Memory Map

\* For subroutine calls, only PCL and PCH are stacked.

Figure 7 Interrupt Stacking Order

#### **■ REGISTER**

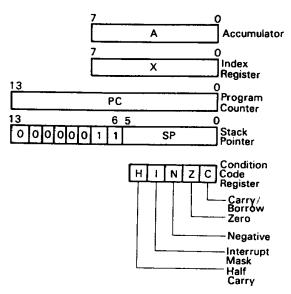

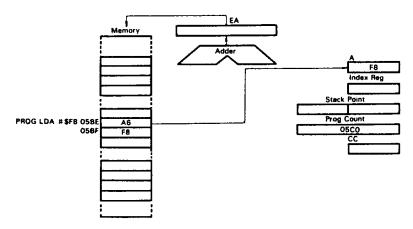

This CPU contains five registers available to the programmer. They are shown in Fig. 8.

#### Accumulator (A)

The accumulator is an 8-bit general purpose register which holds operands and results of the arithmetic operations or data manipulations.

#### Index Register (X)

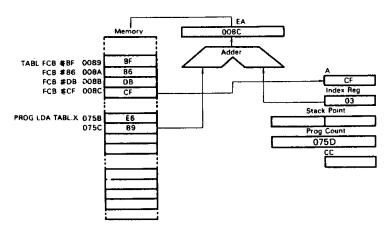

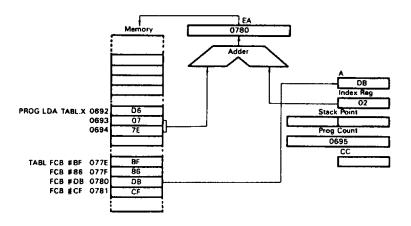

The index register is an 8-bit register used for the indexed addressing mode. It contains an 8-bit value which is added to an offset to create an effective address.

The index register can also be used for data manipulations with read-modify-write instructions.

When not performing addressing operations, the register can be used as a temporary storage area.

#### • Program Counter (PC)

The program counter is a 14-bit register which contains the address of the next instruction to be executed.

#### Stack Pointer (SP)

The stack pointer is a 14-bit register containing the address of the next free location of the stack. Initially, the stack pointer is set to location \$00FF. It is decremented as a data is pushed on to the stack and incremented as data is then poped out of the stack. The 8 high-order bits of the stack pointer are fixed to 00000011. During an MCU reset or a reset stack pointer (RSP) instruction, the pointer is set to location \$00FF. Subroutines and interrupts may be nested down to \$00C1, which allows programmers to use up to 31 levels of subroutine calls and 12 levels of interrupt responses.

#### • Condition Code Register (CCR)

The condition code register is a 5-bit register indicating the results of the instruction just executed. These bits can be individually tested by conditional branch instructions. Each bit is described in the following paragraphs.

#### Half Carry (H)

When set, this bit indicates that a carry occurred between bit 3 and 4 during an arithmetic operation (ADD, ADC).

#### Interrupt (i)

Setting this bit masks all interrupts except for software ones. If an interrupt occurs while this bit is set, the interrupt is latch-

ed and is processed as soon as the interrupt bit(I) is cleared. (More precisely the interrupt enters the servicing routine after the instruction next to the CLI is executed.)

#### Negative (N)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation is negative. (Bit 7 in the result is a logical "1".)

#### Zero (Z)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation is zero.

#### Carry/Borrow (C)

When set, this bit indicates that a carry or borrow occurred during the last arithmetic operation. This bit is also affected by bit test and branch instructions, shifts and rotates.

Figure 8 Programming Model

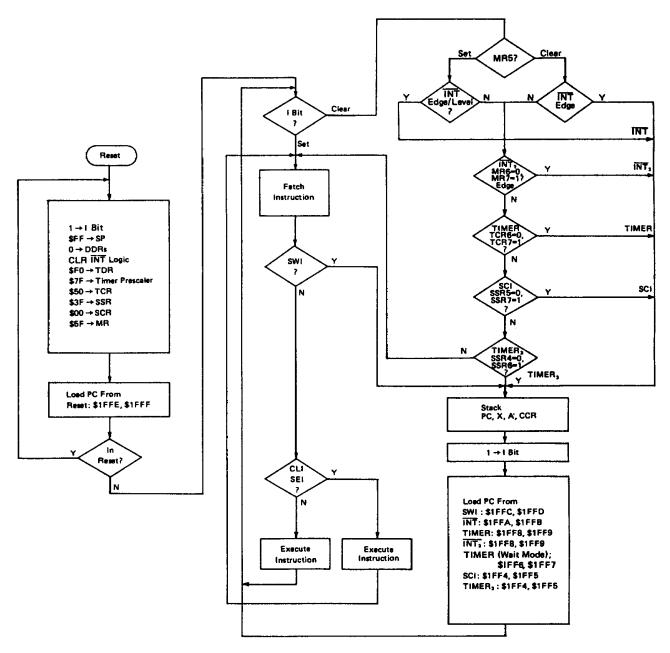

#### ■ INTERRUPTS

The HD63705V0 can be interrupted six different ways through the external interrupt input pins  $(\overline{INT}, \overline{INT_2})$ , the internal timer interrupts  $(TIMER, TIMER_2)$ , the serial interrupt (SCI) and the software interrupt instruction (SWI).

INT<sub>2</sub> and TIMER, and SCI and TIMER2 respectively generate the same vector address although a different vector address is generated for TIMER during the wait mode as shown in Table 1.

When any interrupt occurs, processing is suspended, the present CPU state pushed onto the stack, the interrupt bit (I) in the condition code register is set, the address of the interrupt service routine is obtained from the appropriate interrupt vector address, and the interrupt routine is executed. The RTI instruction causes the CPU to return to normal processing. This instruction unstacks the previous CPU state and allows the CPU to resume processing of the program from the next instruction to the interrupted one. Table 1 lists the execution priority of interrupts and the vector addresses.

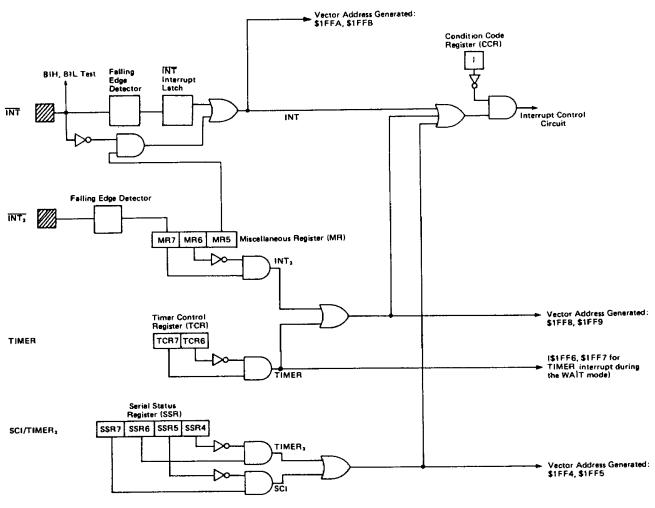

Fig. 9 shows a flowchart of the interrupt sequence. A diagram of the interrupt request source is shown in Fig. 10.

Either a level-sensitive and negative edge-sensitive trigger or negative edge-sensitive only trigger is available to the external interrupt  $\overline{INT}$ , depending on the state of bit 5 in the miscellaneous register. (Setting the bit selects level-sensitive and negative edge-sensitive trigger inputs and clearing it selects negative edge-sensitive only trigger inputs.) The  $\overline{INT}_2$  pin is an edge-sensitive trigger input. An interrupt request occurs on the negative edge of  $\overline{INT}_2$  and it is then latched. When a negative edge-sensitive trigger is used, the  $\overline{INT}$  interrupt request is automatically cleared as soon as a program jumps to the  $\overline{INT}$  service routine. The  $\overline{INT}_2$  interrupt request is cleared when "0" is written in bit 7 of the miscellaneous register.

Requests for external interrupts (INT, INT<sub>2</sub>), internal timer interrupts (TIMER, TIMER2) and serial interrupt (SCI) are held but not serviced while I bit of the condition code register is set. As soon as the I bit is cleared, the corresponding interrupts jumps to the interrupt service routines. The INT<sub>2</sub> interrupt can be masked by setting bit 6 of the miscellaneous register, the TIMER interrupt by bit 6 of the timer control register, the SCI interrupt by bit 5 of the serial status register and the TIMER<sub>2</sub> interrupt by bit 4 of the serial status register.

The state of the  $\overline{\text{INT}}$  pin is tested by BIL and BIH instructions. The  $\overline{\text{INT}}$  negative edge detect circuit and its latch circuit are independent of tests by these instructions. The state of  $\overline{\text{INT}}_2$  pins is also independent.

Table 1 Interrupt Execution Priority

| Interrupt              | Priority | Vector Address |

|------------------------|----------|----------------|

| RES                    | 1        | \$1FFE, \$1FFF |

| SWI                    | 2        | \$1FFC, \$1FFD |

| INT                    | 3        | \$1FFA, \$1FFB |

| TIMER/INT2             | 4        | \$1FF8, \$1FF9 |

| TIMER<br>(Wait Mode)   | 5        | \$1FF6, \$1FF7 |

| SCI/TIMER <sub>2</sub> | 6        | \$1FF4,\$1FF5  |

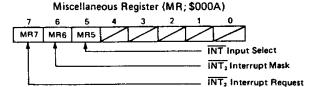

#### ■ MISCELLANEOUS REGISTER (MR: \$000A)

The miscellaneous register is used to determine whether a level-sensitive and negative edge-sensitive trigger or negative edge-sensitive only trigger is available to the external interrupt  $\overline{INT}$ . It is also used to control the  $\overline{INT_2}$  interrupt.

The bit 7 is the  $\overline{INT_2}$  interrupt request bit. This bit is set when a negative edge is detected on  $\overline{INT_2}$  pin. The  $\overline{INT_2}$  can be verified by software during the interrupt service routine (vector address: \$1FF8, \$1FF9). This bit must be cleared by software.

The bit 6 is the  $\overline{INT_2}$  interrupt mask bit. When set, this bit inhibits the  $\overline{INT_2}$  interrupt. Both read and write operations are available to the bit 7, but "1" can not be written into this bit by software. Thus, the  $\overline{INT_2}$  interrupt can not be requested by software.

At reset, the bit 7 is cleared, the bit 6 is set and the bit 5 is cleared.

Figure 9 Interrupt Flowchart

Figure 10 Interrupt Request Generation Circuitry

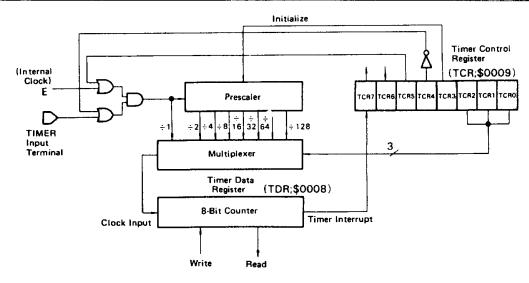

#### TIMER

Fig. 11 contains a block diagram of the MCU timer. The 8-bit counter may be loaded under program control and is decremented towards zero by the clock input. When the counter, that is, the timer data register (TDR) reaches zero, the timer interrupt request bit (bit 7) of the timer control register is set. When recognizing the interrupt request, the MCU proceeds to store the current CPU state on the stack, and then fetches the timer vector address from locations \$1FF8 and \$1FF9 (or \$1FF6 and \$1FF7 if in the wait mode) in order to execute the interrupt service routine. The timer interrupt can be masked by setting the interrupt mask bit (bit 6) of the timer control register. The mask bit (I) of the condition code register can also disable the timer interrupt.

The clock input to the timer can be from an external source applied to the TIMER input pin, or it can be the internal E signal (which is a clock obtained by dividing the oscillator clock by four). When the E signal is used as the source, it can be gated by an input applied to the TIMER pin.

The counter start counting down from "SFF" after it reaches zero. The counter may be monitored at any time by reading the contents of the timer data register. This allows a program to determine the length of the time since the occurrence of a timer

interrupt and does not disturb the counter contents.

At reset, the prescaler and counter are initialized to "\$7F" and "F0" respectively. The timer interrupt request bit (bit 7) is cleared and the timer interrupt request mask (bit 6) is set.

The timer interrupt request bit must be cleared by software.

| TCR7 | Timer Interrupt Request |

|------|-------------------------|

| 0    | Not Requested           |

| 1    | Requested               |

| TCR6 | Timer Interrupt Mask    |

|      |                         |

| 0    | Interrupt Allowed       |

Figure 11 Timer Block Diagram

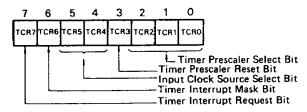

#### • Timer Control Register (TCR:\$0009)

Selection of the input clock source, selection of the prescaler and the control of timer interrupt can be accomplished by setting the corresponding bits in the timer control register (TCR: \$0009).

Timer Control Register (TCR: \$0009)

One of four input clock sources (shown in Table 2) can be selected depending on the value written into the TCR4 and TCR5.

After reset, these bits are initialized to the "AND of External Clock (applied to TIMER pin) and Internal Clocks (E)" mode (TCR4=0, TCR5=0). Thus, if the TIMER pin is "1", the counter starts to count down from "\$F0" just after reset.

Table 2 Input Clock Source Modes

| TO    | CR    | 0                                                                   |  |  |  |

|-------|-------|---------------------------------------------------------------------|--|--|--|

| Bit 5 | Bit 4 | Clock Input Source                                                  |  |  |  |

| 0     | 0     | Internal Clock (E)                                                  |  |  |  |

| 0     | 1     | AND of External Clock (applied to TIMER pin) and Internal Clock (E) |  |  |  |

| 1     | 0     | No Clock                                                            |  |  |  |

| 1     | 1     | External Clock<br>(through TIMER pin)                               |  |  |  |

Writing "1" to the TCR3 initializes the prescaler to zero. A read of this bit always indicates a "0".

The coding of the TCR0 to TCR2 bits produces a division in

the prescaler as shown in Table 3. One of eight outputs of the prescaler  $(\div 1, \div 2, \div 4, \div 8, \div 16, \div 32, \div 64, \div 128)$  is selectable. After reset, these bits are set to the " $\div 1$ " mode.

Table 3 Prescaler Division Select

|       | TCR   |       | Prescaler Division |

|-------|-------|-------|--------------------|

| Bit 2 | Bit 1 | Bit 0 |                    |

| 0     | 0     | 0     | ÷ 1                |

| 0     | 0     | 1     | ÷2                 |

| 0     | 1     | 0     | ÷4                 |

| 0     | 1     | 1     | ÷8                 |

| 1     | 0     | 0     | ÷16                |

| 1     | 0     | 1     | ÷32                |

| 1     | 1     | 0     | ÷64                |

| 1     | 1     | 1     | ÷128               |

The timer interrupt is enabled when the TCR6 bit is "0" and disabled when the bit is "1". When a timer interrupt occurs, the TCR7 bit is set to "1". This bit must be cleared by writing "0" into it.

#### ■ SERIAL COMMUNICATION INTERFACE (SCI)

The SCI is used for a serial transfer of 8-bit data. The transfer clock width ranges from 1  $\mu$ s to about 32 ms (with a 4 MHz oscillator), and sixteen types of transfer clock widths are available. The SCI consists of three registers, an octal counter and a prescaler as shown in Fig. 10. It communicates with CPU via the data bus lines and with peripherals via bits 3, 4 and 5 of Port D. The following are descriptions of the registers and the data transfer operations.

SCI Control Registers (SCR; 0010) SCR6 SCR4 SCR3 SCR2 SCR1 SCR0 SCR5 Transfer Multi-Clock Generator Ds (CK) Octal SCI Data Register (SDR:\$0012) Counter Initialize n D<sub>4</sub> (Rx) LSB  $D_3(Tx)$ 7 6 5 SCI Status Register (SSR:\$0011) SSR6 SSR5 SSR4 SSR3 Not Used

Figure 12 SCI Block Diagram

#### • SCI CONTROL REGISTER (SCR: \$0010)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| SCR7 | SCR6 | SCR5 | SCR4 | SCR3 | SCR2 | SCR1 | SCRO |

#### Bit 7 (SCR7)

When this bit is set, the DDR bit corresponding to the  $D_3$  pin goes to "1" and the  $D_3$  pin acts as output of SCI data. Resetting the MCU clears this bit.

| SCR7 | D <sub>3</sub>                  |

|------|---------------------------------|

| 0    | Used as I/O pin (by DDR)        |

| 1    | Serial data output (DDR output) |

#### Bit 6 (SCR6)

When this bit is set, the DDR bit corresponding to the D<sub>4</sub> pin goes to "1" and the D<sub>4</sub> pin acts as input of SCI data. Resetting the MCU clears this bit.

| SCR6 | D <sub>4</sub>                  |

|------|---------------------------------|

| 0    | Used as I/O pin (by DDR)        |

| 1    | Serial data input (DDR output). |

#### Bit 5, 4 (SCR5, SCR4)

|   | SCR5 | SCR4 | Clock Source | D <sub>s</sub>            |  |  |  |  |  |  |

|---|------|------|--------------|---------------------------|--|--|--|--|--|--|

| - | 0    | 0    | _            | Used as I/O pin (by DDR)  |  |  |  |  |  |  |

|   | 0    | 1    |              | Osed as 1/O pin (by DDN)  |  |  |  |  |  |  |

| _ | 1    | 0    | Internal     | Clock output (DDR output) |  |  |  |  |  |  |

| - | 1    | 1    | External     | Clock input (DDR input)   |  |  |  |  |  |  |

#### Bit 3 ~ 0 (SCR3 ~ SCR0)

SCI/TIMER2

These bits select a transfer clock width. Resetting the MCU clears all these bits.

| CODO | SCR2 | SCR1 | SCRO      | Transfer Clock Width |         |  |  |  |  |  |  |

|------|------|------|-----------|----------------------|---------|--|--|--|--|--|--|

| SCR3 | SCRZ | SCHI | 4.194 MHz |                      |         |  |  |  |  |  |  |

| 0    | 0    | 0    | 0         | 1 μs                 | 0.95 μs |  |  |  |  |  |  |

| 0    | 0    | 0    | 1         | 2 μs                 | 1.91 µs |  |  |  |  |  |  |

| 0    | 0    | 1    | 0         | 4 μς                 | 3.82 µs |  |  |  |  |  |  |

| 0    | 0    | 1    | 1         | 8 µs                 | 7.64 µs |  |  |  |  |  |  |

| ₹    | ₹    | . ₹  | ₹ .       | ₹                    | ₹ .     |  |  |  |  |  |  |

| 1    | 1    | 1    | 1         | 32768 µs             | 1/32 s  |  |  |  |  |  |  |

#### SCI Data Register (SDR: \$0012)

A serial-parallel conversion register used for data transfer.

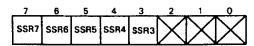

#### • SCI Status Register (SSR: \$0011)

#### Bit 7 (SSR7)

This is the SCI interrupt request bit which is set on the completion of transmitting or receiving 8-bit data. It is cleared when the MCU is reset or data is written to or read from the SCI data register with the SCR5 = "1". This bit can also be cleared by writing a "0" into it.

#### Bit 6 (SSR6)

This is the TIMER<sub>2</sub> interrupt request bit. The TIMER<sub>2</sub> is also used as the serial clock generator, and this bit is set on the every negative edge of the internal transfer clock. When the MCU is reset, the bit is cleared. It can also be cleared by writing "0" into it. (For details, see "TIMER").

#### Bit 5 (SSR5)

This is the SCI interrupt mask bit which can be set or cleared by software. When this bit is "1", the SCI interrupt (SSR7) is masked. Resetting the MCU sets this bit to "1".

#### Bit 4 (SSR4)

This is the TIMER<sub>2</sub> interrupt mask bit which can be set or cleared by software. When this bit is "1", the TIMER<sub>2</sub> interrupt (SSR6) is masked. Resetting the MCU sets this bit to "1".

#### Bit 3 (SSR3)

Writing "1" into this bit initializes the prescaler of the transfer clock generator. A read of this bit always indicates "0".

Bit 2 ~ Bit 0 Not Used.

| SSR 7 | SCI Interrupt Request                |

|-------|--------------------------------------|

| 0     | Not Requested                        |

| 1     | Requested                            |

| SSR6  | TIMER <sub>2</sub> Interrupt Request |

| 0     | Not Requested                        |

| 1     | Requested                            |

| SSR5  | SCI Interrupt Mask                   |

| 0     | Interrupt Allowed                    |

| 1     | Interrupt Inhibited                  |

| SSR4  | TIMER <sub>2</sub> Interrupt Mask    |

| 0     | Interrupt Allowed                    |

|       | Interrupt Inhibited                  |

#### Transmit Operations

The transfer clock width and the clock source are determined by setting the corresponding SCI control register bits, and then the  $D_3$  pin and the  $D_5$  pin are set to serial data output pin and serial clock pin respectively. The transmit data should be moved from the accumulator or the index register into the SCI data register. Then, the data moved into the SCI data register is output through the  $D_3/Tx$  pin, starting with the LSB, synchronously with the negative edge of the serial clock. See Fig. 13. When 8 bits of data have been transmitted, the bit 7 of the SCI status register (interrupt request bit) is set on the positive edge of the last serial clock. This interrupt request can be masked by setting bit 5 of the SCI status register. After completion of the data transmission, the 8th bit of data (MSB) stays at the

$D_3/Tx$  pin. If the external clock source is selected, the transfer clock width determined by bit 0 to bit 3 of the SCI control register is ignored and the  $D_5/\overline{CK}$  pin is set as input. If the internal clock source is selected, the  $D_5/\overline{CK}$  is set as output and clocks are generated with the transfer clock width selected by bit 0 to 3 of the SCI control register.

Figure 13 SCI Timing

### Receive Operations

The transfer clock width and the clock source are determined by setting the corresponding SCI control register bits, and the D<sub>4</sub> pin and the D<sub>5</sub> pin are set to serial data input pin and serial clock pin respectively. Then the receive operation is enabled by dummy-reading or -writing the SCI data register. (This procedure is not needed after a data is received. It is needed after reset or when no data is received yet.) The received data through the D<sub>4</sub>/Rx pin is input to the SCI data register synchronously with the positive edge of the serial clock. (See Fig. 13.) At completion of 8-bit data reception, the bit 7 in the SCI status register (interrupt request bit) is set. This interrupt request can be masked by setting bit 5 of the SCI status register. If the external clock source is selected, the transfer clock width determined by bit 0 to bit 3 of the SCI control register is ignored and data is received synchronously with the clock input through the D<sub>5</sub>/CK pin. If the internal clock source is selected, the  $D_5/C\overline{K}$  acts as an output and clocks are output with the transfer clock selected by bit 0 to bit 3 of the SCI control register.

#### • TIMER2

The SCI transfer clock generator can be used as a timer. The clock which is selected by bit 3 to 0 in the SCI control register (4  $\mu$ s to approx. 32 ms with 4 MHz oscillator) is input to the bit 6 in the SCI status register (TIMER<sub>2</sub> interrupt request bit), and this bit is set on every negative edge of the clock. Thus, TIMER2 can be used as a reload counter or clock.

- Transfer clock generator is reset and TIMER2 interrupt mask bit (bit 4 of SCI status register) is cleared.

- 2. (6): TIMER2 interrupt request bit is set.

- 3, 5: TIMER<sub>2</sub> interrupt request bit is cleared.

TIMER<sub>2</sub> is used as the SCI transfer clock generator. If wanting to use the TIMER<sub>2</sub> independently of the SCI, select external clock source (SCR5=1, SCR4=1).

If internal clock source is selected, reading from or writing to the SCI data register causes the prescaler of the transfer clock generator to be initialized.

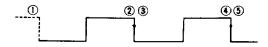

#### ■ I/O PORTS

There are 31 input/output pins (Ports A, B, C and D). Each I/O pin is programmed by setting the corresponding bit in the

Figure 14 I/O Port (Ports A, B, C, D) Diagram

data direction register (DDR) to "1" for output or "0" for input. When programmed as outputs, all I/O ports read latched data regardless of the logic levels at the output pin due to output loading. (See Fig. 14)

On reset, the DDRs and data registers go to "0", which

places all the ports in the input mode.

All input/output pins are TTL compatible and CMOS compatible as both inputs and outputs.

When not used, the I/O ports should be connected to VSS via resistors. With no lines connected to these pins, power may be consumed despite their not being used.

In EPROM mode, port A is used as EPROM data buses  $(EO_0 \sim EO_7)$ , port C as low order EPROM address buses  $(EA_0 \sim EA_7)$ , ports  $B_4$ ,  $B_5$  and  $B_7$  as  $EA_{11}$ ,  $EA_{10}$  and  $EA_8$  respectively. (The  $B_4$ ,  $B_5$  and  $B_7$  pins are three of high order EPROM address buses.)

Whether the port A data buses are used as inputs or outputs depends on  $\overrightarrow{OE}$  and  $\overrightarrow{CE}$  signals regardless of the state of the DDR bits.

| DDR Bit | Output Data<br>Bit | Output State | Input to CPU |

|---------|--------------------|--------------|--------------|

| 1       | 0                  | 0            | 0            |

| 1       | 1                  | 1            | 1            |

| 0       | ×                  | 3-State      | Pin          |

#### ■ MODE SELECTION

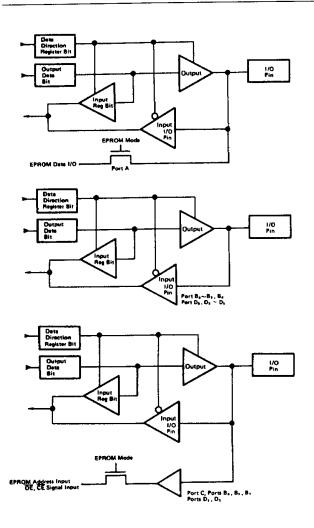

The HD63705V0 is capable of operating in two modes, the MCU mode and the EPROM mode.

The operating mode is determined by mode program pins; NUM pin and STBY pin as shown in Table 4.

#### MCU Mode

In this mode, all ports are available. (See Fig. 15.)

Table 4 Mode Selection

| Mode          | NUM | STBY | EPROM | RAM | Interrupt<br>Vector | Operation Mode         |

|---------------|-----|------|-------|-----|---------------------|------------------------|

| MCU Mode      | "L" | •    | I     | 1   | ı                   | Single Chip Mode       |

| EPROM<br>Mode | "H" | "L"  | I     | *   | •                   | EPROM Programming Mode |

<sup>&</sup>quot;L" = logic "0", "H" = logic "1", I; Internal, \*Don't care

#### EPROM Mode

In this mode, the EPROM can be programmed. For detail, see "PROGRAMMING THE EPROM."

#### Mode and Port

Table 5 shows MCU port condition in each mode.

Table 5 MCU Port Condition

| Mode<br>Port | MCU Mode | EPROM Mode                                                                                                                     |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| Port A       | I/O Port | Data Bus (EO <sub>0</sub> ~ EO <sub>7</sub> )                                                                                  |

| Port B       | I/O Port | Address Bus EA <sub>8</sub> (B <sub>7</sub> ), EA <sub>10</sub> , EA <sub>11</sub> (B <sub>5</sub> , B <sub>4</sub> ) (Note 1) |

| Port C       | I/O Port | Address Bus (EA <sub>0</sub> ~ EA <sub>7</sub> )                                                                               |

| Port D       | I/O Port | OE(D <sub>1</sub> ), CE(D <sub>2</sub> ) (Note 2)                                                                              |

| INT          | Input    | Address Bus (EA <sub>9</sub> )                                                                                                 |

| Timer        | Input    | Program Voltage V <sub>PP</sub>                                                                                                |

(Note 1)  $B_0 \sim B_1$  are not used.  $B_3$  should be connected to  $V_{SS}$ ,  $B_4$  is not used. (Note 2)  $D_0$  or  $D_3 \sim D_5$  are not used.  $D_6$  should be connected to  $V_{SS}$ .

#### MEMORY MAP

A memory map for each operating mode is shown in Fig. 17.

The first 32 locations of the MCU mode map are reserved for the MCU internal register area as shown in Table 6.

Figure 17 HD63705V0 Memory Map

#### Table 6 Internal Register

(R/W)

: Read/Write Register : Read Only Register

(R) (W)

: Write Only Register

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Address  | Read/Write *1/Initial Value after Reset |              |              |           |              |          |              |    |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------|--------------|--------------|-----------|--------------|----------|--------------|----|--|--|--|--|--|--|

| Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Address  | 7                                       | 6            | 5            | 4         | 3            | 2        | 1            | 0  |  |  |  |  |  |  |

| Port A Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$00     |                                         |              |              | R/        |              |          |              |    |  |  |  |  |  |  |

| Tott A Data Hegister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                         |              |              | \$0       |              |          |              |    |  |  |  |  |  |  |

| Port B Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$01     |                                         |              |              | R/        |              |          |              |    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                         |              | <del> </del> | \$0<br>R/ |              |          |              |    |  |  |  |  |  |  |

| Port C Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$02     |                                         |              |              | \$0       |              |          |              |    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -        | Not<br>Used                             |              |              | R/        |              |          |              |    |  |  |  |  |  |  |

| Port D Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$03     | 1                                       |              |              | \$0       | 0            |          |              |    |  |  |  |  |  |  |

| Port A Data Direction Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$04     |                                         |              |              | R/        |              |          |              |    |  |  |  |  |  |  |

| Port A Data Direction negister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$04     |                                         |              |              | \$0       |              |          |              |    |  |  |  |  |  |  |

| Port B Data Direction Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$05     |                                         |              |              | R/        |              |          |              |    |  |  |  |  |  |  |

| TOTAL DATE OF THE PARTY OF THE |          |                                         |              |              | \$0       |              |          |              |    |  |  |  |  |  |  |

| Port C Data Direction Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$06     |                                         |              |              | R/<br>\$0 |              |          |              |    |  |  |  |  |  |  |