# Transistor Circuit Techniques

Discrete and integrated

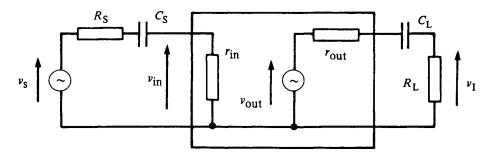

Third edition

G. J. Ritchie

# **Transistor Circuit Techniques**

discrete and integrated

#### TUTORIAL GUIDES IN ELECTRONIC ENGINEERING

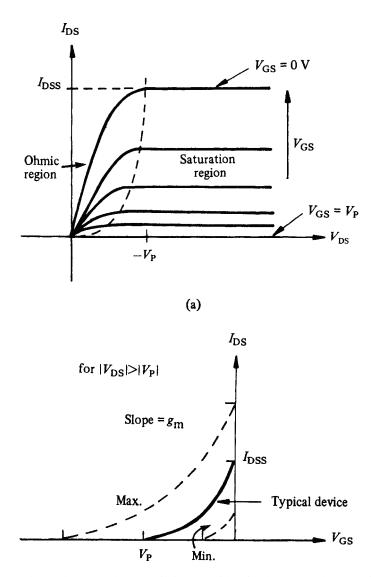

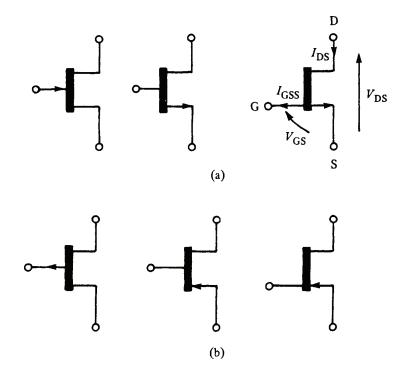

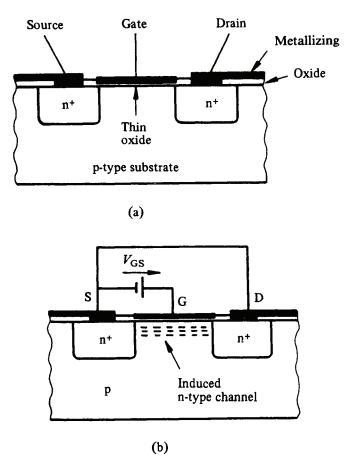

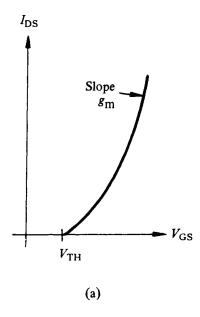

Series editors

Professor G.G.Bloodworth, University of York

Professor A.P.Dorey, University of Lancaster

Professor J.K.Fidler, University of York

This series is aimed at first- and second-year undergraduate courses. Each text is complete in itself, although linked with others in the series. Where possible, the trend towards a 'systems' approach is acknowledged, but classical fundamental areas of study have not been excluded. Worked examples feature prominently and indicate, where appropriate, a number of approaches to the same problem.

A format providing marginal notes has been adopted to allow the authors to include ideas and material to support the main text. These notes include references to standard mainstream texts and commentary on the applicability of solution methods, aimed particularly at covering points normally found difficult. Graded problems are provided at the end of each chapter, with answers at the end of the book.

# **Transistor Circuit Techniques**

discrete and integrated

#### Third edition

G.J.Ritchie

Department of Electronic Systems Engineering University of Essex

Text © G.J.Ritchie 1983, 1987, 1993

The right of G.J.Ritchie to be identified as author of this work has been asserted by him in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording or any information storage and retrieval system, without permission in writing from the publisher or under licence from the Copyright Licensing Agency Limited, of 90 Tottenham Court Road, London W1T 4LP.

Any person who commits any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages.

First edition published in 1983 by Chapman & Hall Second edition 1987 Third edition 1993

03 04 05 06 / 10 9 8 7 6 5 4 3

A catalogue record for this book is available from the British Library

ISBN 0 7487 4075 9

Page make-up by Colset Private Ltd

## **Contents**

| Preface to the third edition  |                                        | xi   |

|-------------------------------|----------------------------------------|------|

| Preface to the second edition |                                        | xiii |

| 1                             | Introduction to semiconductor devices  | 1    |

|                               | Objectives                             | 1    |

|                               | Semiconductors                         | 1    |

|                               | The junction diode                     |      |

|                               | Diode in equilibrium                   | 3 3  |

|                               | Reverse bias                           | 4    |

|                               | Forward bias                           | 5    |

|                               | The diode equation                     | 5    |

|                               | Breakdown                              | 8    |

|                               | Diode capacitance                      | 8    |

|                               | Diode ratings                          | 8    |

|                               | Diode models                           | 9    |

|                               | d.c. model                             | 9    |

|                               | Small-signal a.c. model                | 9    |

|                               | Breakdown diodes                       | 11   |

|                               | The bipolar junction transistor        | 12   |

|                               | BJT operation                          | 14   |

|                               | BJT current gain                       | 15   |

|                               | BJT characteristics                    | 16   |

|                               | Load line                              | 18   |

|                               | BJT ratings                            | 19   |

|                               | Integrated circuits                    | 19   |

|                               | The planar process                     | 20   |

|                               | Integrated BJTs                        | 21   |

|                               | Integrated diodes                      | 22   |

|                               | Integrated resistors                   | 22   |

|                               | Integrated capacitors                  | 23   |

|                               | Economic forces                        | 23   |

|                               | Summary                                | 24   |

|                               | Problems                               | 25   |

| 2                             | Introduction to amplifiers and biasing | 26   |

|                               | Objectives                             | 26   |

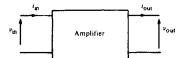

|                               | Amplifier fundamentals                 | 26   |

|                               | Amplifier gain                         | 26   |

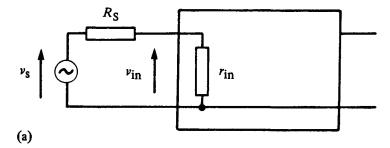

|                               | Input and output resistances           | 27   |

|                               | BJT configurations                     | 28   |

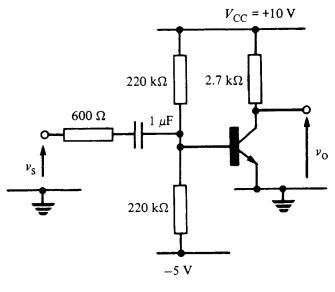

|                               | BJT biasing in common-emitter          | 29   |

|                               | The need for biasing                   | 29   |

|                               | Constant base current biasing          | 30   |

|                               | Shunt feedback biasing                 | 32   |

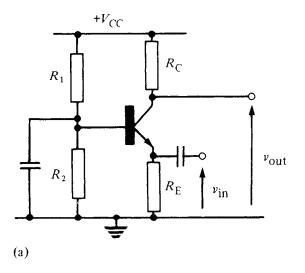

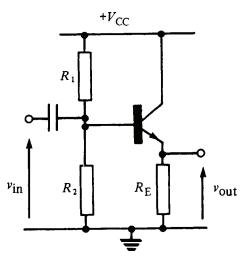

|                               | Potentiometer biasing                  | 34   |

|   | Biasing other configurations                  | 36 |

|---|-----------------------------------------------|----|

|   | Coupling capacitors                           | 36 |

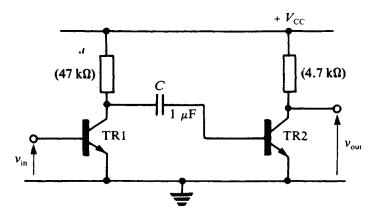

|   | Direct coupling                               | 38 |

|   | Summary                                       | 39 |

|   | Problems                                      | 39 |

| 3 | Small-signal BJT models and their application | 43 |

|   | Objectives                                    | 43 |

|   | Why model?                                    | 43 |

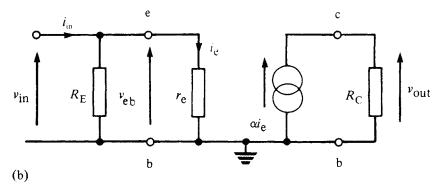

|   | A basic BJT model                             | 44 |

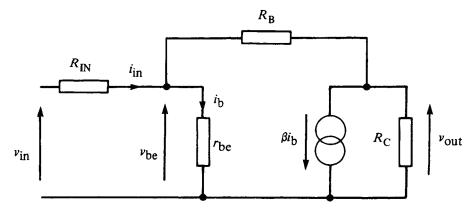

|   | Use of the model                              | 45 |

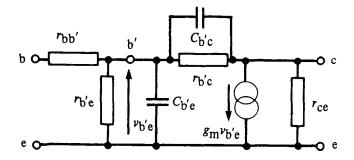

|   | Full hybrid- $\pi$ model                      | 48 |

|   | Simple common-base model                      | 50 |

|   | Summary                                       | 52 |

|   | Problems                                      | 52 |

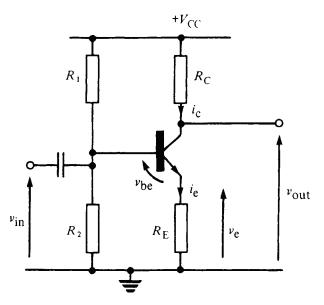

| 4 | Single-stage BJT amplifiers with feedback     | 55 |

|   | Objectives                                    | 55 |

|   | Series feedback amplifier                     | 55 |

|   | The emitter follower                          | 59 |

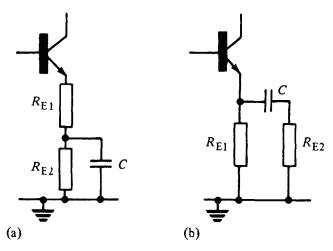

|   | Effect of emitter decoupling capacitor        | 62 |

|   | Shunt feedback amplifier                      | 64 |

|   | High-input resistance techniques              | 68 |

|   | Compound-connected BJTs                       | 68 |

|   | Bootstrap bias circuit                        | 69 |

|   | Summary                                       | 72 |

|   | Problems                                      | 73 |

| 5 | Linear integrated circuit techniques          | 75 |

|   | Objectives                                    | 75 |

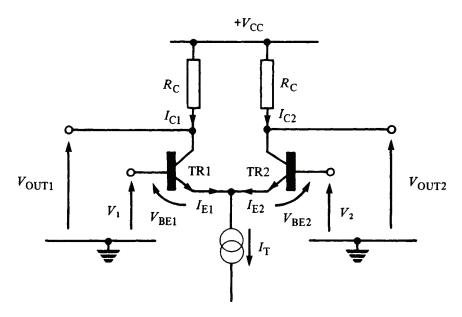

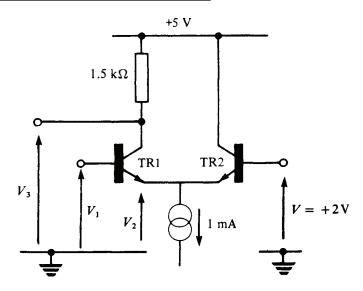

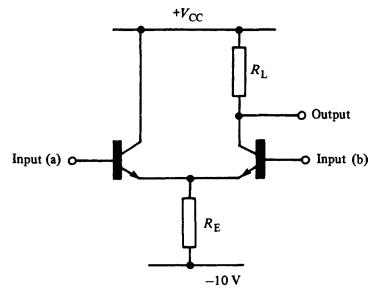

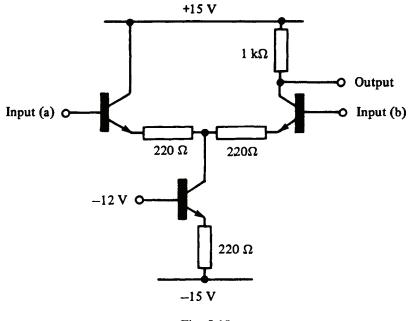

|   | The differential amplifier                    | 75 |

|   | Balance state                                 | 76 |

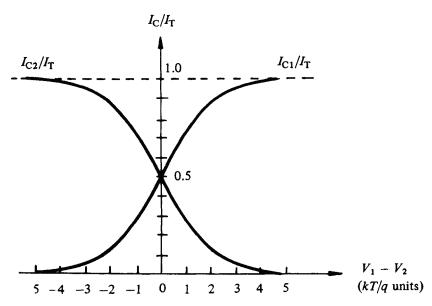

|   | Large-signal behaviour                        | 76 |

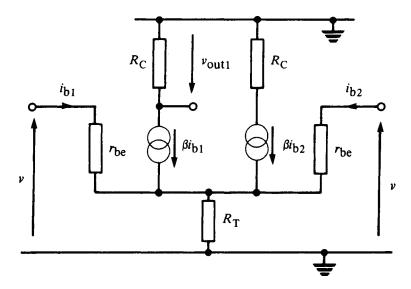

|   | Small-signal behaviour                        | 79 |

|   | Common-mode performance                       | 80 |

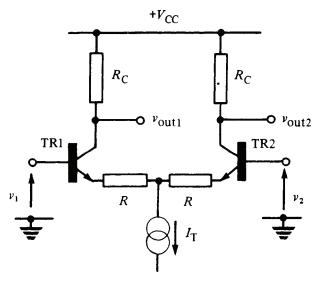

|   | Emitter feedback                              | 82 |

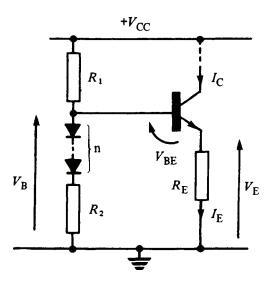

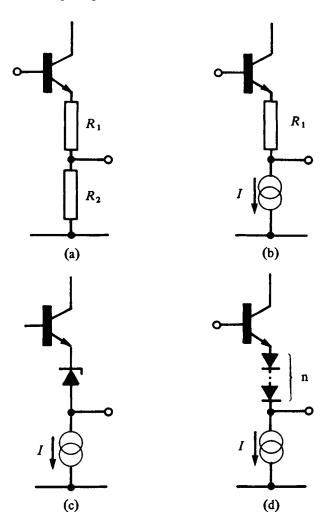

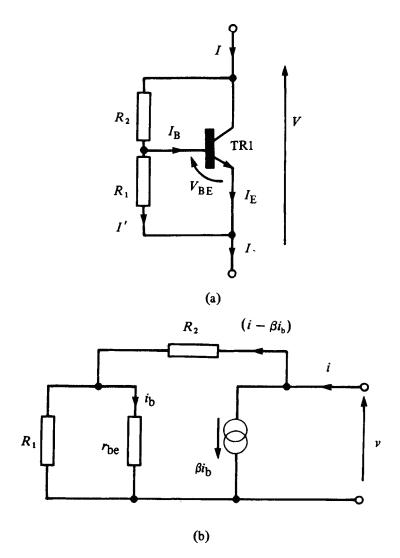

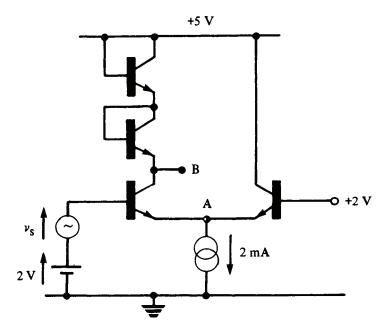

|   | Current sources                               | 83 |

|   | Temperature stability                         | 83 |

|   | Output resistance                             | 85 |

|   | Sources or sinks?                             | 86 |

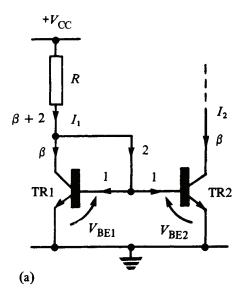

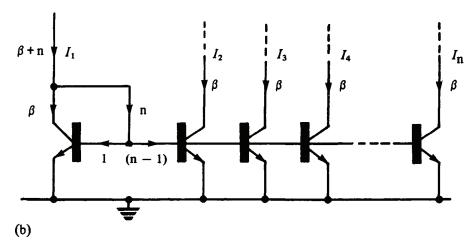

|   | Current mirrors                               | 86 |

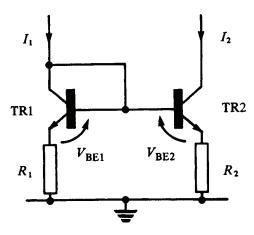

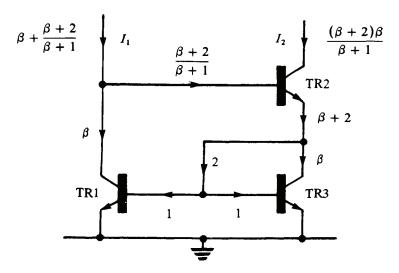

|   | Basic current mirror                          | 86 |

|   | Wilson mirror                                 | 89 |

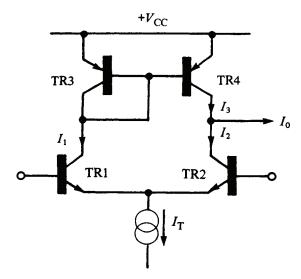

|   | Active loads                                  | 90 |

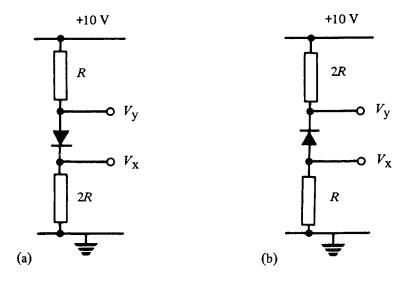

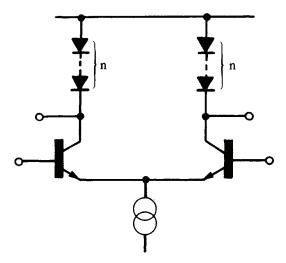

|   | Level-shifting circuits                       | 92 |

|   | The amplified diode                           | 93 |

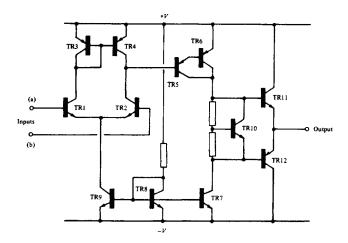

|   | A simple operational amplifier                | 95 |

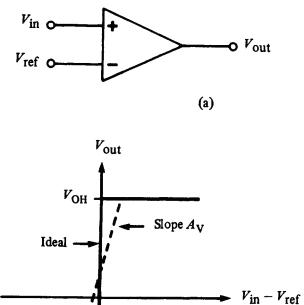

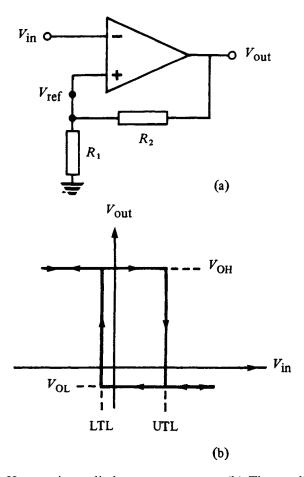

|   | The differential comparator                   | 96 |

|   | Summary                               | 98  |

|---|---------------------------------------|-----|

|   | Problems                              | 99  |

|   |                                       |     |

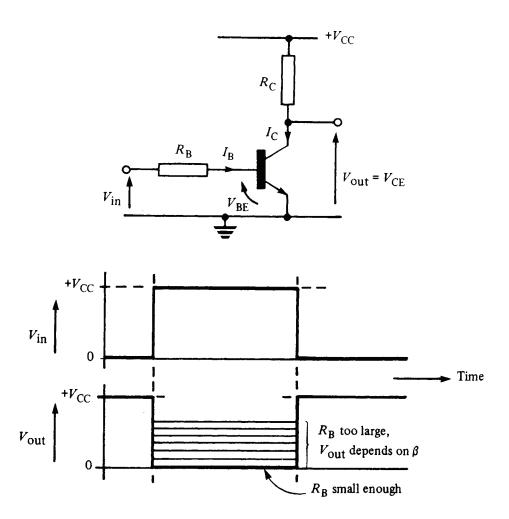

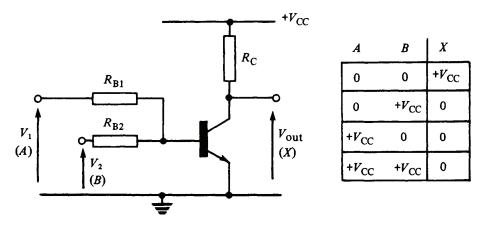

| 6 | BJT switching circuits                | 102 |

|   | Objectives                            | 102 |

|   | BJT regions of operation              | 102 |

|   | Simple switching circuits             | 103 |

|   | Single-stage inverter                 | 103 |

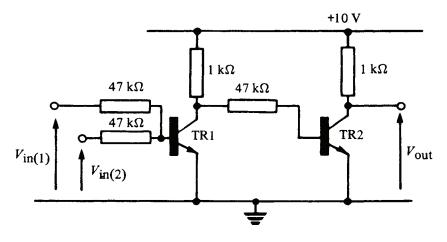

|   | BJT NOR gate                          | 104 |

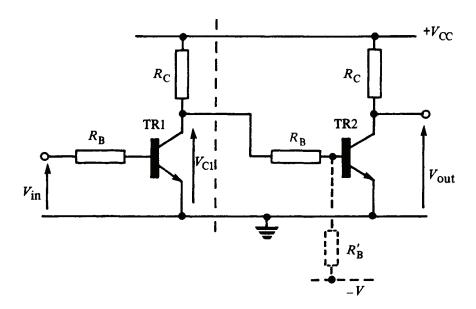

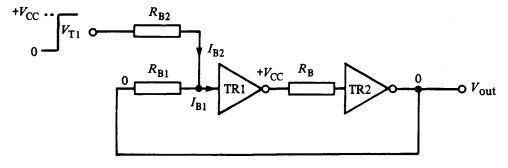

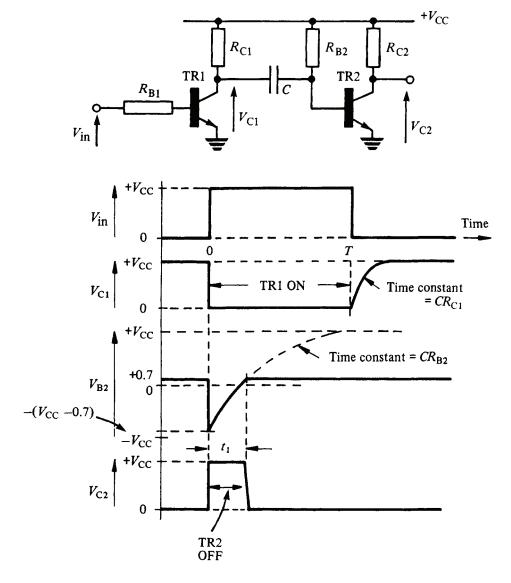

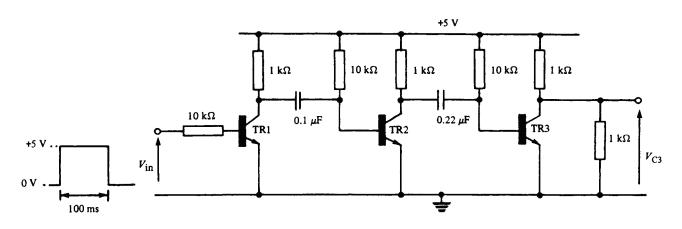

|   | Cascaded switching stages             | 105 |

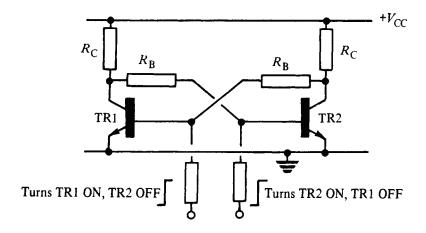

|   | Positive feedback: the bistable       | 106 |

|   | Timing circuits                       | 107 |

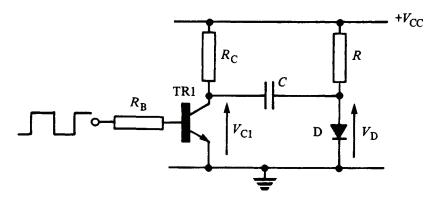

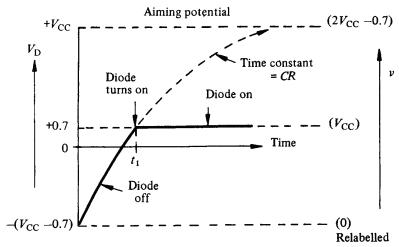

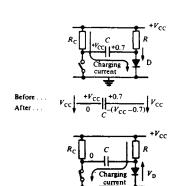

|   | Timing mechanism                      | 107 |

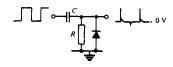

|   | Pulse generator                       | 109 |

|   | Monostable                            | 109 |

|   | Astable                               | 113 |

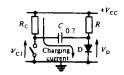

|   | Collector waveform improvement        | 115 |

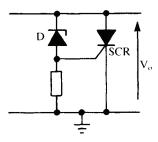

|   | Isolating diode                       | 115 |

|   | Emitter-follower                      | 116 |

|   | Junction breakdown protection         | 116 |

|   | Junction breakdown                    | 116 |

|   | Protection using emitter diodes       | 118 |

|   | Protection using base diodes          | 118 |

|   | An integrated circuit timer           | 119 |

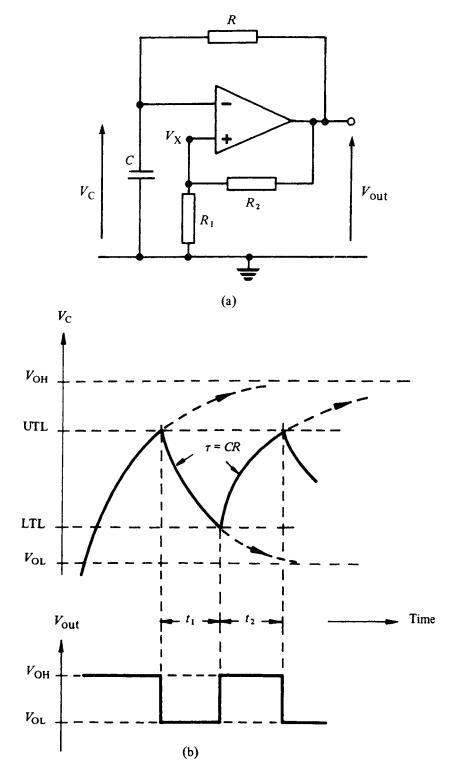

|   | Differential comparator oscillator    | 122 |

|   | Summary                               | 125 |

|   | Problems                              | 125 |

|   |                                       |     |

| 7 | Field-effect transistors and circuits | 128 |

|   | Objectives                            | 128 |

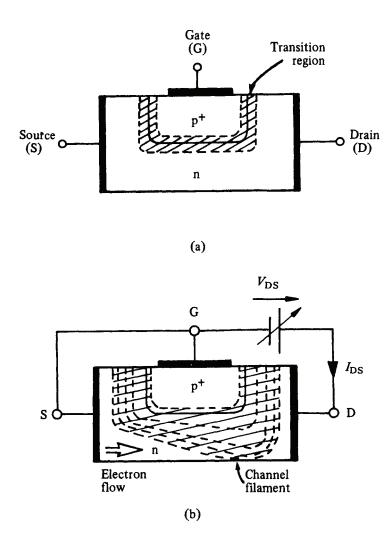

|   | The JFET                              | 128 |

|   | Structure and operation               | 128 |

|   | Characteristic equations              | 131 |

|   | The MOST                              | 133 |

|   | Structure and operation               | 133 |

|   | Characteristic equations              | 136 |

|   | Small-signal model                    | 137 |

|   | FET amplifiers                        | 138 |

|   | Biasing                               | 138 |

|   | Current sources                       | 141 |

|   | Temperature stability                 | 141 |

|   | Common-source amplifier               | 142 |

|   | Series feedback amplifier             | 142 |

|   | Source follower                       | 143 |

|   | Differential amplifier                | 143 |

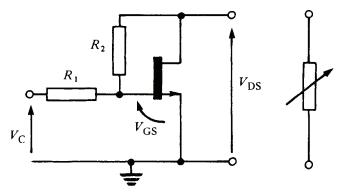

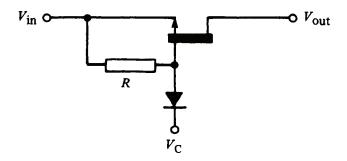

|   | Voltage-variable resistor             | 143 |

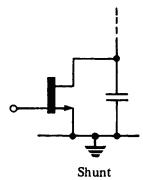

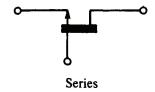

|   | FET switches                          | 145 |

|   | Shunt switch                          | 145 |

|   | Series switch                         | 145 |

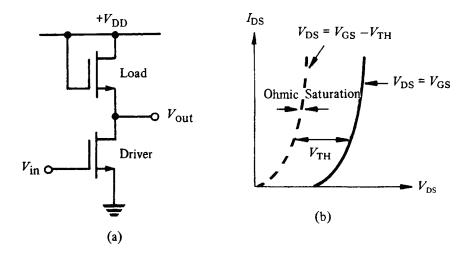

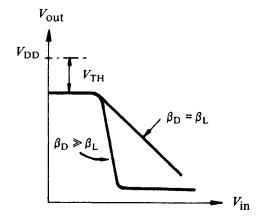

|   | MOS logic gates                               | 146 |

|---|-----------------------------------------------|-----|

|   | MOS inverter                                  | 146 |

|   | MOS NOR and NAND gates                        | 149 |

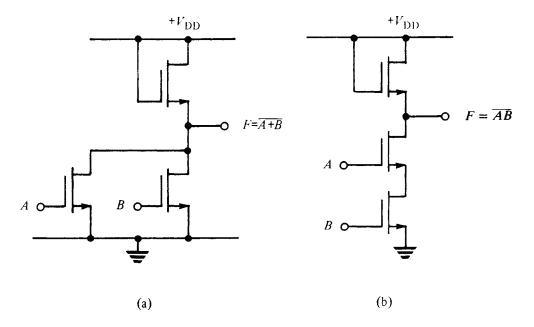

|   | CMOS logic gates                              | 149 |

|   | Summary                                       | 150 |

|   | Problems                                      | 151 |

| 8 | Audio power amplifiers                        | 153 |

|   | Objectives                                    | 153 |

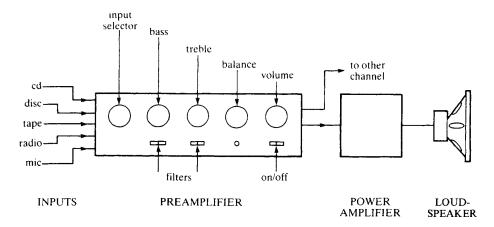

|   | An audio system                               | 153 |

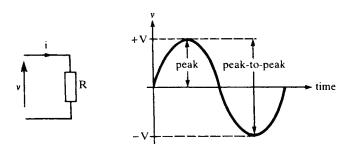

|   | Voltage, current and power                    | 154 |

|   | Distortion                                    | 155 |

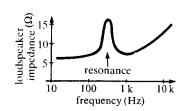

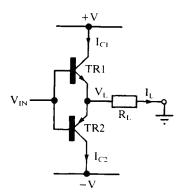

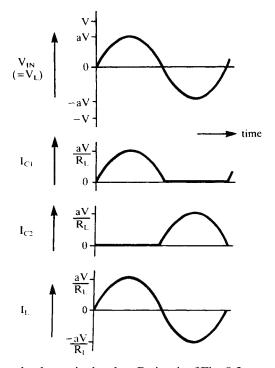

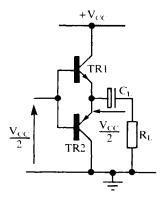

|   | Power amplifier output stage                  | 156 |

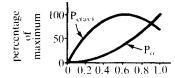

|   | Class A and class B operation                 | 156 |

|   | The amplified diode                           | 160 |

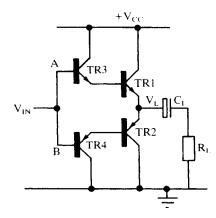

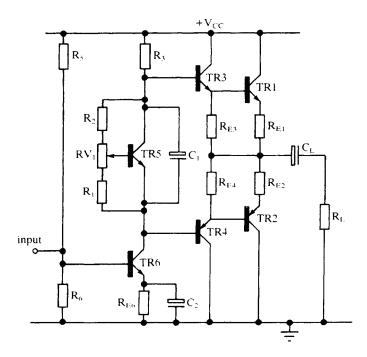

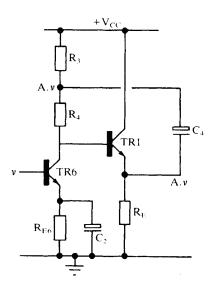

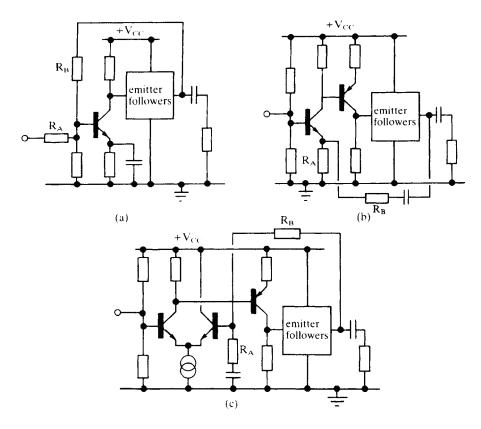

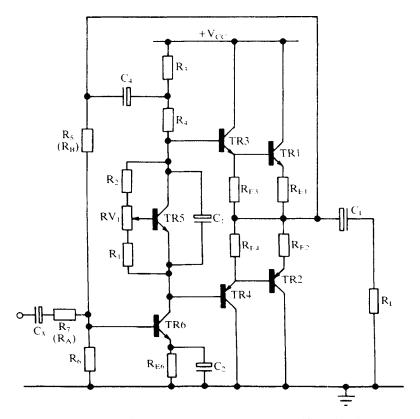

|   | Voltage gain stages and overall configuration | 163 |

|   | Collector load bootstrapping                  | 165 |

|   | Overall configuration                         | 166 |

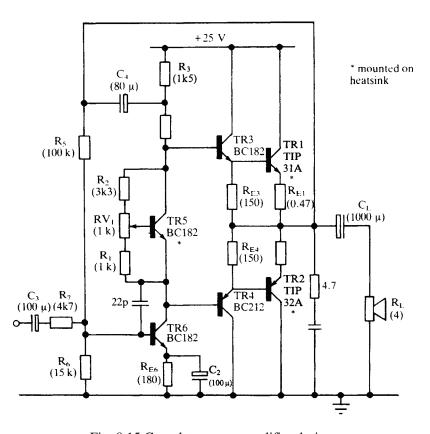

|   | An audio power amplifier design procedure     | 167 |

|   | Specification                                 | 167 |

|   | Supply voltage requirements                   | 168 |

|   | Output stage considerations                   | 168 |

|   | Driver stage                                  | 169 |

|   | Input sensitivity and voltage gain            | 171 |

|   | Low-frequency response                        | 171 |

|   | Comments                                      | 171 |

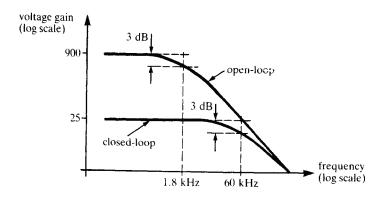

|   | Performance                                   | 172 |

|   | Other aspects of power amplifiers             | 173 |

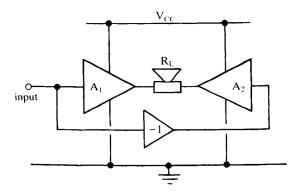

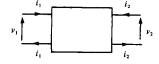

|   | Bridge configuration                          | 173 |

|   | Use of power MOSTs                            | 174 |

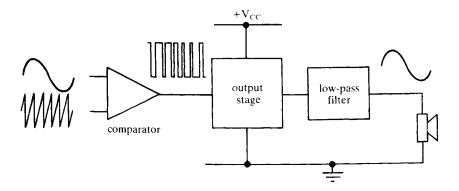

|   | Class D operation                             | 174 |

|   | Summary                                       | 175 |

|   | Problems                                      | 176 |

| 9 | Power supply regulators                       | 177 |

|   | Objectives                                    | 177 |

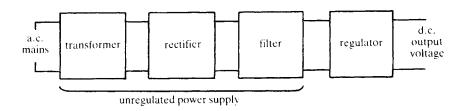

|   | Introduction                                  | 177 |

|   | The unregulated supply                        | 177 |

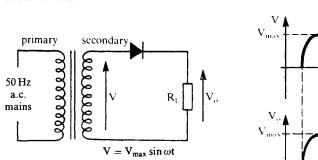

|   | Transformer                                   | 177 |

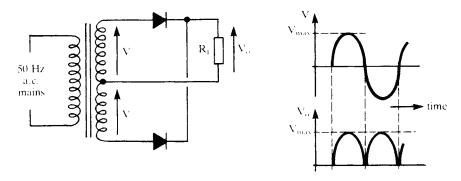

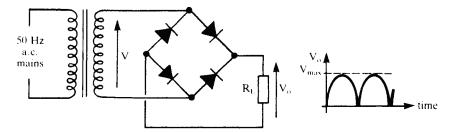

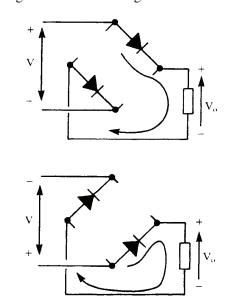

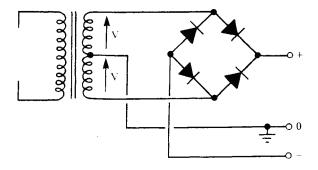

|   | Rectifier                                     | 178 |

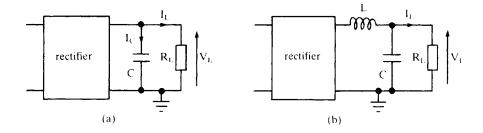

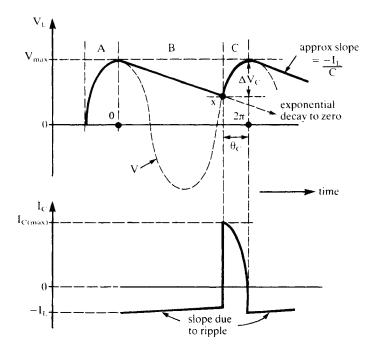

|   | Filter                                        | 180 |

|   | Rectifier and capacitor ratings               | 184 |

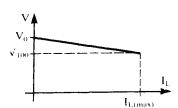

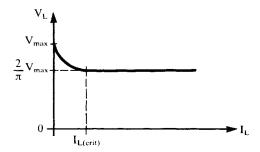

|   | Linear voltage regulators                     | 185 |

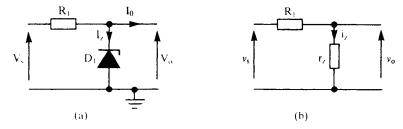

|   | Shunt voltage regulators                      | 186 |

|   | Series voltage regulators                     | 188 |

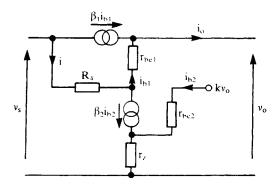

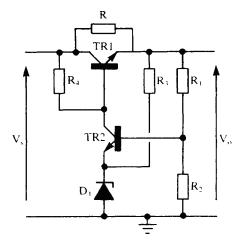

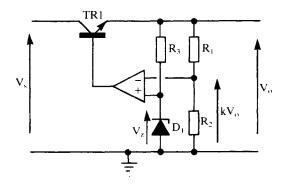

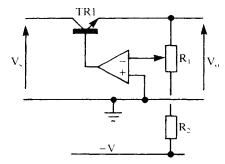

|   | Feedback series regulators using BJTs         | 189 |

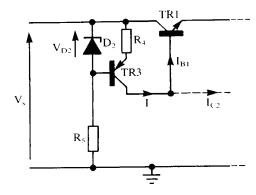

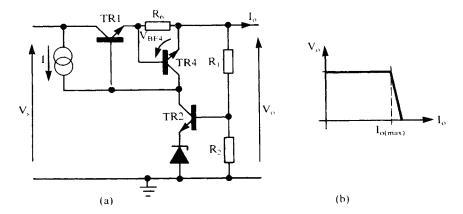

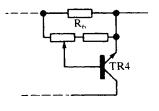

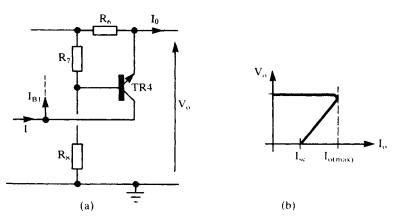

|   | Overload protection                           | 193 |

|   | Series regulators using op-amps               | 196 |

|   | Regulator design examples                     | 198 |

| BJT implementation                                 | 198 |

|----------------------------------------------------|-----|

| Op-amp implementation                              | 200 |

| Introduction to switching regulators               | 201 |

| Summary                                            | 202 |

| Problems                                           | 203 |

| Appendix A Preferred values for passive components | 204 |

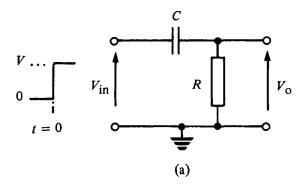

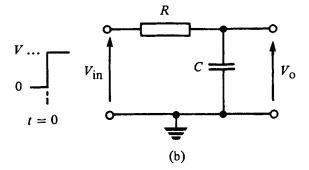

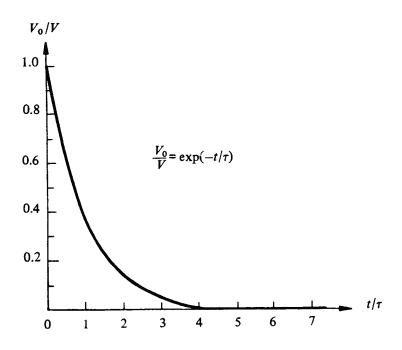

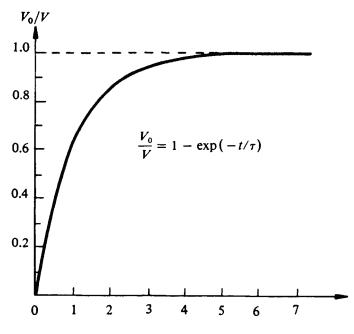

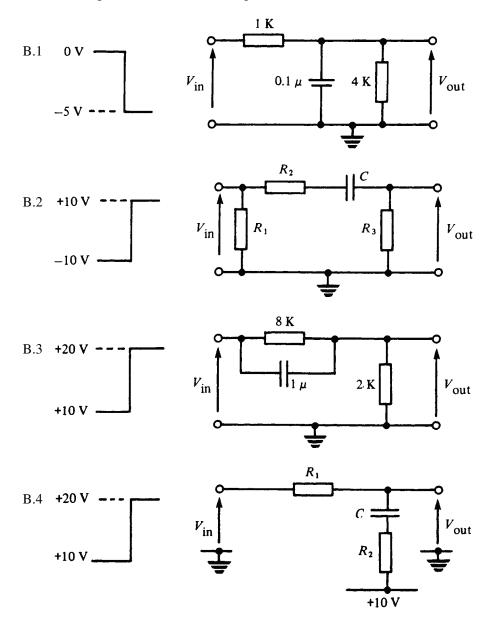

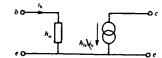

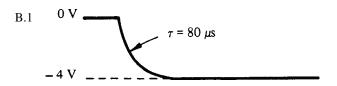

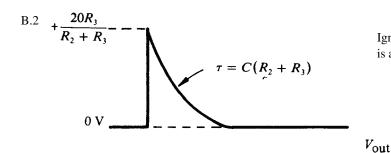

| Appendix B Transient response of R-C circuits      | 206 |

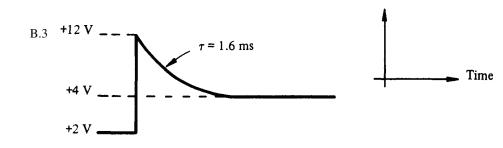

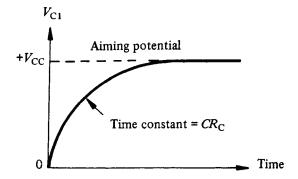

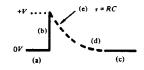

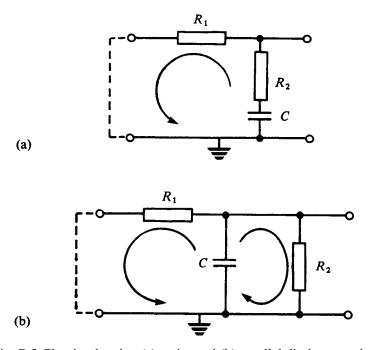

| Intuitive solution                                 | 208 |

| Determination of time constant                     | 209 |

| Problems                                           | 211 |

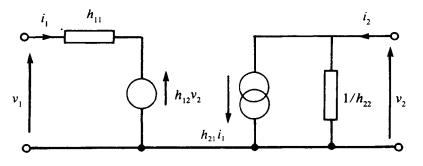

| Appendix C h-parameter modelling of BJTs           | 212 |

| Circuit analysis using <i>h</i> -parameters        | 215 |

| References                                         | 216 |

| Answers to problems                                | 217 |

### Preface to the third edition

Many encouraging comments extending back to the launch of the First Edition have prompted additional chapters on audio power amplifiers and power supplies. Naturally, new concepts are introduced but many of the techniques covered in earlier chapters are reinforced, particularly by the three substantial design studies.

Again, as for the Second Edition, the opportunity has been taken to rationalize and update references to other books, in particular to those in this series.

I gratefully acknowledge useful discussion on audio amplifiers with Dr Malcolm Hawksford, as well as the careful and constructive comment from my editor, Professor Greville Bloodworth.

G.J.Ritchie

### Preface to the second edition

A penalty suffered by the author of the first book in a series is his inability to refer to those that follow. Now with a substantial number of books published in the series, it is possible in this second edition to cross-reference many of these excellent texts. Several new problems have been added and, by popular request, the material on *h*-parameters has been extended in the form of an additional Appendix. I am very grateful to Professor John Sparkes (author of the title 'Semiconductor Devices' in this series) for his detailed comments and revisions suggested to harmonize our efforts.

#### Preface to the first edition

It has been my experience in teaching electronic circuit design that many firstyear degree students are frustrated by the lack of suitable texts at the right level of practical and theoretical content. Introductory volumes tend to be rather elementary while authoritative reference texts prove too extensive for this sensitive audience.

In this book my aim has been to guide the student gently through the analysis and design of transistor circuits, providing worked examples and design examples as illustration. Spread liberally throughout each chapter are exercises to test the reader's grasp of the material and a set of problems at the end of each chapter provides useful and realistic assessment. Extensive use has been made of margin comments to reinforce the main text by way of highlighting the most important features, giving references for further reading, recalling earlier material, summarizing the approach and emphasizing practical points.

It was considered essential to introduce, at an early stage, the concept of representing semiconductor devices by simple d.c. and a.c. models which prove so useful in circuit analysis. A brief description of semiconductors and device operation is justified in providing a basis for understanding diode and transistor behaviour, their characterization and limitations. Great importance is attached to a basic appreciation of integrated devices, bipolar and field-effect, particularly in terms of their matching and thermal tracking properties, as well as the fundamental economic law of integration, minimize chip area, which dictates the techniques used in modern circuit design.

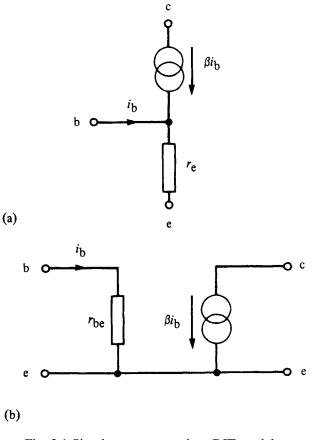

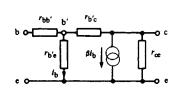

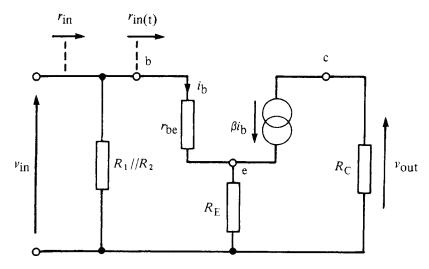

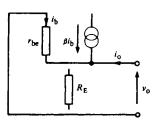

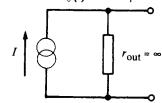

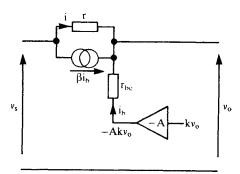

A very simple model of the bipolar transistor is developed using a single resistor ( $r_{be}$ ) and a current source ( $\beta_{ib}$ ). This is adequate for most low-frequency requirements; only when considering current sources has the  $r_{ce}$  parameter of the full hybrid-p equivalent circuit been invoked. The author does not favour the use of h-parameters since they are purely numbers and do not give the inherent prediction of parameter variation with bias current and current gain which is the forte of the hybrid- $\pi$  and simple models.

A wide range of transistor circuitry, both linear and switching, is covered in terms of fundamental qualitative circuit operation followed by analysis and design procedure. No apology is made for the extensive analytic treatment of circuits presented in this text—practice in analysis and engendering familiarity with design procedures are essential facets of the training of an electronic circuit designer.

It is hoped that this book instils a sound foundation of concept and approach which, even in this most rapidly developing area of modern electronics, will prove to be of lasting value.

I am grateful to my colleagues at Essex University, in particular Professors G.B.B. Chaplin and J.A.Turner and Dr J.K.Fidler, for many useful discussions. I also wish to thank my Consultant Editor, Dr A.P.Dorey of Southampton University, for his enthusiasm and very constructive assistance with this project.

## Introduction to semiconductor devices

| To define terms such as intrinsic (pure) and extrinsic (doped) semiconductors,   |

|----------------------------------------------------------------------------------|

| majority and minority carriers.                                                  |

| To explain in simple terms how a semiconductor diode operates and how its        |

| d.c. characteristic is expressed analytically by the diode equation.             |

| To approximate the d.c. behaviour of a forward biased diode to a constant        |

| voltage and represent its a.c. behaviour by the dynamic slope resistance.        |

| To explain junction breakdown and how a breakdown diode can be used as a         |

| simple voltage stabilizer.                                                       |

| To describe the operation of a bipolar junction transistor (BJT).                |

| To define the terms current gain, cut-off and saturation applied to a BJT.       |

| To describe the structure of integrated circuit components—BJTs, resistors       |

| and capacitors.                                                                  |

| To explain the value of the (planar) integrated circuit process in being able to |

| produce components which are matched and whose parameters track with             |

| temperature.                                                                     |

| -                                                                                |

Objectives

The following general references are useful for this chapter:

Millman and Grabel

(1987), Chapters 1–5.

Sparkes (1987).

In the design of electronic circuits it is important to know about discrete semiconductor devices such as diodes and transistors, their terminal properties and limitations. While device behaviour can be expressed in terms of complex equations, it is much more important to be able to characterize devices in the form of approximate, simple, a.c. and d.c. models which assist in both the analysis and design processes.

This chapter aims to develop a simple understanding of device operation and characterization which subsequently is applied to the design of amplifiers and switching circuits. Although the emphasis is on discrete components and fundamental circuit techniques, the influence of integrated circuit design is equally important.

#### Semiconductors

A pure or intrinsic semiconductor is conveniently recognized as having a conductivity between that of a metal and of an insulator although, as we shall see later, this is not the formal definition of the term. Many elements and compounds exhibit semiconductor properties but in this text we shall restrict our discussion to Group 4 elements such as silicon.

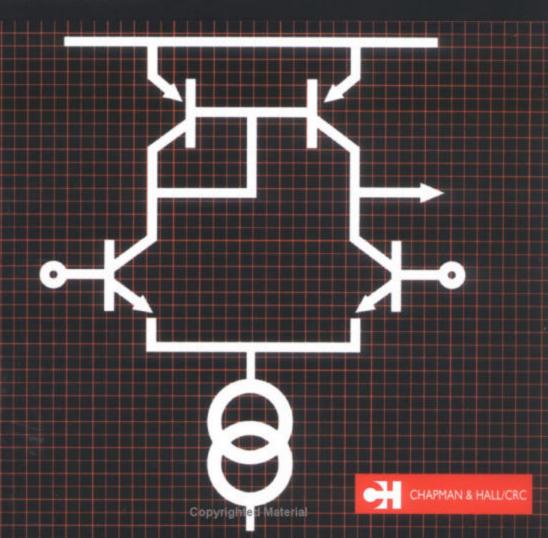

Fig. 1.1a shows a very simple representation of the covalent bonding between silicon atoms in a crystal lattice structure. At a temperature of absolute zero the valence electrons are very tightly bound into the structure; none are free for conduction and the resistivity of the material is very high, approaching that of a

GaAs, GaP and GaAlAs are particularly important as materials for optical devices such as light-emitting diodes, photodetectors and lasers. Germanium has largely been supplanted by silicon for diodes and transistors and is not used in integrated circuit fabrication.

A formal treatment of conduction mechanisms in semiconductors is beyond the scope of this text.

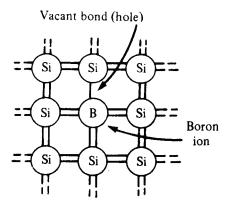

Fig. 1.1 (a) Pure silicon crystal (complete covalent bonding), (b) Phosphorus-doped n-type silicon (lightly bound electron), (c) Boron-doped p-type silicon (vacant bonds=hole).

perfect insulator. However, as the temperature is raised the valence electrons gain more and more thermal (kinetic) energy and lose their immediate association with host ions; they become mobile and permit electrical conduction within the material. Thus resistivity falls with increasing temperature: a more correct definition of a semiconductor is—a material which exhibits a negative temperature coefficient of resistivity, at least over a certain temperature range. It is important to appreciate that the silicon **ions** are locked into the crystal lattice and, being immobile, do not contribute to the conduction mechanism.

In their pure crystalline state intrinsic semiconductors have little application to devices and are usually doped by the addition of a controlled amount of impurity.

If a Group 5 impurity element such as phosphorus is introduced, each phosphorus atom bonds covalently within the silicon crystal lattice and introduces one extra, lightly bound electron (Fig. 1.1b). These electrons take part in the conduction

process at all but very low temperatures and are termed **majority carriers** in **n-type**, Group 5 doped semiconductors. The resistivity of a doped semiconductor is significantly less than that of the intrinsic material.

In contrast, if a Group 3 element such as boron is introduced as impurity into the silicon crystal, the three bonding electrons of each boron atom form covalent bonds with adjacent silicon atoms leaving one vacant bonding site, or **hole** (Fig. 1.1c). A hole may be considered mobile, as an electron from a neighbouring atom can fill it leaving a vacant site behind; in this way, the hole has moved. It is convenient to think of holes as positively charged mobile carriers—majority carriers in Group 3 doped, **p-type** semiconductors.

Doped semiconductors, both n-type and p-type, are also known as extrinsic semiconductors and the dopant ions, Group 3 or Group 5, are fixed in the crystal lattice just as are the silicon ions.

At normal ambient temperatures (around 290 K), mobile holes and electrons both exist in a semiconductor. However, the type of doping dictates which charge carrier dominates as the majority carrier (as described above), depressing below intrinsic level the concentration of the other carrier—the minority carrier. In n-type semiconductors, electrons are the majority carriers, holes the minority carriers; for p-type material, holes are the majority carriers and electrons the minority ones.

n-type→**n**egatively charged electrons

p-type→**p**ositively charged holes

#### The junction diode

The simplest semiconductor component fabricated from both n-type and p-type material is the junction diode, a two-terminal device which, ideally, permits conduction with one polarity of applied voltage and completely blocks conduction when that voltage is reversed.

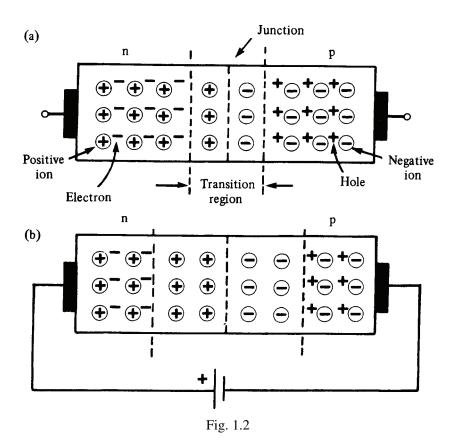

Consider a slice of semiconductor material one end of which is doped n-type, the other p-type. The n-type impurity dopant may be regarded as introducing fixed positively charged ions with loosely bound (negatively charged) electrons into the crystal lattice; the p-type dopant produces negative ions with attendant (positive) mobile holes.

#### Diode in equilibrium

In the immediate junction region between the n-type and p-type material, electrons can easily diffuse from the n-type into the p-type region, and holes can diffuse in the opposite direction. Both these diffusions result in a net transfer of positive charge from the p-region towards the n-region so that a potential difference and an electric field are developed between the two regions. The region within which this field is significant is called the **transition region**. In equilibrium the tendency of holes and electrons to diffuse and the effect of the field on the electrons and holes in the transition region just balance. The combined effect of both field and diffusion reduces the density of both electrons and holes to a level that is much less than the majority carrier density in either region, so the transition region is also sometimes called the **depletion layer**. It still contains small densities of mobile carriers so it is not wholly depleted; it also contains the positive and negative ions that are fixed in the lattice, as shown in Fig. 1.2, so transition region is usually the better term to use.

#### Reverse bias

If an external potential is applied to the device, making the p-type material more negative with respect to the n-type, the electric field strength at the junction is increased, repelling mobile carriers further from the junction and widening the transition region (Fig. 1.2b). Under such circumstances, it would be expected that no current would flow across the junction with this reverse bias applied; however, in practice, a small current does flow. The **leakage** (or reverse) current is due to the **minority** carriers (the low-concentration holes in n-type and electrons in p-type) being attracted across the junction by the applied potential. It is temperature-dependent since, as the temperature is increased, more carriers are thermally generated.

In practice, because of surface leakage as well, it is reasonable to assume that the leakage current doubles approximately every 7 °C.

Variation of the width (w) of the transition region by applied voltage is important when considering the operation of junction field-effect transistors (see Chapter 7) and is given by

$$\mathbf{w} \propto (\psi + V_{\rm r})^{x} \tag{1.1}$$

where  $V_r$  is the applied reverse voltage,  $\psi$  is the diffusion potential associated with the electric field at the junction ( $\psi \approx 0.7 \text{ V}$  for silicon), and x is a constant, either 1/2 or 1/3 depending on the method used in fabricating the junction.

Positive attracts negative, and vice versa.

Leakage current can be as low as several tens of nanoamps at room temperature.

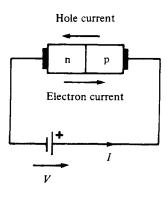

#### Forward bias

If the external bias voltage is now reversed, with the more positive potential connected to the p-region, the electric field strength in the transition region is reduced so that carriers can more easily flow through the junction. In a normal rectifier diode, holes from the p-region and electrons from the n-region flow through the junction. Since these opposing movements involve oppositely charged carriers they add together to form the total current I (amps) given by

$$I \propto \exp\left(\frac{qV}{kT}\right) \tag{1.2}$$

where q is the electronic charge (1.602×10<sup>-19</sup> coulombs), V is the forward bias potential (volts), k is Boltzmann's constant (1.38×10<sup>-23</sup> joule/K), and T is the temperature (K).

At a nominal ambient temperature of 290 K, kT/q can be evaluated as approximately 25 mV. This is an important figure, as will be seen later, and should be committed to memory.

The electron and hole currents (and the total current) may be regarded as the **injection** of majority carriers across the junction, the level of injection being controlled by the applied forward potential. The relative magnitudes of these current components are determined by the doping of the n-type and p-type regions. If the n-type region is much more heavily doped than the p-type then the forward current is almost all electron current; if the relative doping levels are reversed, the hole current is predominant. While this feature is of little significance with regard to the performance of junction diodes, it is vital in the manufacture of high-quality bipolar junction transistors.

#### The diode equation

The behaviour of a semiconductor junction diode may be summarized as

- passing current under forward bias, with an associated forward voltage drop; and

- 2. exhibiting a very small leakage current under reverse bias.

This can be expressed as a **diode equation**:

$$I = I_{\rm s} \left[ \exp\left(\frac{qV}{kT}\right) - 1 \right] \tag{1.3}$$

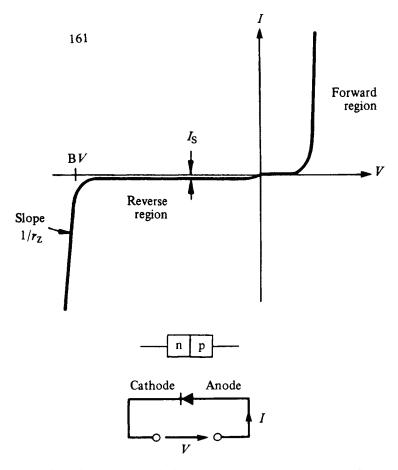

where  $I_s$  is the reverse leakage (or saturation) current. Fig. 1.3 shows this equation graphically (the device characteristic) and the diode symbol with defined directions of voltage and (positive) current.

Correspondence between the analytic expression of Equation 1.3 and the device characteristic can be checked. In the reverse region, for a sufficiently negative reverse voltage, the  $\exp(qV/kT)$  term is very small and may be ignored relative to the (-1) term. Under this condition, the reverse leakage current is given by  $I=I_s$ . For a forward bias (V positive) of greater than 115 mV, the (-1) term has less than 1% significance and conveniently may be discarded leaving the forward bias region of the characteristic described by the approximate relationship

$$I = I_{\rm s} \exp\left(\frac{qV}{kT}\right) \tag{1.4}$$

p-type **p**ositive and n-type **n**egative for forward bias.

In correspondence with thermionic valve terminology, the p-type terminal is called the **anode** and the n-type the **cathode**.

Derivation of the diode equation is complex; the reader is asked to take it on trust or to consult specialized texts.

Equation 1.3 is a simplification of the full diode equation which contains, in the exponential term, an extra factor which is current and material-dependent.

The direction of current flow is conventionally defined as that of positive charge carriers despite the fact that the current may be electron current or, as here, the sum of electron and hole currents. The current scale in the reverse region is highly magnified compared with that of the forward region.

Fig. 1.3 Junction diode characteristic (not to scale), symbol and defined current and voltage directions.

This corresponds with the injection description given by Equation 1.2.

The exponential nature of the forward characteristic makes it possible to calculate the change in forward voltage which results from increasing or decreasing the forward current by a certain ratio. Two useful ratios are the octave, a factor of 2 (or 1/2), and the decade, a factor of 10 (or 1/10).

There are corresponding voltages  $V_1$  and  $V_2$  for the two different currents  $I_1$  and  $I_2$ .

$$I_1 = I_s \exp\left(\frac{qV_1}{kT}\right)$$

and

$$I_1 = I_s \exp\left(\frac{qV_1}{kT}\right)$$

Therefore

$$\frac{I_2}{I_1} = \exp\left[\frac{q}{kT} \left(V_2 - V_1\right)\right] \tag{1.5}$$

It is interesting that we do not need to know the value of  $I_s$  to perform the voltage increment calculations. However, if we required the actual voltage, the value of  $I_s$  is necessary for calculation.

or

$$(V_2 - V_1) = \frac{kT}{q} \ln \left(\frac{I_2}{I_1}\right) \tag{1.6}$$

If  $I_2=2\times I_1$ , an octave relationship, then at T=290 K:

$$V_2 - V_1 = \frac{kT}{q} \ln 2 \approx 17.3 \,\text{mV}$$

This implies that increasing the forward current by a factor of two increases the forward voltage by 17.3 mV irrespective of  $I_s$  and of the actual current level, provided that the (-1) term in the diode equation may be ignored. If  $I_2$ =0.5 $I_1$ , a halving of forward current, Equation 1.6 also shows that the forward diode voltage is reduced by 17.3 mV.

Now, for a decade change in current,  $I_2=10\times I_1$ ,

$$V_2 - V_1 = \frac{kT}{q} \ln 10 \approx 57.6 \,\text{mV}$$

at 290 K

and for a reduction in current by a factor of 10, i.e.  $I_2$ =0.1 $I_1$ ,

$$V_2 - V_1 \approx -57.6 \,\text{mV}$$

Another result of the sharply rising nature of the exponential forward characteristic, when it is plotted against linear current and voltage scales, is that there appears to be little conduction until (for a silicon diode) a voltage of approximately 0.5 V is reached. Above that voltage the current rises more and more rapidly such that, for normal operating currents, there is little change of forward voltage in the region of 0.7 V. This feature arises as a result of plotting the characteristic on linear scales; if diode voltage is plotted against the logarithm of the forward current, the characteristic becomes, over much of its length, a straight line with slope approximately 60 mV/decade.

Given that the forward voltage of a diode is 0.7 V for a forward current of 5 mA at a temperature of 290 K, calculate the reverse leakage current,  $I_s$ .

[Answer:  $I_s$ =3.4×10<sup>-15</sup> A; a surprisingly low figure! In practice, low-power diodes usually exhibit leakage currents in the order of tens of nanoamps. The discrepancy between the two figures is due to current leakage across the physical surface of the diode which is additive to the junction leakage predicted by the diode equation. Another factor which destroys the exponential nature of the diode equation, particularly at higher current levels, is the resistance of the bulk doped semiconductor on either side of the junction; this gives an increased forward voltage at a given current.]

Temperature dependence of the diode characteristic can be determined by considering Equation 1.4 in the form

$$V = \frac{kT}{q} \ln \frac{I}{I_s} \tag{1.7}$$

Since we have already recognized that  $I_s$  increases with temperature then, to maintain a constant forward current I, the forward voltage V must be reduced as

Note that the voltage increments are proportional to absolute temperature (K).

**Exercise 1.1**

This may seem to be an insignificant figure but it does represent 200 mV over a temperature range of 100 °C, a sizeable fraction of the normal forward voltage.

temperature is increased. Thus the forward voltage drop has a negative temperature coefficient which, in practice, is approximately -2.2 mV/°C.

#### Breakdown

One feature of the diode characteristic not yet described is breakdown in the reverse bias region. When a certain reverse voltage, the reverse breakdown voltage (BV), is exceeded the reverse current increases dramatically for increasing reverse voltage (see Fig. 1.3) owing to the very high electric fields at the junction. The breakdown voltage can be controlled in manufacture by adjusting the doping levels: the higher the doping level, the lower the magnitude of the breakdown voltage. A diode with sufficiently high breakdown voltage should be chosen to preserve true rectifying action in normal circuit operation.

Depending on intended application, the breakdown voltage can range from several volts (breakdown diodes) to over 20 kV (high-voltage rectifiers).

#### Diode capacitance

While the nonlinear static (or d.c.) behaviour of a junction diode is characterized by the diode equation (Equation 1.3) or its approximation in the forward region (Equation 1.4) the device possesses capacitive properties which can be described in terms of transition capacitance and diffusion capacitance.

*Transition capacitance:* A junction diode under reverse bias may be considered as acting as a parallel-plate capacitor, the two plates being the bulk n-type and p-type semiconductor separated by the transition region dielectric. This transition capacitance  $(C_t)$  is proportional to the cross-sectional area (A) of the junction and inversely proportional to the width (w) of the transition region, i.e. the separation of the plates.

$$C_{\rm t} \propto \frac{A}{w}$$

Since the transition width is a function of the applied reverse voltage as given by Equation 1.1, the transition capacitance is also a function of voltage

$$C_{\rm t} \propto (\psi + V_{\rm r})^{-x}$$

which approximates to

$$C_{t} \propto V_{r}^{-x} \tag{1.8}$$

The capacitance of a varicap diode can be varied over a range of several hundred picofarads (large area device). Signal diodes generally have a capacitance of less than 10 pF.

(where x=1/2 or 1/3) for a reverse voltage ( $V_r$ ) greater than several volts. Diodes used as voltage-variable capacitors (varicaps or varactors) find wide application in the tuning sections of radio and television receivers.

Diffusion capacitance: A junction diode also possesses capacitive properties under forward bias conditions by virtue of charge crossing the junction region. This is a complex concept and the reader should refer to more advanced texts for detail. However, it is sufficient to note that the diffusion capacitance ( $C_d$ ) in forward bias is directly proportional to the forward current flowing through the device.

#### Diode ratings

Although semiconductor devices are robust and reliable, circuit designers must still ensure that they are operated within the range of capabilities for which they are

manufactured. Diodes are no exception and information regarding maximum permissible parameter limits (or ratings) can be found published in manufacturers' data. The important factors for a diode are maximum reverse voltage (before breakdown), maximum forward current, and maximum power dissipation (the product of forward current and forward voltage). These ratings must not be exceeded otherwise device failure can result, with catastrophic consequences. Careful selection from a wide range of available device types is therefore essential for reliable design.

#### Imagine the consequences of failure in a nuclear power station, an aircraft navigation system or even a domestic television receiver!

#### Diode models

d.c. model

The diode equation with its exponential nature is very difficult to use directly in circuit analysis and design and it is useful to have an approximation to the characteristic which can provide a reasonably accurate indication of device behaviour.

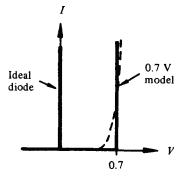

In circuits using high voltages little error would result if a diode were assumed to be ideal, i.e. zero voltage drop in the forward direction and zero leakage current in the reverse direction. However the voltages in most semiconductor circuits are not very large and a forward biased diode voltage of approximately 0.7 V can prove very significant. Therefore, as a second level of approximation, it is realistic to assume a constant 0.7 V drop in the forward direction and again ignore leakage current in the reverse direction.

#### Small-signal a.c. model

When a diode is biased with a constant forward current (I) there is a corresponding voltage drop (V) across its terminals. If the current is changed by a small amount ( $\pm \Delta I$ ) around I, the voltage will also change ( $\pm \Delta V$ ) and for very small variations  $\Delta I$  and  $\Delta V$  are related by the tangential slope of the characteristic at the bias point (V, I). Owing to the curvature of the characteristic, this slope is not constant but varies with I; as I increases, the slope increases. It is useful to obtain an expression for this slope and its reciprocal (dV/dI) which has dimensions of resistance and is referred to as the dynamic slope resistance ( $r_d$ ) of the diode.

Taking the approximate diode equation (Equation 1.4), and differentiating

$$I = I_{s} \left[ \exp\left(\frac{qV}{kT}\right) \right]$$

$$\therefore dI = \frac{q}{kT} I_{s} \left[ \exp\left(\frac{qV}{kT}\right) \right] dV$$

$$= \frac{q}{kT} I dV$$

$$\therefore r_{d} = \frac{dV}{dI} = \frac{kT}{qI}$$

(1.9)

Now kT/q is approximately 25 mV at room temperature, hence the dynamic slope resistance can be expressed as

$$r_{\rm d} \approx \frac{0.025}{I} \Omega \quad (I \text{ in A})$$

(1.10)

Exponentials and logarithms in equations are difficult to handle.

This approach is used to simplify the subsequent mathematics which then becomes linear. or

$$r_{\rm d} \approx \frac{25}{I} \Omega$$

(*I* in mA) (1.11)

This latter presentation (Equation 1.11) is the result which is normally used and clearly shows the dependence of slope resistance on the d.c. bias current (*I*).

#### Exercise 1.2

Calculate the dynamic slope resistance ( $r_d$ ) of a diode, forward biased at the following currents:  $10 \mu A$ ,  $500 \mu A$ , 1 mA, 5mA. [Answer:  $2.5\text{k}\Omega$ ,  $50\Omega$ ,  $25\Omega$  and  $5\Omega$  respectively.]

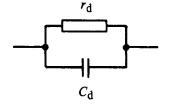

We are now able to represent the small-signal behaviour of a forward biased diode by its slope resistance ( $r_d$ ) and, for high frequencies, include a parallel capacitance ( $C_d$ ) representing its diffusion capacitance.

How small is a small signal? The trite answer is—vanishingly small, to preserve  $r_d$  as a constant slope over the signal excursion around the bias level. For other than zero amplitude signals, the slope of the characteristic changes,  $r_d$ , is not constant and the voltage/current relationship is nonlinear. It is customary, however, to use the model described above assuming a constant  $r_d$  but at the same time recognizing that nonlinearity (or distortion) increases with signal amplitude.

In Chapter 3 this small-signal representation of diode behaviour is developed to enable us to characterize the rather more complex bipolar junction transistor.

In the reverse bias region  $r_d$  is very high and may be omitted. We are then left with the diode being represented by its reverse bias transition capacitance  $(C_t)$  which degenerates, at low frequencies, to an open circuit.

#### Worked Example 1.1

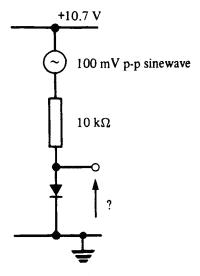

The circuit of Fig. 1.4 shows a diode, a 10 k $\Omega$  resistor and an a.c. voltage source connected in series across a 10.7 V d.c. supply. If the a.c. voltage source delivers a sinewave of 100 mV peak-to-peak amplitude, calculate the voltage across the diode.

Fig. 1.4

*Solution.* The diode is in forward conduction since its arrow is in the direction of conventional current flow from positive to negative. Therefore, using the 0.7 V d.c. model, the average d.c. voltage across the diode is 0.7 V.

The d.c. voltage across the resistor is (10.7–0.7) V=10 V and, since the resistor value is 10 k $\Omega$ , the d.c. current through the diode is 1 mA.

The slope resistance of the diode is given by

$$r_{\rm d} \approx \frac{25}{I} \Omega(I \text{ in mA})$$

(25  $\Omega$  in this case).

For the a.c. signal, the resistor and the slope resistance of the diode form a potential divider giving an a.c. diode voltage of

$$\frac{25 \Omega}{25 \Omega + 10 \text{ k}\Omega} \times 100 \text{ mV} \approx 250 \,\mu\text{V} \text{ peak-to-peak}$$

Therefore the diode voltage is an approximate sinewave of 250  $\mu$ V peak-to-peak amplitude superimposed on a d.c. level of approximately 0.7 V.

#### **Breakdown diodes**

Although reverse breakdown of a diode is a departure from its rectifying action, practical use can be made of this effect. If a diode is supplied with reverse current from a current source with a sufficiently high voltage capability (>|BV|), the diode voltage is substantially constant over a wide range of current. The diode, now used as a breakdown (or Zener) diode, has wide application in providing stabilized voltages ranging from 2.7 V to 200 V or more.

A breakdown diode is characterized by its nominal breakdown voltage and the reciprocal of the reverse characteristic in the reverse region, the dynamic slope resistance ( $r_z$ ). An ideal breakdown diode has a well specified breakdown voltage and zero slope resistance giving a constant reverse voltage (in breakdown) independent of temperature and reverse current. In practice, however, the breakdown characteristic is curved in the low reverse current region and the reverse current supplied must be of sufficient magnitude to ensure that the breakdown diode operates beyond the knee of the characteristic in a region of low slope resistance. Further, even beyond the knee, slope resistance varies with reverse current and depends on the nominal breakdown voltage and temperature. Manufacturers' data should be consulted for accurate figures. In general,  $r_z$  is a minimum for devices with a |BV| of approximately 6 V and operated at high reverse currents. At lower currents and for both higher and lower values of |BV|,  $r_z$  increases.

The temperature coefficient of breakdown voltage depends on both the nominal breakdown voltage and on the reverse current. Below approximately 5 V the temperature coefficient is negative and above is positive. This is because different breakdown mechanisms occur for low and high breakdown voltages. At approximately 5 V both mechanisms are present and produce a zero temperature coefficient.

The device rating which is important for a breakdown diode is the power dissipation, the product of reverse current and breakdown voltage.

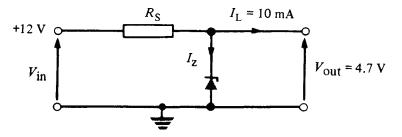

Using a 400 mW breakdown diode and a resistor, design a simple stabilized voltage supply capable of providing 10 mA at 4.7 V from an existing +12 V supply.

This is an example of the application of the principle of superposition. The d.c. conditions (with a.c. sources turned down to zero) are evaluated first, then the a.c. behaviour is considered in isolation. The overall result is the additive superposition of the two cases since the a.c. signals are small and a linear model is used for the diode.

Breakdown diodes are often referred to as **Zener** diodes and the breakdown voltage as the Zener voltage.

Voltage regulators are covered in detail in Chapter 9.

The nominal breakdown voltage is subject to a tolerance, e.g. 5.1 V, ±5%.

Avalanche and Zener breakdown mechanisms are described in Chapter 2 of Sparkes.

**Design Example 1.1**

Note the symbol for a breakdown diode is similar to that of a normal diode but with a tail on the cathode bar. In reverse conduction a breakdown diode is connected with the cathode positive.

Fig. 1.5

Solution. The series resistor ( $R_s$ ) limits the breakdown diode current which, although dependent on load current ( $I_L$ ), allows the breakdown diode to develop a substantially constant output voltage (Fig. 1.5).

The output voltage is specified as 4.7 V; therefore a breakdown diode with a |BV| of 4.7 V should be used.

Allow a minimum reverse current  $(I_z)$  of say 10 mA to flow through the breakdown diode, thus ensuring a reasonably low  $r_z$ .

The total current through  $R_S$  is  $(I_L+I_z)=20$  mA and the voltage across  $R_S$  is  $(V_{in}-V_{out})=(12-4.7)=7.3$  V. Therefore

$$R_{\rm S} = \frac{7.3}{0.02} = 365\,\Omega$$

This is not a preferred value (see Appendix A), the nearest being 330  $\Omega$  and 390  $\Omega$  in the E12 series. The lower of these two values should be selected since the extra current reduces the slope resistance but it is essential to check that the power rating (400 mW) of the breakdown is not exceeded.

The power dissipation= $BV \times I_{z(max)}$ .  $I_z$  is a maximum if the external load current were to fall to zero, i.e.

$$I_{\text{z(max)}} = \frac{V_{\text{in}} - V_{\text{out}}}{R_{\text{s}}} = \frac{12 - 4.7}{330} = 22 \text{ mA}$$

Therefore the dissipation is  $(4.7 \times 0.022)=104$  mW which is less than the rating of the breakdown diode. The design, with  $R_s=330$   $\Omega$ , is satisfactory.

#### Exercise 1.3

The superimposed a.c. behaviour of the circuit.

It is not always appropriate to

value. On occasion, the higher

value may be the more suitable.

select the nearest preferred

(or lower) adjacent preferred

For the circuit of the preceding design example, if the 12 V supply is liable to variations of  $\pm 0.5$  V, calculate the voltage variation of the derived 4.7 V supply, given that the slope resistance of the breakdown diode is 40  $\Omega$ .

[Answer: ±54 mV. This illustrates the ripple reduction of the simple voltage stabilizer.]

#### The bipolar junction transistor

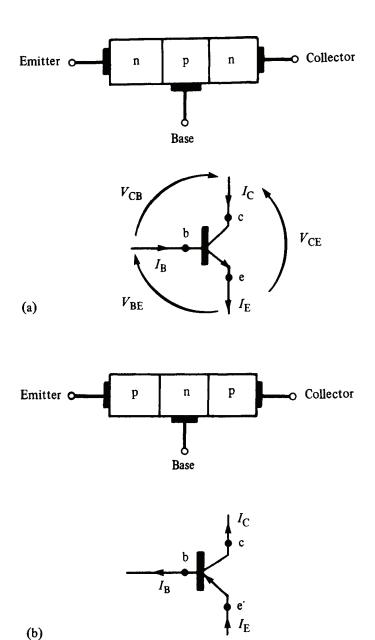

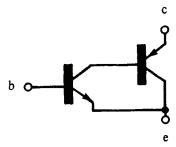

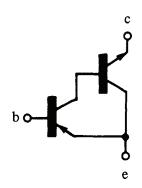

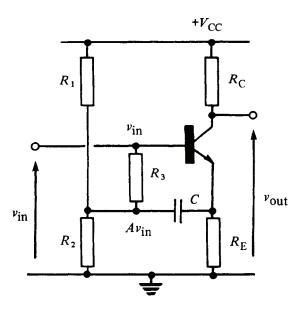

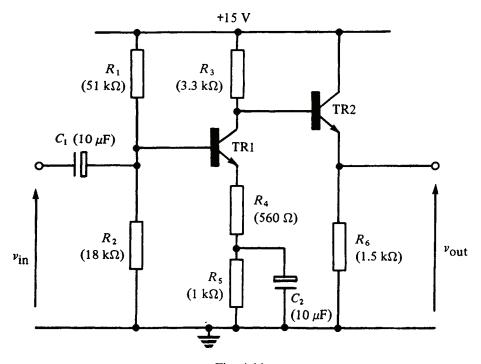

A bipolar junction transistor (BJT) can be represented by a two-diode n-p-n or p-n-p structure as shown in Fig. 1.6, which also defines the symbols and the three terminals of the devices (emitter, base and collector) plus the terminal voltages and currents.

The arrow on the emitter lead serves two purposes. First, it distinguishes between the collector and emitter terminals which normally cannot be interchanged. Second, the arrow denotes the direction of conventional current flow through the device,

The direction of conventional current flow is that of positive charge carriers.

Fig. 1.6 Schematic structures, symbols, voltages and currents for (a) n-p-n and (b) p-n-p BJTs.

providing discrimination between the symbol for the n-p-n transistor and its p-n-p counterpart.

Figure 1.6 shows that for both n-p-n and p-n-p transistors,

$$I_{\rm E} = I_{\rm C} + I_{\rm B} \tag{1.12}$$

where  $I_E$ ,  $I_C$  and  $I_B$  are the emitter, collector and base currents, respectively.

Fig. 1.7

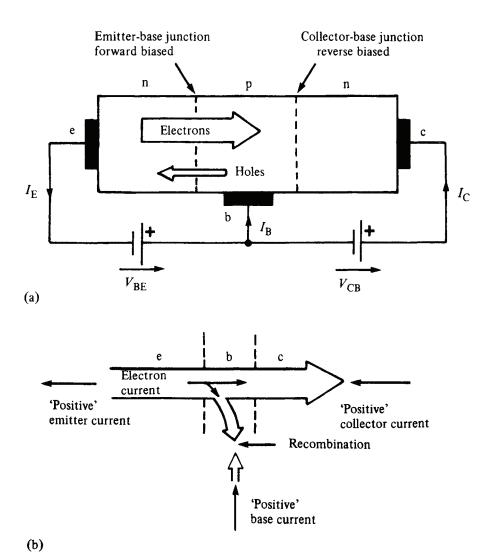

#### BJT operation

In normal operation, the emitter-base junction is forward biased and the collector-base junction reverse biased. For the schematic n-p-n structure of Fig. 1.7a, electrons are injected from the n-type emitter into the base and, at the same time, holes are injected from base to emitter. To improve device efficiency, the doping level of the base region is made much lower than that of the emitter; essentially only electron current flows across the emitter-base junction with the injection level controlled (exponentially) by the base-emitter forward bias potential ( $V_{\rm BE}$ ), as

$$I_{\rm E} \propto \exp\left(\frac{qV_{\rm BE}}{kT}\right)$$

(1.13)

Electrons injected from the emitter become minority carriers in the p-type base and, since the collector-base junction is reverse biased, these minority carriers which cross the base by diffusion are swept across the collector-base transition region. Because the electrons spend a finite time in transit through the base region, some recombine with holes; the holes involved in this recombination are replaced by positive charge flow into the base (via its connection to the bias source) resulting in a base current ( $I_B$ ).

Operation of the transistor may be summarized by reference to Fig. 1.7b. The electron current at the collector is almost all of the current injected from the emitter diminished only by that lost as base current due to recombination. This consideration neglects hole injection from base to emitter and hole leakage from collector to base, both of which contribute to device current and hence degrade total efficiency.

The term **bipolar** is applied to junction transistors of the type described above since two types of charge carrier (holes and electrons) are involved in the operation of the device. Unipolar, or field-effect, transistors (see Chapter 7) rely on only one type of carrier.

In this text leakage currents are ignored since, for silicon devices, they are significant only at elevated temperatures. (For consideration of leakage currents in devices and their effect on circuit design the reader should consult more advanced texts.)

#### BJT current gain

The fraction of the emitter current appearing as collector current is given the symbol  $\alpha$ , the **common-base** current gain of the transistor—common-base since the base terminal is common to both the input port (emitter-base) and the output port (collector-base). Thus

$$\frac{\text{Collector current}}{\text{Emitter current}} = \frac{I_{\text{C}}}{I_{\text{E}}} = \alpha \tag{1.14}$$

The ratio  $(\beta)$  of the collector current to base current can be determined by combining Equations 1.12 and 1.14, as follows. Since

$$I_{\rm E} = I_{\rm C} + I_{\rm B}$$

$$I_{\rm B} = (1 - \alpha)I_{\rm E}$$

$$\frac{\text{Collector current}}{\text{Base current}} = \frac{I_{\rm C}}{I_{\rm B}} = \frac{\alpha}{1 - \alpha} = \beta$$

(1.15)

$\beta$  is termed the common-emitter current gain, input at the base, output at the collector. The symbols  $h_{\text{fb}}$  and  $h_{\text{fe}}$  are widely used as alternatives to  $\alpha$ . and  $\beta$  (see Appendix C).

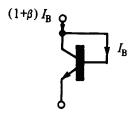

Rearrange Equation 1.15 to provide an expression for  $\alpha$  in terms of  $\beta$  and hence determine a for a BJT whose measured  $\beta$  is 100. [Answer:  $\alpha = \beta/(1+\beta) \approx 0.99$ ]

For most bipolar transistors,  $\alpha$  lies within the range 0.97 to 0.998, giving a corresponding  $\beta$  range of approximately 30 to 500. In other words, for a typical device, perhaps 1/100 of the emitter current is lost by recombination in the base. Since  $\alpha$  is very close to unity it is often convenient to use the approximation

Transit time and recombination are reduced by making the base region very thin.

BJT leakage current is discussed in the more expansive treatment by Millman and Grabel (1987), Chapter 3.

Why bipolar?

Many different symbols are used for various definitions of common-emitter current gain  $(\beta, \beta_{\text{F}}, \beta_{\text{o}}, \textbf{h}_{\text{fe}}, \textbf{h}_{\text{FE}}$  and so on). At this stage, it is unnecessary to distinguish between them.

#### Exercise 1.4

$$I_{\rm C} \approx I_{\rm E}$$

(1.16)

$$\approx I_{\rm s} \exp \frac{qV_{\rm BE}}{kT} \tag{1.17}$$

where  $I_s$  is a saturation or leakage current.  $I_C$  is nominally independent of the collector-base reverse bias ( $V_{CB}$ ).

Although we have considered injection from emitter into base with the emitter as input, it is relevant to note, particularly when dealing with the common-emitter configuration, that the controlling input voltage is still the base-emitter voltage  $(V_{\rm BE})$  but in this case the input (base) current is only recombination current. If base current is supplied to the device, the base-emitter voltage and consequent emitter-to-base injection is forced to a level dictated by the base current and the current gain  $(\beta)$ .

What about p-n-p transistors?

This description of BJT operation has referred only to the n-p-n structure. A p-n-p device operates in exactly the same way except that holes are now the predominant charge carriers and the polarity of applied voltage and the directions of the terminal currents are reversed.

#### BJT characteristics

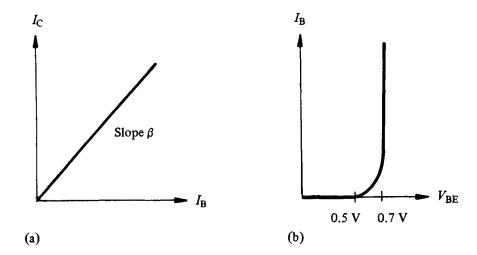

The input parameters for a BJT in common-emitter are the base-emitter voltage  $(V_{\rm BE})$  and the base current  $(I_{\rm B})$ ; the output parameters are the collector-emitter voltage  $(V_{\rm CE})$  and the collector current  $(I_{\rm C})$ . The interrelation of these parameters can be presented graphically as device characteristics.

Current transfer characteristic: The current transfer characteristic of Fig. 1.8a,  $I_C$  plotted against  $I_B$ , is a graphical presentation of the common-emitter current gain  $(\beta)$ . While this characteristic is relevant for a specific measured device, the very large variation (or spread) of  $\beta$  from one device to another, typically 10:1 even within a device type, limits general application. In representing current transfer by a straight line of slope  $\beta$  passing through the origin, two assumptions have been made; that leakage current is negligible and that  $\beta$  is a constant. Neither is true in practice; leakage currents can be significant at high temperatures and  $\beta$  falls off at both low and high currents, peaking to a maximum in the 1 to 10mA range for low-power BJTs and at somewhat higher currents for high-power devices.

Input characteristic: A plot of  $I_{\rm B}$  versus  $V_{\rm BE}$  interrelates the two input parameters as the device input characteristic, shown in Fig. 1.8b. The exponential nature of the characteristic, expected from Equation 1.17 if  $\beta$  is assumed constant, is very similar to that of a diode and a constant voltage drop of 0.7 V is a satisfactory approximation to the  $V_{\rm BE}$  of a conducting silicon transistor. This figure is widely used in the d.c. design of BJT circuits.

The same  $V_{\rm BE}$  increments for a doubling of  $I_{\rm C}$  and  $I_{\rm B}$  (17.3 mV), and approximately 58 mV for a factor of ten times change in current, apply to the BJT. Also, the temperature coefficient of  $V_{\rm BE}$  is approximately -2 mV/°C. All devices are not identical and  $V_{\rm BE}$  is subject to a spread (typically  $\pm 50$  mV) for a particular device type.

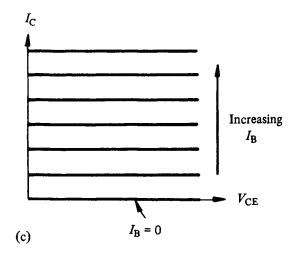

Output characteristic: The graphical relationship between the output parameters,  $I_{\rm C}$  and  $V_{\rm CE}$  with  $I_{\rm B}$  as control, provides the output characteristic shown in idealized form in Fig. 1.8c. To a first approximation it is valid to assume that the collector

Fig. 1.8 n-p-n BJT characteristics: (a) current transfer, (b) input, (c) output (idealized).

current is determined only by  $I_{\rm B}$  and  $\beta$  ( $I_{\rm C}=\beta\times I_{\rm B}$ ) and is independent of  $V_{\rm CE}$ ; the BJT is therefore a current-controlled current source. However, the practical characteristic (Fig. 1.9) has non-zero slope implying that the collector is not a perfect current source (this is discussed further in Chapter 3). Also, curvature of the characteristic close to the  $I_{\rm C}$  axis indicates that  $V_{\rm CE}$  cannot fall to zero (except for zero current) as there must be at least a minimal residual voltage, termed the collector-emitter saturation voltage  $V_{\rm CE(sat)}$ , which is typically 100 mV although it does depend on  $I_{\rm C}$ ,  $I_{\rm B}$  and temperature.

It is fallacious to regard the BJT as a variable resistor controlled by  $I_B$  or  $V_{BE}$ . It is a controlled current source.

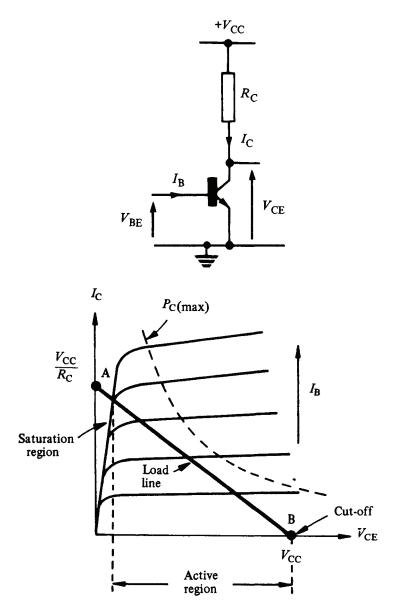

Fig. 1.9 Output characteristic with load line superimposed.

#### Load line

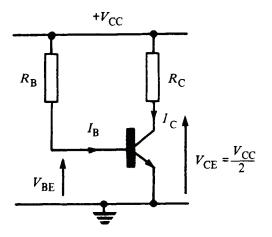

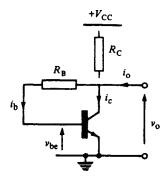

Consider a common-emitter BJT with the collector connected via a collector load resistor ( $R_{\rm C}$ ) to a positive voltage supply ( $V_{\rm CC}$ ) as shown in Fig. 1.9. Summing voltages gives

$$V_{\rm CE} + I_{\rm C}R_{\rm C} = V_{\rm CC} \tag{1.18}$$

or

$$I_{\rm C} = \frac{V_{\rm CC}}{R_{\rm C}} - \frac{V_{\rm CE}}{R_{\rm C}} \tag{1.19}$$

distinguish them from device terminal voltages, e.g.  $\boldsymbol{V}_{\text{C}}$  is the collector voltage with respect to earth while  $\boldsymbol{V}_{\text{CC}}$  is the collector supply voltage, also with respect to earth.

Supply voltages are usually

given a double subscript to

Equation 1.19 can be superimposed on the output characteristic as a straight line of slope -1/ $R_{\rm C}$  intersecting the  $I_{\rm C}$  axis at  $V_{\rm CC}/R_{\rm C}$  (point A) and the  $V_{\rm CE}$  axis at  $V_{\rm CC}$  (point B). This line is called the **load line** which, given  $V_{\rm CC}$  and  $R_{\rm C}$ , describes all possible operating conditions of the circuit.

Let us travel along this line and observe the conditions which apply. Starting at point B, for which  $I_C$ =0 and  $V_{CE}$ = $V_{CC}$ , the BJT is said to be cut-off or in the OFF state. This is achieved by open-circuiting the base terminal ( $I_B$ =0) or by making  $V_{BE}$ =0 V (for an n-p-n transistor).

If  $I_B$  (or  $V_{BE}$ ) is raised slightly above zero, the BJT starts to conduct ( $I_C>0$ ) and enters the normal active region with the emitter-base junction forward biased and the collector-base junction reverse biased. Progressive increase of  $I_B$  (or  $V_{BE}$ ) increases the collector current with a corresponding  $I_CR_C$  reduction in  $V_{CE}$  (Equation 1.18) and the operating point moves along the load line towards point A.

As the collector voltage falls, the reverse bias on the collector-base junction reduces reaching zero bias when the collector and base voltages are equal. We are now at the other limit of the active region and about to enter the saturation region which is defined as the collector-base junction being forward biased. The approximately linear relationship between  $I_{\rm C}$  and  $I_{\rm B}$  no longer applies in this region and the curvature of the output characteristic limits  $I_{\rm C}$  to a maximum of

$$I_{\text{C(ON)}} = \frac{V_{\text{CC}} - V_{\text{CE(sat)}}}{R_{\text{C}}} \tag{1.20}$$

where  $V_{\text{CE(sat)}}$  has been described earlier. The BJT is now said to be fully saturated or ON.

#### BJT ratings

In common with all electronic components, voltage current and power levels in a BJT must not be exceeded if the device is to be operated reliably. Manufacturers' specified ratings include maximum collector and base current levels, the minimum breakdown voltages (B $V_{\rm CB}$  and B $V_{\rm BE}$ ) of the collector-base and emitter-base junctions as well as a corresponding limit on collector-emitter voltage B $V_{\rm CE}$ . For silicon BJTs, |B $V_{\rm BE}$ | is usually guaranteed to be not less than 6 V while |B $V_{\rm CB}$ | can range from 10 V to several hundreds of volts.

The maximum power dissipation ( $P_D$  or  $P_{C(max)}$ ), defined as the product of collector current and collector-emitter voltage, restricts operation to an area on the output characteristic bounded by a hyperbola (Fig. 1.9).  $P_{C(max)}$  is usually quoted for temperatures up to 25 °C. Above this temperature the allowable dissipation is reduced by a figure (in mW/°C) which depends on the thermal properties of the device package.

#### Integrated circuits

An integrated, or monolithic, circuit is a small chip of silicon (typically between 1 mm and 5 mm square and 0.25 mm thick) containing hundreds of thousands of components and capable of performing tasks ranging from simple combinational logic or amplification to very complex functions such as those required in microprocessors.

The distinction is made here between saturation ( $V_{CB}$ <0 for an n-p-n BJT) and the fully saturated or ON state.

Morant (1990) and Chapter 5 of Sparkes (1987) are comprehensive references.

A variety of units of length are in common use with respect to integrated circuit dimensions. Millimetres (mm,  $10^{-3}$  m) are the largest used; others are the micrometre (1  $\mu$ m= $10^{-6}$  m), the angstrom (1 Å= $10^{-10}$  m) and the **thou** or **mil** (one thousandth of an inch or  $2.5 \times 10^{-5}$  m).

The first commercial production of integrated circuits was in 1961.

This step increasingly is being replaced by ion implantation where dopant ions, accelerated through a very high potential, penetrate the silicon crystal surface (see Morant (1990), Chapter 3).

To date, Integrated inductors have not been fabricated successfully.

The + in p<sup>+</sup> signifies heavily doped, high-conductivity material.

Chips are not manufactured individually but are processed, many thousands at a time, on circular silicon slices (wafers), 50 to 150mm in diameter. When the processing and testing of wafers are complete, they are split into individual chips prior to packaging and final testing.

#### The planar process

The feasibility of making integrated circuits is due entirely to the planar process which, as its name suggests, involves processing only on one side of a silicon wafer. This comprises three fundamental operations—oxidation, diffusion and metallization.

Oxidation The surface of silicon is readily oxidized at elevated temperatures to form a thin insulating layer. Using photographic resist and selective etching techniques, a **window** is created in the oxide exposing the desired area of the silicon surface.

*Diffusion* If an impurity (usually boron for p-type, phosphorus for n-type) in gaseous form is passed over the heated silicon, it diffuses into the exposed silicon with the rest of the surface being protected by the oxide mask. Impurity diffusion occurs both vertically and laterally forming a junction under the protective oxide. Successive masking plus p-type and n-type diffusions into the silicon produce vertical diode and BJT structures.

*Metallization* When all diffusions are complete and the device structures have been formed, they are connected in circuit configuration by coating the surface with a thin film of aluminium and then etching away (as in printed circuit fabrication, but on a microscopic scale) all except the interconnection pattern.

Using the planar process, it is possible to fabricate many types of electronic components such as diodes, BJTs, field-effect transistors, resistors and very low-value capacitors.

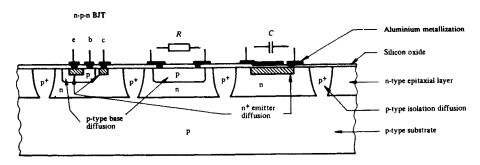

Figure 1.10 illustrates the structures of a BJT, a resistor and a capacitor all isolated from each other. Isolation is essential in integrated circuits to minimize unintended interaction between components and is achieved in the following manner. The starting point is usually a p-type doped silicon wafer or substrate on which is grown an 'epitaxial' crystalline layer of n-type silicon. A deep p+ diffusion through the n-type layer joins with the substrate forming n-type wells which are isolated from each other by reverse biasing their junctions with the substrate (the

Fig. 1.10 Section (not to scale) of an isolated integrated BJT, resistor and capacitor.

substrate is connected to the most negative potential in the circuit). Isolated bipolar transistors, resistors and capacitors are fabricated in these wells.

#### Integrated BJTs

An integrated n-p-n planar BJT (see Fig. 1.10) is fabricated by performing a p-type base diffusion followed by an n<sup>+</sup> emitter diffusion: a combination of time, temperature and dopant concentration determines impurity profiles. The n<sup>+</sup> diffusion is also applied to the collector contact area since the aluminium metallization is a p-type (Group 3) impurity and, otherwise, would create an unwanted rectifying junction at the contact.

In addition to the diffusion parameters mentioned, the performance of a planar BJT is determined by its surface geometry, i.e. by the masks. If two transistors have identical geometries and are fabricated adjacent to each other (perhaps within 0.1 mm) they are subject to almost identical processing conditions and are closely matched in terms of current gain ( $\beta$ ) and  $V_{\rm BE}$  for a given  $I_{\rm C}$ . Since the transistors are in very close thermal proximity, their parameters remain closely matched over a wide range of temperature. This feature is called (thermal) tracking. In practice, integrated BJTs have  $V_{\rm BE}$ s matched to within 5mV with less than 10  $\mu$ V/°C drift and their  $\beta$ s are matched to within ±10%.

It is rather more difficult to realize p-n-p bipolar transistors in an essentially n-p-n process which is controlled to yield adequate values of  $\beta$  and breakdown voltages for n-p-n devices. It is possible to use the substrate in a vertical p-n-p structure combining the substrate as collector, the n-type well as base and the p-type base diffusion as emitter. This structure has the disadvantages that the base region is rather wide, giving a low value of  $\beta$ , and that the substrate (the p-n-p collector) must be connected to the most negative circuit potential in order to achieve isolation for other devices.

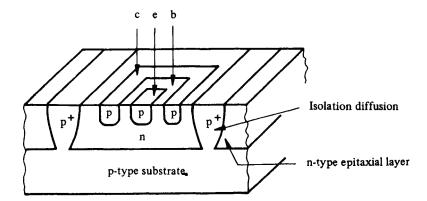

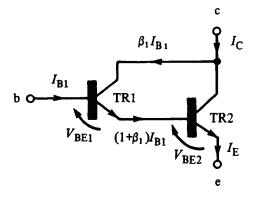

A lateral structure for a p-n-p transistor (Fig. 1.11) can be created by diffusing both the p-type collector and emitter at the same time (the base diffusion for n-p-n devices). This lateral p-n-p transistor exhibits poor and variable performance owing to mask and processing tolerances;  $\beta$ s are often as little as 10. The current gain of a lateral p-n-p transistor can be enhanced by compounding it with a high- $\beta$  n-p-n transistor as discussed in Chapter 4.

Fig. 1.11 Structure of a lateral p-n-p transistor (not to scale). The oxide layer and metallization have been omitted.

Millman and Grabel (1987), pp. 191–193 provide more information on integrated diodes.

See Sparkes (1987), Chapter 5.

To improve compactness, highvalued diffused resistors have a meandering or snake-like geometry. Special allowance, over and above the ohms per square, must be made for corners and end contacts.

#### Exercise 1.5

Determine the length of a straight, base-diffused integrated resistor of value  $8 \text{ k}\Omega$  if the sheet resistivity of the base diffusion is 200  $\Omega$  per square. The resistor width is 25  $\mu$ m.

[Answer: 1 mm]

#### Exercise 1.6

Calculate the aspect ratio of a base-diffused resistor of value 50  $\Omega$ . The sheet resistivity of the base diffusion is 200  $\Omega$  per square.

[Answer: 1:4 (short and wide)]

Owing to process variations, the absolute value of an integrated resistor is subject to wide tolerance (typically up to  $\pm 20\%$ ) but, as with integrated BJTs, resistors

#### Integrated diodes

A junction diode with a relatively high breakdown voltage ( $\approx$ 30 V) can be realized by using the collector-base junction of an integrated BJT; the emitter diffusion is unnecessary. Alternatively, the emitter-base junction ( $|BV|\approx$ 7 V) may be used for low-voltage or breakdown diode (Zener) applications.

Neither of these devices matches the input characteristic of a BJT which is more closely approximated by the emitter-base junction with the collector shorted to the base. This diode-connected transistor has wide application in integrated circuits both linear (see Chapter 5) and digital.

#### Integrated resistors

The ohmic value of an integrated resistor is realized by carefully defining the surface geometry of a base (or emitter) diffusion which has a controlled depth and resistivity. Isolation of the resistive region is provided by reverse biasing its junction with the collector well (or base region). The emitter diffusion with its low resistivity is preferred for low-value resistors (10  $\Omega$  to 1 k $\Omega$ ) while the base diffusion is appropriate for higher-valued resistors (up to 50 k $\Omega$ ).

Integrated resistor values are calculated using the concept of sheet resistivity as follows. Resistive material has a bulk resistivity ( $\rho$ , in  $\Omega$ -cm) which relates resistance (R) to the resistor dimensions length ( $\ell$ ), width (w) and thickness (t).

$$R = \rho \frac{\ell}{wt} \tag{1.21}$$

If a square geometry  $(\ell=w)$  is considered, the resistance between opposite faces of the square is

$$R = \rho \frac{\ell}{\ell t} = \frac{\rho}{t} \equiv R_{\rm S} \tag{1.22}$$

where  $R_S$  is defined as the sheet resistivity (in  $\Omega$  per square), independent of the size of the square.

A resistance of value ( $n \times R_S$ ) is achieved by a surface shape which is n squares in length, an aspect ratio of n: 1 (long and thin). Alternatively, a resistance of less than  $R_S$  has an aspect ratio of less than unity (short and wide). Theoretically, the actual width of the resistor is unimportant since it is only the aspect ratio that counts (for a given  $R_S$ ). In practice, because of photographic limitations, resistor widths are usually made no less than 0.025 mm (1 mil).

fabricated in close proximity to each other exhibit almost identical departures (within  $\pm 1\%$ ) from their design values. Also, although integrated resistors vary in value with temperature ( $\pm 0.2\%$ /°C), physically adjacent resistors have the same temperature coefficient and are subject to the same temperature. The effect of these features is that, while the values of individual resistors are subject to temperature and tolerance variations, ratios of resistor values correspond closely to their design geometries and remain constant with temperature.

A major problem with integrated resistors is the area which they expend; a 50 k $\Omega$  resistor (base-diffused, 50  $\mu$ m width) will occupy an area of 0.625 mm² compared with around 0.05 mm² for a typical low-power BJT. Imperfections in the crystal structure occur randomly over the area of a silicon wafer and, since each imperfection may result in a faulty device (and chip), the area of each chip should be minimized in order to maximize the final yield of functional chips. With chip area at a premium, total chip resistance is limited to an absolute maximum of around 500 k $\Omega$  but, more important, special circuit design techniques (see Chapter 5) are used to reduce chip resistance with scant regard for transistor count. This is a total reversal of the economics of discrete component circuit design in which the cost of a transistor is typically five to ten times that of a resistor, whatever its ohmic value.

Thin- and thick-film resistors are also used in specialized, precision circuits.

#### Integrated capacitors

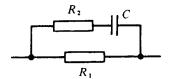

We have seen, earlier in this chapter, that a reverse biased p-n junction exhibits a transition capacitance. This may be used in integrated circuits to realize capacitors but there are several disadvantages. The value of transition capacitance is dependent on reverse voltage and such a capacitor is polarized; the junction must be reverse biased. Also, the capacitance per unit area is very small.

An alternative approach is to create a non-polarized capacitor with electrodes formed by the low-resistivity emitter diffusion and aluminium metallization separated by a very thin (500 Å) silicon oxide dielectric (see Fig. 1.10). This structure also has a very low capacitance per unit area (in the order of 400 pF/mm²) and, for this reason, total chip capacitance is usually limited to a maximum of approximately 100 pF. Therefore, it is impossible to integrate capacitors with nanofarad values and integrated circuit design techniques avoid, wherever possible, the use of capacitors. Essential high-valued capacitors must be discrete components external to the integrated circuit package. However, it is possible to accommodate the internal 3–10 pF compensating capacitor commonly used to stabilize operational amplifiers against oscillation.

This structure is called Metal Oxide Semiconductor (or MOS).

At this stage we are concerned primarily with bipolar techniques but it is essential to realize that MOS transistors are the key to the integration of very complex circuits. They are described in Chapter 7.

#### Economic forces

Despite a high utilization of computer aids, the design of an integrated circuit is a lengthy and expensive procedure. In order that the integrated circuits themselves are inexpensive, they must be mass-produced and satisfy a wide market. Although it is possible to design integrated circuits to meet almost every conceivable specification, manufactured in small numbers their cost is prohibitive, outweighing the advantages of small size, low weight, high performance and reliability. However, custom development of special integrated circuits sometimes proves cost-effective to achieve security of a product plus enhanced reliability, particularly for space and military equipment.

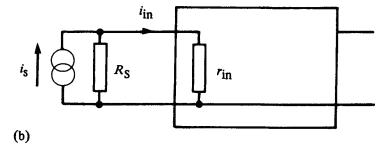

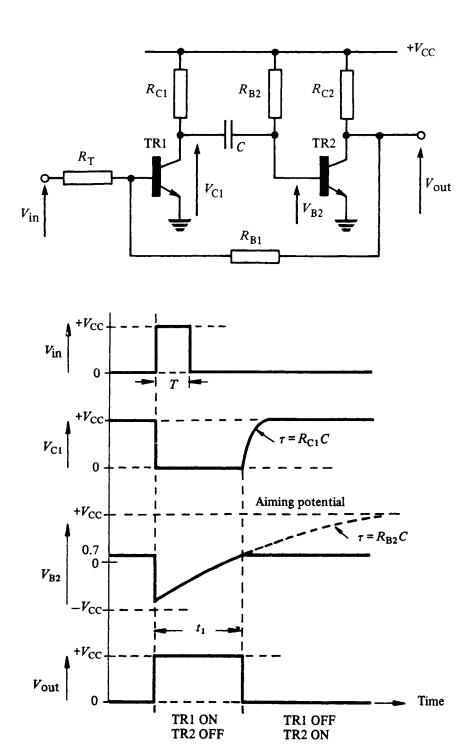

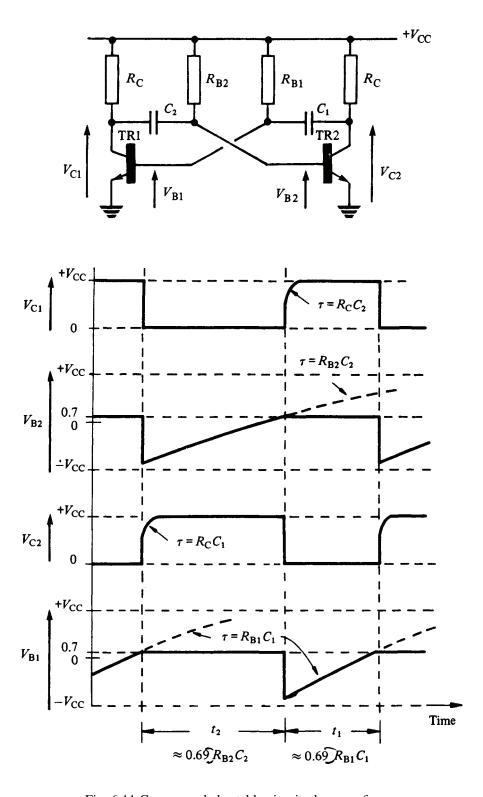

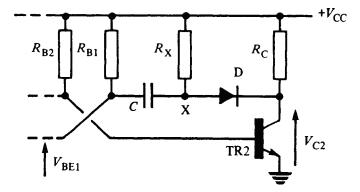

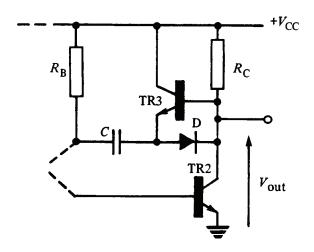

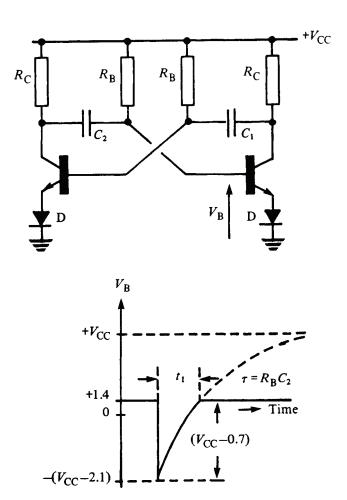

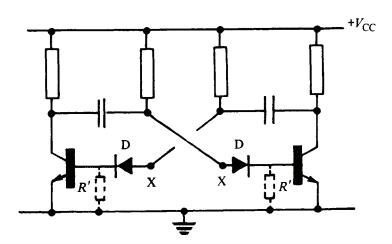

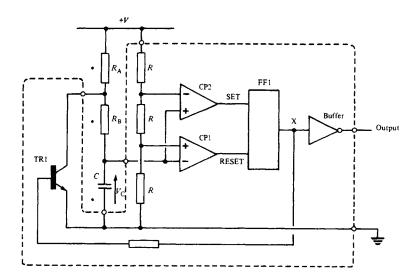

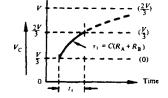

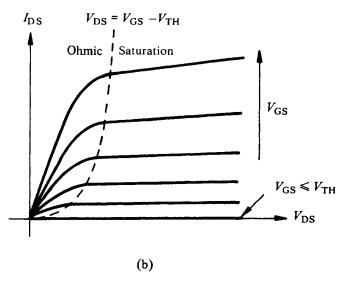

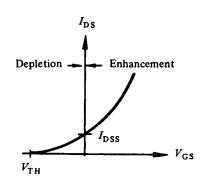

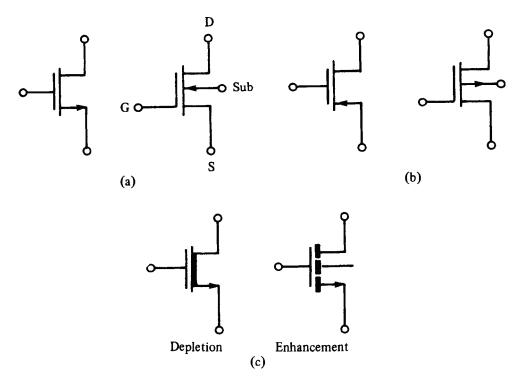

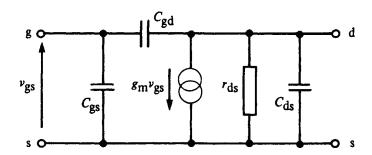

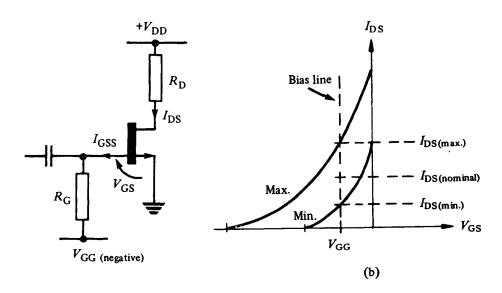

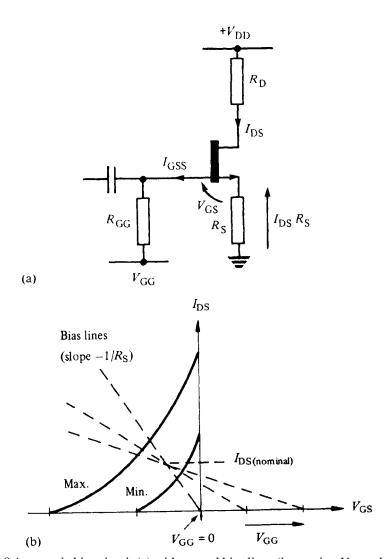

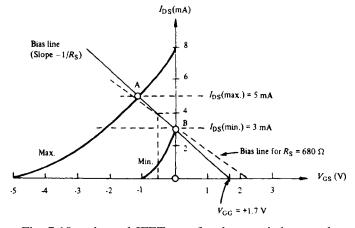

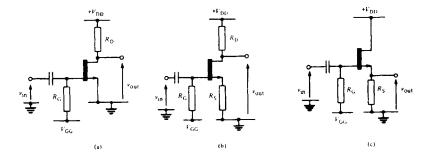

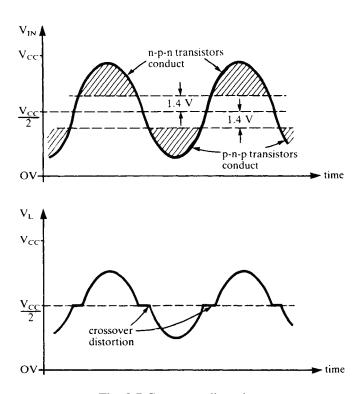

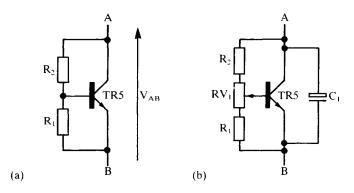

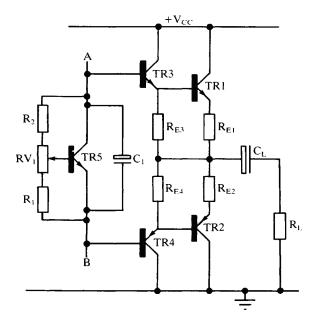

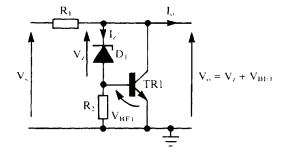

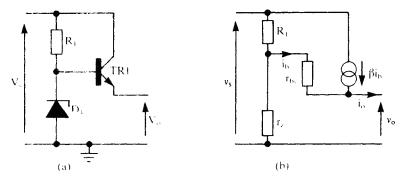

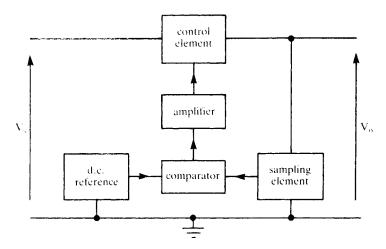

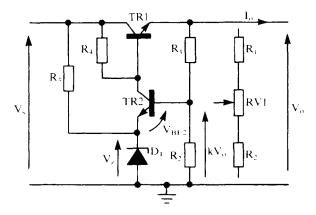

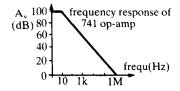

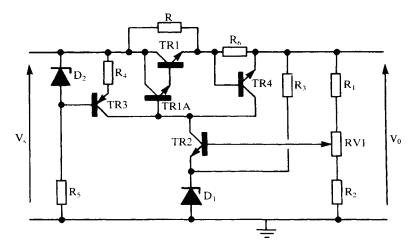

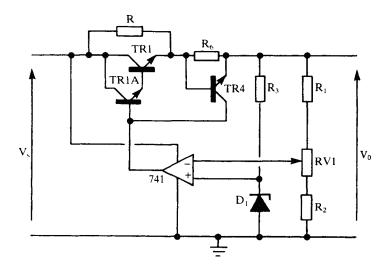

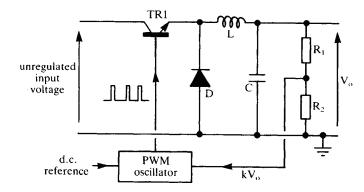

Commercially available integrated circuits either provide a single function to