# μPD8279 PROGRAMMABLE KEYBOARD/ DISPLAY INTERFACE

#### Description

The  $\mu$ PD8279 is a programmable keyboard and display input/output device providing the user with the ability to display data on alphanumeric segment displays or simple indicators. The display RAM can be programmed to function as a 16 x 8-bit or dual 16 x 4-bit memory and can be loaded or read by the host processor. The display can be loaded with right or left entry with an auto-increment of the display RAM address.

The keyboard interface provides a scanned signal to a 64 contact key matrix expandable to 128. General sensors or strobed keys may also be used. Keystrokes are stored in an 8 character FIFO and can be either 2 key lockout or N key rollover. Keyboard entries generate an interrupt to the processor.

#### **Features**

- ☐ Programmable by processor

- $\square$  32 hex or 16 alphanumeric displays

- ☐ 64 expandable to 128 keyboard

- ☐ Simultaneous keyboard and display

- □ 8 character keyboard—FIFO

- ☐ 2 key lockout or N key rollover

- □ Contact debounce

- ☐ Programmable scan timer

- ☐ Interrupt on key entry

- $\square$  Single +5 V ±10% power supply

- Fully compatible with 8080A, 8085A, μPD780 (Z80<sup>®</sup>)

#### **Ordering Information**

| Part<br>Number | Package<br>Type    | Max Frequency of Operation |

|----------------|--------------------|----------------------------|

| μPD8279C-2     | 40-pin plastic DIP | 5 MHz                      |

| μPD8279C-5     | 40-pin plastic DIP | 3 MHz                      |

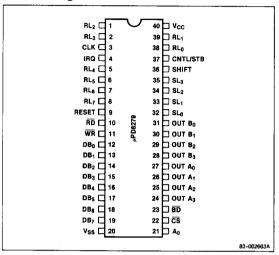

#### **Pin Configuration**

#### Pin Identification

| No.               | Symbol                                    | Function             |

|-------------------|-------------------------------------------|----------------------|

| 1,2,5,6,7,8,38,39 | RL <sub>0</sub> -RL <sub>7</sub>          | Return lines         |

| 3                 | CLK                                       | Clock input          |

| 4                 | IRQ                                       | Interrupt request    |

| 9                 | RESET                                     | Reset input          |

| 10                | RD Read input                             |                      |

| 11                | WR Write input                            |                      |

| 12-19             | DB <sub>0</sub> -DB <sub>7</sub> Data bus |                      |

| 20                | V <sub>SS</sub> Ground refere             |                      |

| 21                | A <sub>0</sub>                            | Buffer address       |

| 22                | ĊS                                        | Chip select          |

| 23                | BD                                        | Blank display output |

| 24-27             | OUT A <sub>O</sub> -OUT A <sub>3</sub>    | Display A outputs    |

| 28-31             | OUT B <sub>0</sub> -OUT B <sub>3</sub>    | Display B outputs    |

| 32-35             | SL <sub>0</sub> -SL <sub>3</sub>          | Scan lines           |

| 36                | Shift                                     | Shift input          |

| 37                | CNTL/STB                                  | Control/strobe input |

| 40                | V <sub>CC</sub>                           | +5 V input           |

<sup>®</sup> Z80 is a registered trademark of Zilog, Inc.

#### Pin Functions

#### RL0-RL7 (Return Lines)

Return line inputs which are connected to the scan lines through the keys or sensor switches. They have active internal pullups to keep them high until a switch closure pulls one low. They also serve as an 8-bit input in the strobed input mode.

#### CLK (Clock)

Clock from system used to generate internal timing.

#### IRQ (Interrupt Request)

In a keyboard mode, the interrupt line is high when there is data in the FIFO/sensor RAM. The interrupt line goes low with each FIFO/sensor RAM read and returns high if there is still information in the RAM. In the sensor mode, the interrupt line goes high whenever a change in a sensor is detected.

#### **RESET (Reset)**

A high signal on this pin resets the  $\mu$ PD8279.

#### RD (Read Input)

Input read allows the data buffers to send data to the external bus.

#### WR (Write Input)

Input write allows the data buffers to receive data from the external bus.

#### DB<sub>0</sub>-DB<sub>7</sub> (Data Bus)

Bidirectional data bus. All data and commands between the processor and the  $\mu PD8279$  are transmitted on these lines.

#### OUT A<sub>0</sub>-OUT A<sub>3</sub> (Display A Outputs)

Output port for the 16 x 4 display refresh registers. The output data is synchronized to the scan lines ( $SL_0$ – $SL_3$ ) for multiplexed digit displays. Ports A and B may be blanked independently and may also be considered as one 8-bit port.

#### OUT B<sub>0</sub>-OUT B<sub>3</sub> (Display B Outputs)

Output port for the 16 x 4 display refresh registers. The output data is synchronized to the scan lines ( $SL_0$ – $SL_3$ ) for multiplexed digit displays. Ports A and B may be blanked independently and may also be considered as one 8-bit port.

#### SL<sub>0</sub>-SL<sub>3</sub> (Scan Lines)

Scan lines which are used to scan the key switch or sensor matrix and the display digits. These lines can be either encoded (1 of 16) or decoded (1 of 4).

#### A<sub>0</sub> (Buffer Address)

A high on this line indicates the signals in or out are interpreted as a command or status. A low indicates that they are data.

#### CS (Chip Select)

A low on this pin enables the interface functions to receive or transmit.

#### BD (Blank Display Output)

This output is used to blank the display during digit switching or by a display blanking command.

#### SHIFT (Shift)

The shift input status is stored along with the key position on key closure in the scanned keyboard modes. It has an active internal pullup to keep it high until a switch closure pulls it low.

#### CNTL/STB (Control/Strobe Input)

For keyboard modes this line is used as a control input and stored like status on a key closure. The line is also the strobe line that enters the data into the FIFO in strobed input mode (rising edge). It has an active internal pullup to keep it high until a switch closure pulls it low.

#### V<sub>SS</sub> (Ground Reference)

Ground.

#### V<sub>CC</sub> (Power Supply)

+5 V power supply input.

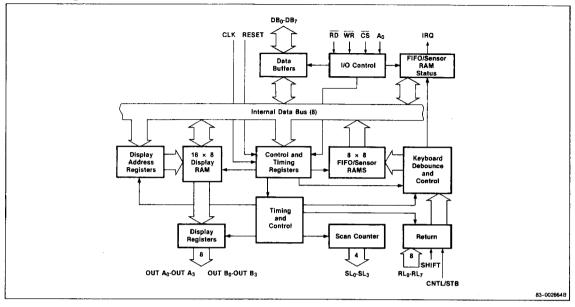

#### **Block Diagram**

#### **Functional Description**

The  $\mu$ PD8279 has two basic functions: 1) to control displays to output and 2) to control a keyboard for input. Its specific purpose is to unburden the host processor from monitoring keys and refreshing displays. The  $\mu$ PD8279 is designed to directly interface with the microprocessor bus. The microprocessor must program the operating mode to the  $\mu$ PD8279 as follows:

#### **Output Modes**

- 8 or 16 character display

- Right or left entry display formats

#### **Input Modes**

- Scanned keyboard with encoded (8 x 8 key keyboard) or decoded (4 x 8 key keyboard) scan lines.

- Scanned sensor matrix with encoded (8 x 8 matrix switches) or decoded (4 x 8 matrix switches) scan lines.

- Strobed input with data on return lines during control line strobe being transferred to FIFO.

#### **Block Diagram**

Following is a description of each section of the  $\mu PD8279$ . See the block diagram for functional reference.

#### I/O Control and Data Buffers

Communication to and from the  $\mu PD8279$  is performed by selecting  $\overline{CS}$ ,  $A_0$ ,  $\overline{RD}$  and  $\overline{WR}$ . The type of information written or read by the processor is selected by  $A_0$ . A logic 0 states that information is data while a 1 selects command or status.  $\overline{RD}$  and  $\overline{WR}$  select the direction by which the transfer occurs through the data buffers. When the chip is deselected ( $\overline{CS}=1$ ) the bidirectional data buffers are in a high impedance state. This enables the  $\mu PD8279$  to be tied directly to the processor bus.

#### **Timing Registers and Timing Control**

The timing registers store the display and keyboard modes and other conditions programmed by the processor. The timing control contains the timing counter chain. One counter is a divide-by-N scaler, which may be programmed to match the processor cycle time. The scaler is programmed with a value between 2 and 31 to divide the external clock input by N to yield the internal clock frequency. A value which scales the internal frequency to 100 kHz gives a 5.1 ms scan time and 10.3 ms switch debounce. The other counters divide down to make key, row matrix, and display scans.

#### Scan Counter

The scan counter can operate in either the encoded or decoded mode. In the encoded mode, the counter provides a count which must be decoded to provide the scan lines. In the decoded mode, the counter provides a 1 out of 4 decoded scan. In the encoded mode, the scan lines are active high, and in the decoded mode, they are active low.

#### Return Buffers, Keyboard Debounce and Control

The eight return lines are buffered and latched by the return buffers. In the keyboard mode these lines are scanned to sample for key closures in each row. If the debounce circuit senses a closure, about 10 ms are timed out and a check is performed again. If the switch is still pressed, the address of the switch matrix plus the status of shift and control are written into the FIFO. In the scanned sensor mode, the contents of return lines are sent directly to the sensor RAM (FIFO) each key scan. In the strobed mode, the transfer takes place on the rising edge of CNTL/STB.

#### FIFO/Sensor RAM and Status

This section is a dual purpose 8 x 8 RAM. In strobe or keyboard mode it is a FIFO. Each entry is pushed into the FIFO and read in order. Status keeps track of the number of entries in the FIFO. Too many reads or writes to the FIFO will be treated as an error condition. The status logic generates an IRQ whenever the FIFO has an entry. In the sensor mode the memory is a sensor RAM which detects changes in the status of a sensor. If a change occurs, the IRQ is generated until the change is acknowledged.

#### **Display Address Registers and Display RAM**

The display address register contains the address of the word being read or written by the processor, as well as the word being displayed. This address may be programmed to autoincrement after each read or write. The display RAM may be read by the processor any time after the mode and address is set. Data entry to the display RAM may be set to either right or left entry.

#### **Command Operation**

The commands programmable to the  $\mu$ PD8279 via the data bus with  $\overline{\text{CS}}$  active (0) and  $A_0$  high are as follows:

#### Keyboard/Display Mode Set

| 0 | 0 | 0 | D | D | К | K | ĸ |

|---|---|---|---|---|---|---|---|

#### **Display Mode:**

| Đ | D     |                                             |

|---|-------|---------------------------------------------|

| 0 | 0     | Eight 8-bit character display—left entry    |

| 0 | 1 (1) | Sixteen 8-bit character display—left entry  |

| 1 | 0     | Eight 8-bit character display-right entry   |

| 1 | 1     | Sixteen 8-bit character display—right entry |

#### Note:

(1) Power on default condition.

#### **Keyboard Mode:**

| K | K | K |                                     |

|---|---|---|-------------------------------------|

| 0 | 0 | 0 | Encoded scan-2 key lockout          |

| 0 | 0 | 0 | Decoded scan-2 key lockout          |

| 0 | 1 | 0 | Encoded scan-N key rollover         |

| 0 | 1 | 1 | Decoded scan-N key rollover         |

| 1 | 0 | 0 | Encoded scan—sensor matrix          |

| 1 | 0 | 1 | Decoded scan—sensor matrix          |

| 1 | 1 | 0 | Strobed input, encoded display scan |

| 1 | 1 | 1 | Strobed input, decoded display scan |

#### **Program Clock**

| 0 | 0 | 1 | P | р | Р | Р | Р |

|---|---|---|---|---|---|---|---|

Where PPPPP is the prescaler value between 2 and 31. This prescaler divides the external clock by PPPPP to develop its internal frequency. After reset, a default value of 31 is generated.

#### Read FIFO/Sensor RAM

| l | 0 | 1 | 0 | <b>A</b> <sub>1</sub> | Х | Α | A | Α | $A_0 = 0$ |

|---|---|---|---|-----------------------|---|---|---|---|-----------|

$A_1$  is the autoincrement flag. AAA is the row to be read by the processor. The read command is accomplished with  $(\overline{CS} \bullet RD \bullet \overline{A0})$  by the processor. If  $A_1$  is 1, the row select counter will be incremented after each read. Note that autoincrementing has no effect on the display.

#### Read Display RAM

| 0 | 1 | 1 | A <sub>1</sub> | Х | Α | Α | Α | $A_0 = 0$ |

|---|---|---|----------------|---|---|---|---|-----------|

|   |   |   |                |   |   |   |   |           |

Where  $A_1$  is the autoincrement flagg and AAAA is the character which the processor is about to read.

#### Write Display RAM

|   |   | - |                |   |   |   |   |

|---|---|---|----------------|---|---|---|---|

| 1 | 0 | 0 | A <sub>1</sub> | Α | Α | Α | Α |

Where AAAA is the character the processor is about to write.

#### Display Write Inhibit Blanking

|   | 1 | 0 | 1 | Х | IW | IW | BL | BL. |

|---|---|---|---|---|----|----|----|-----|

| 1 |   |   |   |   | Α  | В  | Α  | В   |

Where IWA and IWB are inhibit writing nibble A and B respectively, while BLA and BLB are used for blanking. When using the display as a dual 4-bit, it is necessary to mask one of the 4-bit halves to eliminate interaction between the two halves. This in accomplished with the IW flags. The BL flags allow the programmer to blank either half of the display independently. To blank a display formatted as a single 8-bit, it is necessary to set both BLA and BLB. Default after a reset is all zeros. All signals are active high (logic 1).

#### Clear

| 1  | 1  | 0   | CD         | CD                    | CD | C <sub>F</sub> | CA |  |  |

|----|----|-----|------------|-----------------------|----|----------------|----|--|--|

| 1  |    |     |            |                       |    |                |    |  |  |

| CD | CD | C   | <b>;</b> 0 |                       |    |                |    |  |  |

| 1  | 0  |     | X          | All zeros             |    |                |    |  |  |

| 1  | 1  |     | 0          | AB = 20H              |    |                |    |  |  |

| 1  | 1  |     | 1          | All ones              |    |                |    |  |  |

| 0  | X  | - : | X          | Disable clear display |    |                |    |  |  |

This command is used to clear the display RAM, the FIFO, or both. The  $C_D$  options allow the user the ability to clear the display RAM to either all zeros or all ones. Clearing the display takes one complete display scan. During this time the processor can't write to the display RAM.

If the  $C_F$  bit is set to logic 1, the FIFO status is cleared, the FIFO empty flag is set, and IRQ is cleared. The sensor matrix mode RAM pointer will then be set to row 0.

$C_A$ , the clear all bit, has the combined effect of  $C_F$  and  $C_D$ ; it uses the  $C_D$  clearing code on the display RAM and also clears FIFO status. It also resynchronizes the internal timing chain.

#### End Interrupt/Error Mode Set

|   |   | P |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | E | X | Х | Х | Х |

In the sensor matrix mode, this instruction clears IRQ and allows writing into RAM. In N key rollover, setting the E bit to 1 allow for operating in the special error mode. See description of FIFO status.

#### **FIFO Status**

|    |     |   |   | , |   |   |   |

|----|-----|---|---|---|---|---|---|

| DU | S/E | 0 | Ü | F | N | N | N |

|    |     |   |   |   |   |   |   |

#### Where:

- DU = Display unavailable because a clear display or clear all command is in progress.

- S/E = Sense error flag due to multiple closure of switch matrix.

- O = FIFO overrun since an attempt was made to push too many characters into the FIFO.

- U = FIFO underrun. An indication that the processor tried to read an empty FIFO.

- F = FIFO full flag.

- NNN = The number of characters presently in FIFO.

The FIFO status is read with  $A_0$  high and  $\overline{CS}$ ,  $\overline{RD}$  active low.

If the  $C_D$  or  $C_A$  command has not completed its clearing, the display is not available. The S/E flags are used to show an error in multiple closures has occurred. The O or U, overrun or underrun, flags occur when too many characters are written into the FIFO or the processor tries to read an empty FIFO. F is an indication that the FIFO is full and NNN is the number of characters in the FIFO.

#### **Data Read**

Data can be read during  $A_0=0$  and when  $\overline{CS}$ ,  $\overline{RD}$  are active low. The source of data is determined by the read display or read FIFO commands.

#### **Data Write**

Data is written to the chip when  $A_0$ ,  $\overline{CS}$ , and  $\overline{WR}$  are active low. Data will be written into the display RAM with its address selected by the latest read or write display command.

#### **Data Format**

| - 1 |      |    |      |     |

|-----|------|----|------|-----|

|     | CNTL | SH | SCAN | RET |

In the scanned key mode, the characters in the FIFO correspond to the above format where CNTL and SH are the most significant bits and the SCAN and return lines are the scan and column counters.

| I   |     | ·   | <b>.</b> | <b>.</b> |                 |                 |                 |

|-----|-----|-----|----------|----------|-----------------|-----------------|-----------------|

| KL7 | HL6 | HL5 | RL4      | HL3      | RL <sub>2</sub> | RL <sub>1</sub> | RL <sub>0</sub> |

|     |     |     |          |          |                 |                 |                 |

In the sensor matrix mode, the data corresponds directly to the row of the sensor RAM being scanned. Shift and control (SH, CNTL) are not used in this mode.

#### **Command Word Summary**

| 0  | 0   | 0 | D              | D  | K  | K  | К  | Keyboard display mode set      |

|----|-----|---|----------------|----|----|----|----|--------------------------------|

| 0  | 0   | 1 | Р              | Р  | Р  | Р  | Р  | Load program clock             |

| 0  | 1   | 0 | A <sub>1</sub> | Х  | Α  | Α  | Α  | Read FIFO/sensor RAM           |

| 0  | 1   | 1 | A <sub>1</sub> | Α  | Α  | Α  | Α  | Read display RAM               |

| 1  | 0   | 0 | A <sub>1</sub> | Α  | Α  | Α  | Α  | Write display RAM              |

| 1  | 0   | 1 | Χ              | IW | IW | BL | BL | Display write inhibit/blanking |

|    |     |   |                | Α  | В  | Α  | В  |                                |

| 1  | 1   | 0 | CD             | CD | CD | CF | CA | Clear                          |

| 1  | 1   | 1 | E              | Χ  | Χ  | χ  | X  | End interrupt/error mode set   |

| DU | S/E | 0 | U              | F  | N  | N  | N  | FIFO status                    |

## Absolute Maximum Ratings

| -0.5 V to +7.0 V(1) |

|---------------------|

| 1.0 W               |

| 0°C to +70°C        |

| -65°C to +150°C     |

|                     |

#### Note:

(1) With respect to V<sub>SS</sub>.

Comment: Exposing the device to stresses above those listed in the absolute maximum ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### Capacitance

|                    |        | ı   | Limits |     | Test |                  |

|--------------------|--------|-----|--------|-----|------|------------------|

| Parameter          | Symbol | Min | Typ    | Max | Unit | Conditions       |

| Input capacitance  | CI     | 5   |        | 10  | рF   | $V_{l} = V_{CC}$ |

| Output capacitance | CO     | 10  |        | 20  | рF   | $V_0 = V_{CC}$   |

#### **DC Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = 5 \text{ V } \pm 10\%$ ;  $V_{SS} = 0 \text{ V}$

|                                       |                  | Lin  | nits |      | Test                       |

|---------------------------------------|------------------|------|------|------|----------------------------|

| Parameter                             | Symbol           | Min  | Max  | Unit | Conditions                 |

| Input high voltage for return lines   | V <sub>IH1</sub> | 2.2  |      | ٧    |                            |

| Input high voltage for other lines    | V <sub>IH2</sub> | 2.0  |      | ٧    |                            |

| Input low voltage for return lines    | V <sub>IL1</sub> | -0.5 | 1.4  | ٧    |                            |

| Input low voltage for other lines     | V <sub>IL2</sub> | -0.5 | 0.8  | ٧    |                            |

| Output high voltage on interrupt line | IRQ<br>pin       | +3.5 |      | ٧    | $I_{OH} = -50 \mu\text{A}$ |

|                                       | others           | +2.4 |      | ٧    | $i_{OH} = -400 \mu A$      |

| Output low voltage                    | V <sub>OL</sub>  |      | 0.45 | ٧    | $I_{OL} = 2.2 \text{ mA}$  |

| Input current on shift,               | l <sub>IL1</sub> |      | +10  | μΑ   | $V_1 = V_{CC}$             |

| control and return lines              |                  |      | -100 | μΑ   | $V_1 = 0 V$                |

| Input leakage current for other lines | I <sub>IL2</sub> |      | ±10  | μΑ   | $V_I = V_{CC}$ to 0 V      |

| Output float leakage                  | OFL              |      | ±10  | μΑ   | $V_0 = V_{CC}$ to 0 V      |

| Power supply current                  | lcc              |      | 120  | mA   |                            |

AC Characteristics  $T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5 \text{ V } \pm 10\%; V_{SS} = 0 \text{ V}$

|                             |                  | μ <b>PD8279-5</b><br>Limits |     | μ <b>PD8279-2</b><br><b>Limits</b> |     |      | Test                    |

|-----------------------------|------------------|-----------------------------|-----|------------------------------------|-----|------|-------------------------|

| Parameter                   | Symbol           | Min                         | Max | Min                                | Max | Unit | Conditions              |

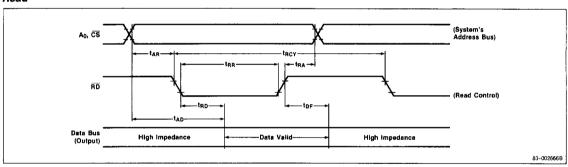

| Read                        |                  |                             |     |                                    |     |      |                         |

| Address stable before read  | t <sub>AR</sub>  | 0                           |     | 0                                  |     | ns   |                         |

| Address hold time for read  | t <sub>RA</sub>  | 0                           |     | 0                                  |     | ns   |                         |

| Read pulse width            | t <sub>RR</sub>  | 250                         |     | 200                                |     | ns   | -                       |

| Data delay from read        | t <sub>RD</sub>  |                             | 150 | -                                  | 140 | ns   | C <sub>L</sub> = 150 pF |

| Address to data valid       | t <sub>AD</sub>  |                             | 250 |                                    | 250 | ns   | C <sub>L</sub> = 150 pF |

| Read to data floating       | t <sub>DF</sub>  | 10                          | 100 | 10                                 | 100 | ns   |                         |

| Read cycle time             | t <sub>RCY</sub> | 1000                        |     | 200                                |     | ns   |                         |

| Write                       |                  |                             |     |                                    |     |      |                         |

| Address stable before write | t <sub>AW</sub>  | 0                           |     | 0                                  |     | ns   |                         |

| Address hold time for write | t <sub>WA</sub>  | 0                           |     | 0                                  |     | ns   |                         |

| Write pulse width           | tww              | 250                         |     | 200                                |     | ns   |                         |

| Data set up time for write  | t <sub>DW</sub>  | 150                         |     | 150                                |     | ns   |                         |

| Data hold time for write    | t <sub>WD</sub>  | 0                           |     | 0                                  |     | ns   |                         |

| Write cycle time            | twcy             | 1000                        |     | 200                                |     | ns   |                         |

| Other                       |                  |                             |     |                                    |     |      |                         |

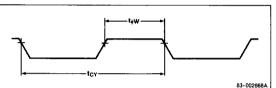

| Clock pulse width           | t <sub>eW</sub>  | 120                         | -   | 70                                 |     | ns   |                         |

| Clock period                | t <sub>CY</sub>  | 320                         |     | 200                                |     | ns   |                         |

### **General Timing**

| Keyboard scan time     | 5.1 ms  |

|------------------------|---------|

| Keyboard debounce time | 10.3 ms |

| Key scan time          | 80 µs   |

| Display scan time      | 10.3 ms |

| Digit-on time          | 480 µs  |

| Blanking time          | 160 µs  |

| Internal clock cycle   | 10 µs   |

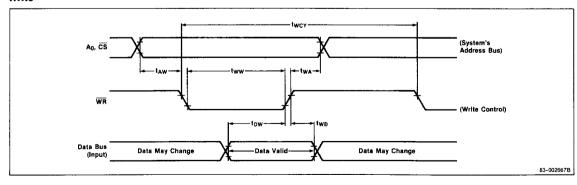

#### **Timing Waveforms**

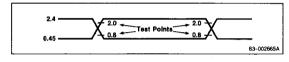

#### AC Test Input

#### Clock Input

#### Read

#### Write