04E 01827

D

T-75-33-09

# GD4702B/GD4702BX PROGRAMMABLE BIT-RATE GENERATOR

DESCRIPTION — The 4702B/4702BX Bit-Rate Generator provides the necessary clock signals for digital data transmission systems, such as Universal Asynchronous Receiver and Transmitter circuits (UARTs). It generates any of the 14 commonly used bit rates using an on-chip crystal oscillator, but its design also provides for easy and economical multi-channel operation, where any of the possible frequencies must be made available on any output channel.

One 4702B/4702BX can control up to eight output channels. When more than one bit-rate generator is required, they can still be operated from one crystal. The 4702B is specified to operate over a power supply voltage range of 5 V  $\pm$  10%. The 4702BX is a specially selected device specified to operate over a power supply voltage range of 4.5 V to 12.5 V,

- PROVIDES 14 COMMONLY USED BIT-RATES

- ONE 4702B/4702BX CONTROLS UP TO EIGHT TRANSMISSION CHANNELS

- USES 2.4576 MHz INPUT FOR STANDARD FREQUENCY OUTPUTS (16 TIMES BIT RATE)

- CONFORMS TO EIA RS-404

- ON-CHIP INPUT PULL UP CIRCUITS

- TTL COMPATIBLE-OUTPUTS WILL SINK 1.6 mA

- INITIALIZATION CIRCUIT FACILITIES DIAGNOSTIC FAULT ISOLATION

- LOW POWER DISSIPATION 1.35 mA POWER DISSIPATION AT 5 V AND 2.4576 MHz

- 16-PIN DUAL IN-LINE PACKAGE

TABLE 1

CLOCK MODES AND INITIALIZATION

| ١x | Ē <sub>CP</sub> | СР  | OPERATION                         |

|----|-----------------|-----|-----------------------------------|

| ww | Н               | L   | Clocked from IX                   |

| χ. | L               | ~~~ | Clocked from CP                   |

| х  | н               | н   | Continuous Reset                  |

| ×  | L               |     | Reset During First CP ≈ HIGH Time |

H = HIGH Level

L = LOW Level

X = Don't Care

I = 1st HIGH Level

Clock Pulse

After E<sub>CP</sub> Goes

LOW-

Note 1: Actual output frequency is 16 times the indicated output rate, assuming a clock frequency of 2.4576 MHz.

TABLE 2

TRUTH TABLE FOR RATE SELECT INPUTS

| s <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | s <sub>0</sub> | Output Rate (Z)<br>Note 1 |

|----------------|----------------|----------------|----------------|---------------------------|

| Ľ              | L              | L.             | L              | Multiplexed Input (IM)    |

| Ĺ              | L              | L,             | н              | Multiplexed Input (IM)    |

| L              | L              | Н              | L              | 50 Baud                   |

| L              | L              | н              | н              | · 75 Baud                 |

| L              | Н              | L              | L              | 134.5 Baud                |

| L,             | н              | L              | н              | 200 Baud                  |

| L              | н              | H              | L              | 600 Baud                  |

| L              | н              | Н              | Н              | 2400 Baud                 |

| н              | L              | L              | L.             | 9600 Baud                 |

| н              | L              | L              | н              | 4800 Baud                 |

| H              | L              | Н              | L              | 1800 Baud                 |

| H              | L              | Н              | н              | 1200 Baud                 |

| н              | н              | L              | L              | 2400 Baud                 |

| н              | н              | L              | н              | 300 Baud                  |

| н              | н              | н              | L              | 150 Baud                  |

| н              | н              | н              | н              | 110 Baud                  |

L = LOW Level H = HIGH Level

| 5 —<br>4 —<br>7 —<br>6 —                                                                                                            | 15 14 13 12 11                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                     | V <sub>DD</sub> = Pin 16<br>V <sub>SS</sub> = Pin 8                                                                                                                     |

|                                                                                                                                     |                                                                                                                                                                         |

| CON                                                                                                                                 | INECTION DIAGRAM<br>DIP (TOP VIEW)                                                                                                                                      |

| 1 [<br>2 [<br>3 [<br>4 [<br>5 [<br>6 [<br>7 [<br>8 [                                                                                |                                                                                                                                                                         |

| NOTE:<br>The SOP<br>outs (Cond<br>Dual In-line                                                                                      | nection Diagram) as the                                                                                                                                                 |

|                                                                                                                                     | PIN NAMES                                                                                                                                                               |

| CP<br>E <sub>CP</sub><br>I <sub>M</sub><br>S <sub>0</sub> -S <sub>3</sub><br>CO<br>O <sub>X</sub><br>Q <sub>0</sub> -Q <sub>2</sub> | External Clock Input External Clock Enable Input (Active LOW) Crystal Input Multiplexed Input Rate Select Inputs Clock Output Crystal Drive Output Scan Counter Outputs |

Bit Rate Output

· 74

4028757 GOLDSTAR TECHNOLOGY INC.

DT-75-33-09 04E 01828

# GS CMOS · GD4702B/GD4702BX

04E 01829 DT- 75-33-09

# GS CMOS · GD4702B/GD4702BX

FUNCTIONAL DESCRIPTION — Digital data transmission systems employ a wide range of standardized bit rates, ranging from 50 baud interfacing with electromechanical devices, to 9600 baud for high speed modems. Modern electronic systems commonly use Universal Asynchronous Receiver and Transmitter circuits (UARTs) to convert parallel data inputs into a serial bit stream (transmitter) and to reconvert the serial bit stream into parallel outputs (receiver). In order to resynchronize the incoming serial data, the receiver requires a clock rate that is a multiple of the incoming bit rate. Popular MOS-LSI UART circuits use a clock that is 16 times the transmitted bit rate. The 4702B/4702BX can generate 14 standardized clock rates from one commonly high frequency input.

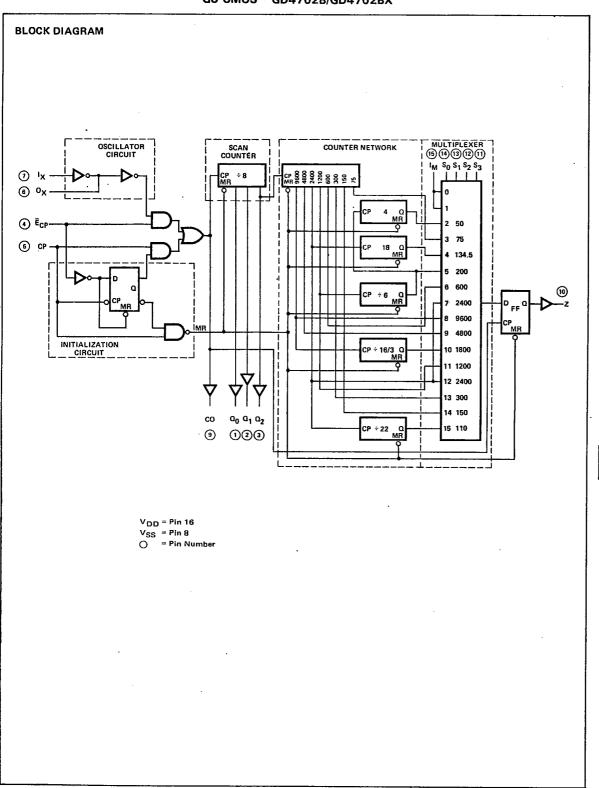

The 4702B/4702BX contains the following five functional subsystems which are discussed in detail below:

- 1. An Oscillator Circuit with associated gating.

- 2. A prescaler used as Scan Counter for multichannel operation (described in the applications section).

- 3. A Counter Network to generate the required standardized frequencies.

- 4. An output Multiplexer (frequency selector) with resynchronizing output flip-flop.

- 5. An Initialization (reset) Circuit.

Oscillator — For conventional operation generating 16 output clock pulses per bit period, the input clock frequency must be 2.4576 MHz (i.e. 9600 baud x 16 x 16, since the scan counter and the first flip-flop of the counter chain act as an internal ÷ 16 prescaler). A lower input frequency will obviously result in a proportionally lower output frequency.

The 4702B/4702BX can be driven from two alternate clock sources: (1) When the ECP (active LOW External Clock Enable) input is LOW, the CP input is the clock source. (2) When the ECP input is HIGH, a crystal connected between I<sub>X</sub> and O<sub>X</sub>, or a signal applied to the I<sub>X</sub> input, is the clock source.

Prescaler (Scan Counter) — The clock frequency is made available on the CO (Clock Output) pin and is applied to the  $\div$  8 prescaler with buffered outputs  $Q_0$ ,  $Q_1$ , and  $Q_2$ . This prescaler is of no particular advantage in single frequency applications, but it is essential for the simple economical multichannel scheme described in the Applications section of this data book.

Counter Network — The prescaler output  $Q_2$  is a square wave of 1/8 the input frequency and is used to drive the frequency counter network generating 13 standardized frequencies. Note that the frequencies are labeled in the block diagram and described in terms of the transmission bit rate. In a conventional system using a 2.4576 MHz clock input, the actual output frequencies are 16 times higher.

The output from the first frequency divider flip-flop is thus labeled 9600, since it is used to transmit or receive 9600 baud (bits per second). The actual frequency at this node is  $16 \times 9.6 \text{ kHz} = 153.6 \text{ kHz}$ . Seven more cascaded binaries generate the appropriate frequencies for bit rates 4800, 2400, 1200, 600, 300, 150, and 75.

The other five bit rates are generated by individual counters:

bit rate 1200 is divided by 6 to generate bit rate 200,

bit rate 200 is divided by 4 to generate bit rate 50,

bit rate 2400 is divided by 18 to generate bit rate 134.5 with a frequency error of -0.87%,

bit rate 2400 is also divided by 22 to generate bit rate 110 with a frequency error of -0.83%, and

bit rate 9600 is divided by 16/3 to generate bit rate 1800.

The 16/3 division is accomplished by alternating the divide ratio between 5 (twice) and 6 (once). The result is an exact average output frequency with some frequency modulation. Taking advantage of the  $\div$  16 feature of the UART, the resulting distortion is less than 0.78%, irrespective of the number of elements in a character, and therefore well within the timing accuracy specified for high speed communications equipment. All signals except 1800, have a 50% duty cycle.

Output Multiplexer — The outputs of the counter network are fed to a 16-input multiplexer, which is controlled by the Rate Select inputs ( $S_0$ - $S_3$ ). The multiplexer output is then resynchronized with the incoming clock in order to cancel all cumulative delays and to present an output signal at the buffered output (Z) that is synchronous with the prescaler outputs ( $Q_0$ - $Q_2$ ). Table 2 lists the correspondence between select code and output bit rate. Two of the 16 codes do not select an internally generated frequency, but select an input into which the user can feed either a different, nonstandardized frequency, or a static level (HIGH or LOW) to generate "zero baud".

The bit rates most commonly used in modern data terminals (110, 150, 300, 1200, 2400 baud) require that no more than one input be grounded, easily achieved with a single pole, 5-position switch. 2400 baud is selected by two different codes, so that the whole spectrum of modern digital communication rates has a common HIGH on the S<sub>3</sub> input.

Initialization (Reset) — The initialization circuit generates a common master reset signal for all flip-flops in the 4702B/4702BX. This signal is derived from a digital differentiator that senses the first HIGH level on the CP input after the Ecp input goes LOW. When Ecp is HIGH, selecting the Crystal input, CP must be LOW. A HIGH level on CP would apply a continuous reset.

All inputs to the 4702B/4702BX, except  $I_X$  have on-chip pull-up circuits which improve TTL compatibility and eliminate the need to tie a permanently HIGH input to  $V_{DD}$ .

04E 01830 DT-75-33-09

# GS CMOS · GD4702B/GD4702BX

| SYMBOL                                                 | PARAMETER                         |          | LIMITS       |              |          | UNITS        | TEMP          | T-07 00                                                                                                 |                                 |  |

|--------------------------------------------------------|-----------------------------------|----------|--------------|--------------|----------|--------------|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------|--|

|                                                        |                                   |          |              | TYP          | MAX      | 7 0,411.3    | I SIVIP       | TEST CONDITIONS                                                                                         |                                 |  |

| VIH                                                    | Input HIGH Voltage                |          | 3.5          |              |          | V            | All           | Guaranteed Inc                                                                                          | out High Voltage                |  |

| VIL                                                    | Input LOW Voltage                 |          |              |              | 1.5      | V            | All           |                                                                                                         | out LOW Voltage                 |  |

| VOH Output HIGH Voltage                                |                                   | 4.95     |              |              | <u> </u> |              |               | puts at 0 or 5 V p                                                                                      |                                 |  |

|                                                        |                                   | 4.95     | ļ            |              | V        | MAX          |               | tion or Truth Table                                                                                     |                                 |  |

|                                                        |                                   |          | 4.5          | ļ            | ļ        | V            | All           |                                                                                                         | nputs at 1.5 or 3.5             |  |

| VOL Output LOW Voltage                                 |                                   | <u></u>  | ļ.,          | 0.05         | ↓ v      | MIN, 25°C    | IOL < 1 μΑ, I | puts at 0 or 5 V p                                                                                      |                                 |  |

| *OL                                                    | Output LOW Voltage                |          | <del> </del> | <b> </b>     | 0.05     | <u> </u>     | MAX           |                                                                                                         | tion or Truth Table             |  |

|                                                        | Innua I OW O                      | 1        | <u> </u>     | <u> </u>     | 0.5      | V            | All           | IOL < 1 µA, Inputs at 1.5 or 3.                                                                         |                                 |  |

| tL                                                     | Input LOW Current<br>for Input Ix | xc       |              | <del> </del> | 0.3      | μА           | MIN, 25°C     | Pin under Test at 0 V<br>All other Inputs Simultaneously                                                |                                 |  |

| (See                                                   | Tor Input IX                      | XM       |              |              | 1 0.4    | <u> </u>     | MAX           |                                                                                                         |                                 |  |

| Note 1)                                                |                                   | ^\"      | <del> </del> | -            | 0.1      | μА           | MIN, 25°C     |                                                                                                         |                                 |  |

|                                                        | Input LOW Current                 | хc       | -15          | -30          | -100     | <del> </del> | MAX           | at 5 V                                                                                                  |                                 |  |

|                                                        | for all Other Inputs              | XM       | -15          | -30          | -100     | μΑ           | 25°C          |                                                                                                         |                                 |  |

|                                                        |                                   | xc       |              |              | 0.3      | <del> </del> | MIN, 25°C     |                                                                                                         | <del></del>                     |  |

| _                                                      | Input HIGH Current                | <u></u>  |              |              | 1        | μΑ           | MAX           | Pin Under Test at 5 V                                                                                   |                                 |  |

| lН                                                     | for all inputs                    | XM       |              |              | 0.1      | μΑ           | MIN, 25°C     |                                                                                                         | All other Inputs Simultaneously |  |

|                                                        | 0                                 | <u> </u> |              |              | 1        | μΑ.          | MAX           | at 0 V                                                                                                  |                                 |  |

| i i                                                    | Output HIGH Current               |          | -0.3         |              |          | mA           | MIN, 25°C     |                                                                                                         |                                 |  |

| for Output OX                                          |                                   |          | -0.1         |              |          |              | MAX           | V <sub>OUT</sub> = 4.5 V                                                                                |                                 |  |

|                                                        | Output HIGH Current               |          | 1.5          |              |          | mA           | MIN, 25°C     | V <sub>OUT</sub> = 2.5 V                                                                                |                                 |  |

|                                                        | for all other Outputs             |          | -1<br>-0.5   |              |          |              | MAX           |                                                                                                         |                                 |  |

|                                                        |                                   |          |              |              |          | mA           | MIN, 25°C     | V                                                                                                       | Inputs at 0 or 5                |  |

|                                                        |                                   |          | 0.3<br>0.2   |              |          |              | MAX           | VOUT = 4.5 V                                                                                            | per Logic                       |  |

|                                                        | Output LOW Current                |          |              |              |          | mA           | MIN, 25°C     |                                                                                                         | Function or<br>Truth Table      |  |

| for Output OX Output LOW Current for all Other Outputs |                                   |          | 0.1          |              |          |              | MAX           |                                                                                                         |                                 |  |

|                                                        |                                   |          | 3,2          |              |          | 4            | MIN, 25°C     |                                                                                                         |                                 |  |

|                                                        | tor an Other Outputs              | - Va     | 1.6          |              |          | mA MAX       |               |                                                                                                         |                                 |  |

|                                                        | Quiescent Power                   | xc       |              |              | 100      | μΑ           | MIN, 25°C     | E <sub>CP</sub> = V <sub>DD</sub> , CP = 0 V,<br>All other Inputs at 0 V<br>or V <sub>DD</sub> (Note 6) |                                 |  |

| DD                                                     | Supply Current                    | XM       |              | +            | 1000     |              | MAX           |                                                                                                         |                                 |  |

|                                                        |                                   |          |              |              | 150      |              | MIN, 25°C     |                                                                                                         |                                 |  |

04E 01831

DT-75-33-09

#### GS CMOS · GD4702B/GD4702BX

| SYMBOL               | PARAMETER                         | LIMITS |      |      |       | TEST CONDITIONS                                        |

|----------------------|-----------------------------------|--------|------|------|-------|--------------------------------------------------------|

|                      |                                   | MIN    | TYP  | MAX  | UNITS |                                                        |

| t <sub>PLH</sub>     | Propagation Delay                 |        | 175  | 350  |       |                                                        |

| <sup>t</sup> PHL     | IX to CO                          |        | 135  | 275  | ns    |                                                        |

| tPLH                 | Propagation Delay                 | ·      | 130  | 260  |       |                                                        |

| tPHL,                | CP to CO                          |        | 110  | 220  | ns    |                                                        |

| t <sub>PLH</sub>     | Propagation Delay ·               |        | 53   | Note |       | 1                                                      |

| tPHL.                | CO to Q <sub>n</sub>              |        | 45   | 5    | ns    | CL = 50 pF, RL = 200 kΩ Input Transition Times < 20 ns |

| t <sub>PLH</sub>     | Propagation Delay                 |        | 37   | 85   |       |                                                        |

| <sup>t</sup> PHL     | CO to Z                           |        | 32   | 75   | ns    |                                                        |

| tTLH                 | Output Transition                 |        | 80   | 160  |       |                                                        |

| †THL                 | Time (Except O <sub>X</sub> )     | 1      | 35   | 75   | ns    |                                                        |

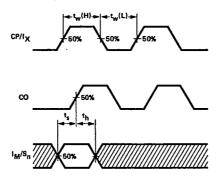

| t <sub>s</sub>       | Set-Up Time, Select to CO         | 350    | 185  |      |       | C <sub>L</sub> < 7 pF on O <sub>X</sub>                |

| th                   | Hold Time, Select to CO           | ŀ      | -182 |      | ns    |                                                        |

| ts                   | Set-Up Time, I <sub>M</sub> to CO | 350    | 190  | 1    |       | 1                                                      |

| th                   | Hold Time, I <sub>M</sub> to CO   | 0      | -182 |      | ns    |                                                        |

| twCP(L)              | Minimum Clock Pulse Width         | 120    | 60   |      |       | 1                                                      |

| twCP(H)              | LOW and HIGH                      | 120    | 60   |      | ns    |                                                        |

| twlX(L)              | Minimum IX Pulse Width            | 160    | 75   |      |       |                                                        |

| t <sub>W</sub> IX(H) | LOW and HIGH                      | 160    | 75   | 1    | ns    |                                                        |

#### NOTES:

- Propegation Delays and Output Transition Times are graphically described under 4000B Series CMOS Family Characteristics.

The first HIGH level Clock Pulse after E<sub>CP</sub> goes LOW must be at least 350 ns long to guarantee reset of all Counters.

It is recommended that input rise and fall times to the Clock Inputs (CP, IX) be less than 15 µs at V<sub>DD</sub> = 5 V, 4 µs at V<sub>DD</sub> = 10 V, and 3 µs

- at V<sub>DD</sub> = 15 V, and the V<sub>DD</sub> pin should be decoupled.

4. Input current and quiescent power supply current are relatively higher for this device because of active pull-up circuits on all inputs except I<sub>X</sub>. This is done for TTL compatibility.

5. For multichannel operation, propagation delay, CO to Q<sub>n</sub>, plus set-up time, select to CO, is guaranteed to < 367 ns.

- 6. IDD is measured on Pin 8 and does not include Input Leakage Currents.

#### **SWITCHING WAVEFORMS**

MINIMUM CP AND  $\rm I_X$  PULSE WIDTHS AND SET-UP AND HOLD TIMES, SELECT INPUT (S\_n) TO CLOCK OUTPUT (CO) AND  $\rm I_M$  INPUT TO CLOCK OUTPUT (CO)

NOTE: Set-up and Hold Times are shown as positive values but may be specified as negative values.

04E 01832

Q3:

Q7:

1800 Baud,

150 Baud.

DT-75-33-09

#### GS CMOS · GD4702B/GD4702BX

#### **APPLICATIONS**

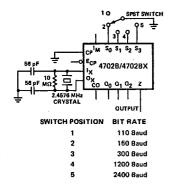

Single Channel Bit Rate Generator — Figure 1 shows the simplest application of the 4702B/4702BX. This circuit generates one of five possible bit rates as determined by the setting of a single pole, 5-position switch. The bit rate output (Z) drives one standard TTL load or four low power Schottky loads over the full temperature range. The possible output frequencies correspond to 110, 150, 300, 1200, and 2400 Baud. For many low cost terminals these five bit rates are adequate.

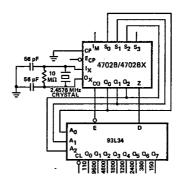

#### Simultaneous Generation of Several Bit Rates:

Fixed Programmed Multichannel Operation — Figure 2 shows a simple scheme that generates eight bit rates on eight output lines, using one 4702B/4702BX and one 93L34 8-Bit Addressable Latch. This and the following applications take advantage of the built-in scan counter (prescaler) outputs. As shown in the block diagram, these outputs (O<sub>0</sub> to O<sub>2</sub>) go through a complete sequence of eight states for every half-period of the highest output frequency (9600 Baud). Feeding these Scan Counter outputs back to the Select inputs of the multiplexer causes the 4702B/4702BX to interrogate sequentially the state of eight different frequency signals. The 93L34 8-Bit Addressable Latch, addressed by the same Scan Counter outputs, reconverts the multiplexed single output (Z) of the 4702B/4702BX into eight parallel output frequency signals. In the simple scheme of Figure 2, input S<sub>3</sub> is left open (HIGH) and the following bit rates are generated:

Q<sub>0</sub>: 110 Baud, Q<sub>1</sub>: 9600 Baud, Q<sub>2</sub>: 4800 Baud, Q<sub>4</sub>: 1200 Baud, Q<sub>5</sub>: 2400 Baud, Q<sub>6</sub>: 300 Baud,

Other bit rate combinations can be generated by changing the Scan Counter to selector interconnection or by inserting logic gates into this path.

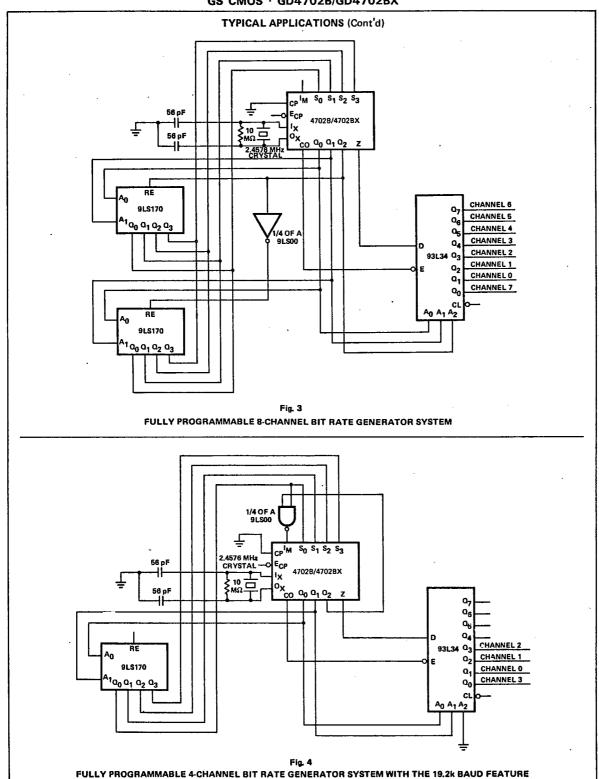

Fully Programmable Multichannel Operation — Figure 3 shows a fully programmable 8-channel bit rate generator system that, under computer control, generates arbitrarily assigned bit rates on all eight outputs simultaneously. The basic operation is similar to the previously described fixed programmed system, but two 9LS170 4 x 4 Register File MSI packages are connected as programmable look-up tables between the Scan Counter outputs (Q<sub>0</sub> to Q<sub>2</sub>) and the multiplexer Select inputs (S<sub>0</sub> to S<sub>3</sub>). The content of this 8-word by 4-bit memory determines which frequency appears at what output.

19200 Baud Operation — Though a 19200 Baud signal is not internally routed to the multiplexer, the 4702B/4702BX can be used to generate this bit rate by connecting the Q<sub>2</sub> output to the I<sub>M</sub> input and applying select code 0 or 1. An additional 2-input NAND gate can be used to retain the "Zero Baud" feature on select code 0. Any multichannel operation that involves 19200 Baud must be limited to four outputs as shown in *Figure 4*. Only the two least significant Scan Counter outputs are used, so that the scan is completed within one half period of the 19200 output frequency.

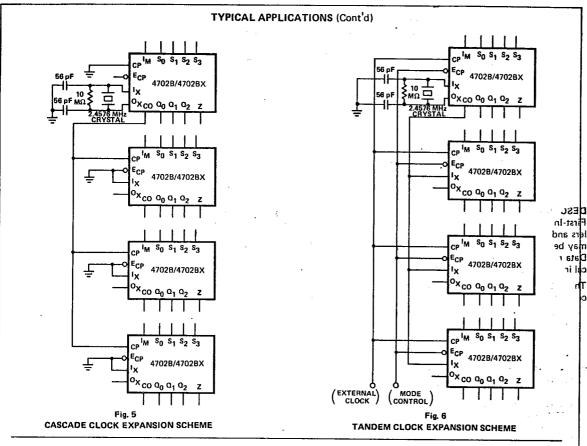

Clock Expansion — One 4702B/4702BX can control up to eight output channels. For more than eight channels, additional bit rate generators are required. These bit rate generators can all be run from the same crystal or clock input. Figure 5 shows one possible expansion scheme. One 4702B/4702BX is provided with a crystal. All other devices derive their clock from this master. Figure 6 shows a different scheme where the master clock output feeds into the Ix input of all slaves and all Ecp inputs are normally held HIGH. This scheme retains the reset feature and the selection between two different clock sources of the basic 4702B/4702BX circuit.

During normal operation, the common E<sub>CP</sub> line is HIGH and the common clock line (CP) is LOW. For diagnostic purposes the common E<sub>CP</sub> is forced LOW. This deselects the crystal frequency and initiates the diagnostic mode. When CP goes HIGH for the first time, all 4702B/4702BXs are reset through their individual on-chip initialization circuitry. Subsequent LOW-to-HIGH clock transitions on the common CP line advance the scan counter, causing all 4702B/4702BXs to operate synchronously.

#### TYPICAL APPLICATIONS

Fig. 1 SWITCH SELECTABLE BIT RATE GENERATOR CONFIGURATION PROVIDING FIVE BIT RATES

Fig. 2

BIT RATE GENERATOR CONFIGURATION

WITH EIGHT SIMULTANEOUS FREQUENCIES

4028757 GOLDSTAR TECHNOLOGY INC. 04E 01833 DT-75-33-09

### GS CMOS · GD4702B/GD4702BX

04E 01834

07-75-33-09

#### GS CMOS · GD4702B/GD4702BX

CRYSTAL SPECIFICATION RECOMMENDATIONS — Table 3 is a convenient listing of recommended crystal specifications.

Crystal manufacturers are also listed below.

#### TABLE 3 CRYSTAL SPECIFICATIONS

| PARAMETERS              | TYPICAL CRYSTAL SPEC |  |  |  |

|-------------------------|----------------------|--|--|--|

| Frequency               | 2.4576 MHz "AT" Cut  |  |  |  |

| Series Resistance (Max) | 250 Ω                |  |  |  |

| Unwanted Modes          | −6 dB (Min)          |  |  |  |

| Type of Operation       | Parallel             |  |  |  |

| Load Capacitance        | 32 pF ±0.5           |  |  |  |

#### CRYSTAL MANUFACTURERS

CTS Knights, Inc. Sandwich, III. 60548 (815) 786-8411 Crystal #F1004

X - Tron Electronics 1869 National Ave. Hayward, Calif. (415) 783-2145

Erie Frequency Control 499 Lincoln St. Carlisle, Pa. 17013 (717) 249-2232 International Crystal Mfg. Company 10 No. Lee Oklahoma City, Okla. 73102 (405) 236-3741

Sentry Manufacturing Co. Crystal Park Chickasha, Oklahoma 73018 (405) 224-6780 Crystal # SGP 6-2.4576 or Crystal # SGP-7-2.4576

7-231

7