## DG200, DG201

## CMOS Dual/Quad SPST Analog Switches

The DG200 and DG201 solid state analog gates are designed using an improved, high voltage CMOS monolithic technology. They provide ease-of-use and performance advantages not previously available from solid state switches. Destructive latch-up of solid state analog gates has been eliminated by Harris' CMOS technology.

The DG200 and DG201 are completely specification and pinout compatible with the industry standard devices.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# DG200, DG201

CMOS Dual/Quad SPST Analog Switches

August 1997

## Features

- Switches Greater than 28V<sub>P-P</sub> Signals with  $\pm 15V$  Supplies

- · Break-Before-Make Switching (Typ)

| - | toff  |  |  |  |  |  |  | - |  |  |  |  |  |  |  |  |  | . 2 | 25 | 0r | IS |

|---|-------|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|-----|----|----|----|

| - | ton . |  |  |  |  |  |  | - |  |  |  |  |  |  |  |  |  | . : | 70 | 0r | ıs |

- TTL, DTL, CMOS, PMOS Compatible

- · Non-Latching with Supply Turn-Off

- · Complete Monolithic Construction

- · Industry Standard (DG200, DG201)

## **Applications**

- · Data Acquisition

- · Sample and Hold Circuits

- Operational Amplifier Gain Switching Networks

## Description

The DG200 and DG201 solid state analog gates are designed using an improved, high voltage CMOS monolithic technology. They provide ease-of-use and performance advantages not previously available from solid state switches. Destructive latch-up of solid state analog gates has been eliminated by Harris' CMOS technology.

The DG200 and DG201 are completely specification and pinout compatible with the industry standard devices.

## Ordering Information

| PART NUMBER  | TEMP. RANGE<br>(°C) | PACKAGE          | PKG.<br>NO. |

|--------------|---------------------|------------------|-------------|

| DG200AA      | -55 to 125          | 10 Pin Metal Can | T10.B       |

| DG200AK      | -55 to 125          | 14 Ld CERDIP     | F14.3       |

| DG200BA      | -25 to 85           | 10 Pin Metal Can | T10.B       |

| DG200BK      | -25 to 85           | 14 Ld CERDIP     | F14.3       |

| DG200CJ      | 0 to 70             | 14 Ld PDIP       | E14.3       |

| DG200AA/883B | -55 to 125          | 10 Pin Metal Can | T10.B       |

| DG200AK/883B | -55 to 125          | 14 Ld CERDIP     | F14.3       |

| DG201AK      | -55 to 125          | 16 Ld CERDIP     | F16.3       |

| DG201BK      | -25 to 85           | 16 Ld CERDIP     | F16.3       |

| DG201CJ      | 0 to 70             | 16 Ld PDIP       | E16.3       |

| DG201AK/883B | -55 to 125          | 16 Ld CERDIP     | F16.3       |

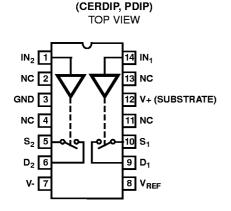

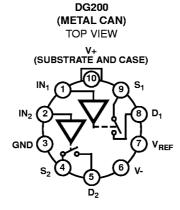

## **Pinouts**

DG200

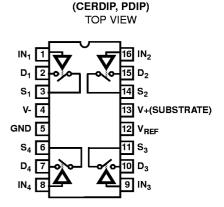

DG201

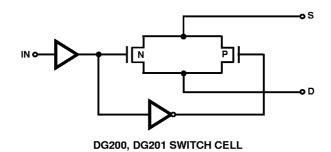

## **Schematic Diagram** $(^1/_2 DG200, ^1/_4 DG201)$ Q3 Q14 Q15 7 $V_{\text{REF}}$ Q1 Q12 7 **市**Q13 Q2 GATE PROTECTION RESISTOR

Q11

## Functional Diagram

INPUT

#### DG200

#### **Absolute Maximum Ratings Thermal Information** $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W) Thermal Resistance (Typical, Note 1) CERDIP Package ..... 75 20 100 N/A 155 67 Maximum Junction Temperature **Operating Conditions** Ceramic Package .......175°C Temperature Range Maximum Storage Temperature Range . . . . . . . -65°C to 150°C Maximum Lead Temperature (Soldering 10s)......300°C "B" Suffix . . . . . . . . . . . . . . . . . -25°C to 85°C "C" Suffix......0°C to 70°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Electrical Specifications** $T_A = 25^{\circ}C$ , $V_{+} = +15V$ , $V_{-} = -15V$ , GND = 0V

|                                                                       |                                                                      |       | MILITARY | ,     | СОММЕ           | RCIAL/IND | USTRIAL         |       |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|-------|----------|-------|-----------------|-----------|-----------------|-------|

| PARAMETER                                                             | TEST CONDITIONS                                                      | -55°C | 25°C     | 125°C | 0°C TO<br>-25°C | 25°C      | 70°C TO<br>85°C | UNITS |

| Input Logic Current,<br>I <sub>IN(ON)</sub>                           | V <sub>IN</sub> = 0.8V (Notes 2, 3)                                  | 10    | ±1       | ±10   | -               | ±10       | ±10             | μΑ    |

| Input Logic Current,<br>I <sub>N(OFF)</sub>                           | V <sub>IN</sub> = 2.4V (Notes 2, 3)                                  | ±10   | ±1       | ±10   | -               | ±10       | ±10             | μА    |

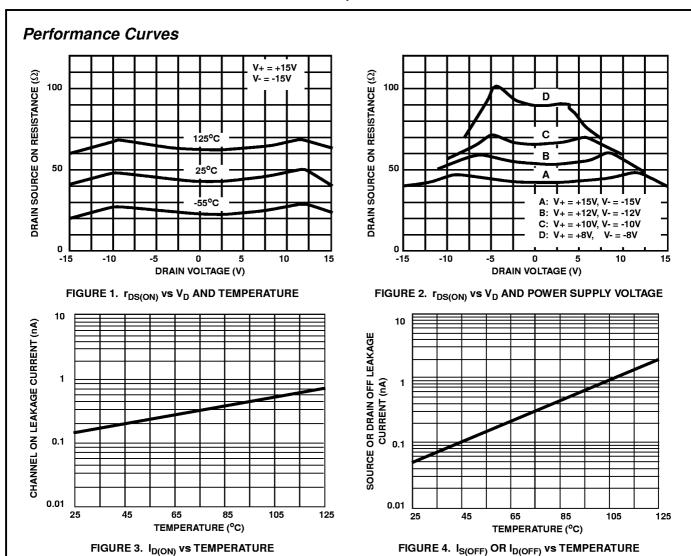

| Drain-Source On Resistance,  rDS(ON)                                  | $I_S = 10$ mA, $V_{ANALOG} = \pm 10$ V                               | 70    | 70       | 100   | 80              | 80        | 100             | Ω     |

| Channel-to-Channel r <sub>DS(ON)</sub> Match, r <sub>DS(ON)</sub>     |                                                                      | -     | 25 (Typ) | -     | -               | 30 (Typ)  | -               | Ω     |

| Minimum Analog Signal Handling<br>Capability, V <sub>ANALOG</sub>     |                                                                      | -     | ±15V     | -     | -               | ±15V      | -               | V     |

| Switch OFF Leakage Current, I <sub>D(OFF)</sub>                       | $V_{ANALOG} = -14V \text{ to } +14V$                                 | -     | ±2       | 100   | -               | ±5        | 100             | nA    |

| Switch OFF Leakage Current, I <sub>S(OFF)</sub>                       | $V_{ANALOG} = -14V \text{ to } +14V$                                 | -     | ±2       | 100   | -               | ±5        | 100             | nA    |

| Switch ON Leakage Current, $I_{D(ON)} + I_{S(ON)}$                    | $V_D = V_S = -14V \text{ to } +14V$                                  | -     | ±2       | 200   | -               | ±10       | 200             | nA    |

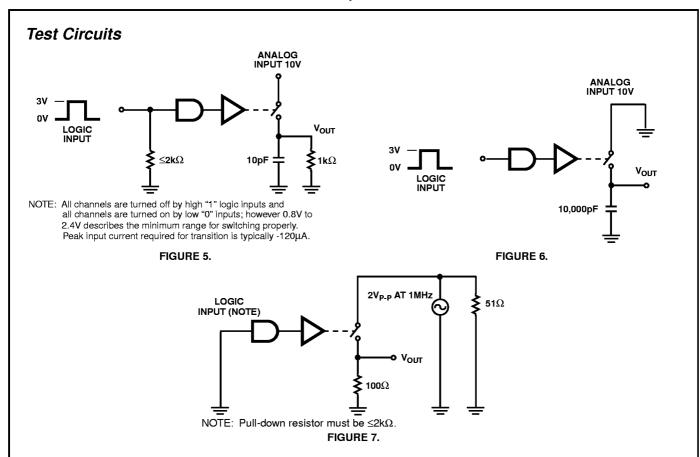

| Switch "ON" Time (Note 1), t <sub>ON</sub>                            | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)         | -     | 1.0      | -     | -               | 1.0       | -               | μs    |

| Switch "OFF" Time, t <sub>OFF</sub>                                   | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)         | -     | 0.5      | -     | -               | 0.5       | -               | μs    |

| Charge Injection, Q <sub>(INJ)</sub>                                  | Figure 6                                                             | -     | 15 (Typ) | -     | -               | 20 (Typ)  | -               | mV    |

| Minimum Off Isolation Rejection Ratio, OIRR                           | $ f = 1 MHz, R_L = 100 \Omega, $ $ C_L \le 5 pF (Figure 7, Note 1) $ | -     | 54 (Typ) | -     | -               | 50 (Typ)  | -               | dB    |

| +Power Supply<br>Quiescent Current, I <sub>V1</sub>                   | $V_{IN} = 0V$ to $V_{IN} = 5V$                                       | 1000  | 1000     | 2000  | 1000            | 1000      | 2000            | μА    |

| -Power Supply<br>Quiescent Current, I <sub>V2</sub>                   |                                                                      | 1000  | 1000     | 2000  | 1000            | 1000      | 2000            | μА    |

| Minimum Channel to Channel<br>Cross Coupling Rejection Ratio,<br>CCRR | One Channel Off                                                      | -     | 54 (Typ) | -     | -               | 50 (Typ)  | -               | dB    |

## NOTES:

- 1. Pull Down Resistor must be  $\leq 2k\Omega$ .

- 2. Typical values are for design aid only, not guaranteed and not subject to production testing.

- 3. All channels are turned off by high "1" logic inputs and all channels are turned on by low "0" inputs; however 0.8V to 2.4V describes the minimum range for switching properly. Peak input current required for transition is typically -120µA.

## DG201

#### **Absolute Maximum Ratings Thermal Information** V+ to V-....<36V Thermal Resistance (Typical, Note 1) $\theta_{JA} \, (^{o}\text{C/W}) \quad \theta_{JC} \, (^{o}\text{C/W})$ 20 145 N/A Maximum Junction Temperature V<sub>REF</sub> to V-.....<33V $V_{REF}$ to $V_{IN}. \dots <30 V$ Ceramic Package ......175°C $V_{\mathsf{REF}}$ to GND . . . . . <20V Maximum Storage Temperature Range .....-65°C to 150°C Maximum Lead Temperature (Soldering 10s)......300°C

## **Operating Conditions**

Temperature Range

| "A" Suffix | -55°C to 125°C |

|------------|----------------|

| "B" Suffix | 25°C to 85°C   |

| "C" Suffix | 0°C to 70°C    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $T_A = 25^{\circ}C$ , $V_{+} = +15V$ , $V_{-} = -15V$

|                                                                       |                                                                  |       | MILITARY     | ,     | RCIAL/INI       | DUSTRIAL     |                 |       |

|-----------------------------------------------------------------------|------------------------------------------------------------------|-------|--------------|-------|-----------------|--------------|-----------------|-------|

| PARAMETER                                                             | TEST CONDITIONS                                                  | -55°C | 25°C         | 125°C | 0°C TO<br>-25°C | 25°C         | 70°C TO<br>85°C | UNITS |

| Input Logic Current, I <sub>IN(ON)</sub>                              | V <sub>IN</sub> = 0.8V (Note 1)                                  | ±10   | ±1           | 10    | ±1              | ±1           | ±10             | μΑ    |

| Input Logic Current, I <sub>N(OFF)</sub>                              | V <sub>IN</sub> = 2.4V (Note 1)                                  | ±10   | ±1           | 10    | ±1              | ±1           | ±10             | μΑ    |

| Drain-Source On Resistance, r <sub>DS(ON)</sub>                       | $I_S = 10$ mA, $V_{ANALOG} = \pm 10$ V                           | 80    | 80           | 125   | 100             | 100          | 125             | Ω     |

| Channel-to-Channel r <sub>DS(ON)</sub> Match, r <sub>DS(ON)</sub>     |                                                                  | -     | 25 (Typ)     | -     | -               | 30 (Typ)     | -               | Ω     |

| Minimum Analog Signal Handling<br>Capability, V <sub>ANALOG</sub>     |                                                                  | -     | ±15<br>(Typ) | -     | -               | ±15<br>(Typ) | -               | V     |

| Switch OFF Leakage Current, I <sub>D(OFF)</sub>                       | $V_{ANALOG} = -14V \text{ to } +14V$                             | -     | ±1           | 100   | -               | ±5           | 100             | nA    |

| Switch OFF Leakage Current, I <sub>S(OFF)</sub>                       | $V_{ANALOG} = -14V \text{ to } +14V$                             | -     | ±1           | 100   | -               | ±5           | 100             | nA    |

| Switch ON Leakage<br>Current, I <sub>D(ON)</sub> + I <sub>S(ON)</sub> | $V_D = V_S = -14V \text{ to } +14V$                              | -     | ±2           | 200   | -               | ±5           | 200             | nA    |

| Switch "ON" Time<br>(Note 2), t <sub>ON</sub>                         | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)     | -     | 1.0          | -     | -               | 1.0          | -               | μs    |

| Switch "OFF" Time (Note 2), t <sub>OFF</sub>                          | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)     | -     | 0.5          | -     | -               | 0.5          | -               | μs    |

| Charge Injection, Q <sub>(INJ)</sub>                                  | Figure 6                                                         | -     | 15 (Typ)     | -     | -               | 20 (Typ)     | -               | mV    |

| Minimum Off Isolation Rejection Ratio, OIRR                           | $ f = 1 MHz, R_L = 100 \Omega,                                 $ | -     | 54 (Typ)     | -     | -               | 50 (Typ)     | -               | dB    |

| +Power Supply Quiescent Current, I+Q                                  | $V_{IN} = 0V$ to $V_{IN} = 5V$                                   | 2000  | 1000         | 2000  | 2000            | 1000         | 2000            | μА    |

| -Power Supply Quiescent Current,<br>I-Q                               |                                                                  | 2000  | 1000         | 2000  | 2000            | 1000         | 2000            | μА    |

| Minimum Channel to Channel Cross<br>Coupling Rejection Ratio, CCRR    | One Channel Off                                                  | -     | 54 (Typ)     | -     | -               | 50 (Typ)     | -               | dB    |

## NOTES

- 1. Typical values are for design aid only, not guaranteed and not subject to production testing.

- 2. All channels are turned off by high "1" logic inputs and all channels are turned on by low "0" inputs; however 0.8V to 2.4V describes the minimum range for switching properly. Peak input current required for transition is typically -120µA.

## Pin Descriptions

| DG200 (14 LEAD DIP) |                 |                                            |  |  |  |  |  |

|---------------------|-----------------|--------------------------------------------|--|--|--|--|--|

| PIN                 | SYMBOL          | DESCRIPTION                                |  |  |  |  |  |

| 1                   | IN <sub>2</sub> | Logic Control for Switch 2                 |  |  |  |  |  |

| 2                   | NC              | No Connection                              |  |  |  |  |  |

| 3                   | GND             | Ground Terminal (Logic Common)             |  |  |  |  |  |

| 4                   | NC              | No Connection                              |  |  |  |  |  |

| 5                   | S <sub>2</sub>  | Source (Input) Terminal for Switch 2       |  |  |  |  |  |

| 6                   | $D_2$           | Drain (Output) Terminal for Switch 2       |  |  |  |  |  |

| 7                   | V-              | Negative Power Supply Terminal             |  |  |  |  |  |

| 8                   | $V_{REF}$       | Logic Reference Voltage                    |  |  |  |  |  |

| 9                   | D <sub>1</sub>  | Drain (Output) Terminal for Switch 1       |  |  |  |  |  |

| 10                  | S <sub>1</sub>  | Source (Input) Terminal for Switch 1       |  |  |  |  |  |

| 11                  | NC              | No Connection                              |  |  |  |  |  |

| 12                  | V+              | Positive Power Supply Terminal (Substrate) |  |  |  |  |  |

| 13                  | NC              | No Connection                              |  |  |  |  |  |

| 14                  | IN <sub>1</sub> | Source (Input) Terminal for Switch 1       |  |  |  |  |  |

| DG201 (16 LEAD DIP) |                 |                                            |  |  |  |  |  |  |

|---------------------|-----------------|--------------------------------------------|--|--|--|--|--|--|

| PIN                 | SYMBOL          | DESCRIPTION                                |  |  |  |  |  |  |

| 1                   | IN <sub>1</sub> | Logic Control for Switch 1                 |  |  |  |  |  |  |

| 2                   | D <sub>1</sub>  | Drain (Output) Terminal for Switch 1       |  |  |  |  |  |  |

| 3                   | S <sub>1</sub>  | Source (Input) Terminal for Switch 1       |  |  |  |  |  |  |

| 4                   | V-              | Negative Power Supply Terminal             |  |  |  |  |  |  |

| 5                   | GND             | Ground Terminal (Logic Common)             |  |  |  |  |  |  |

| 6                   | S <sub>4</sub>  | Source (Input) Terminal for Switch 4       |  |  |  |  |  |  |

| 7                   | D <sub>4</sub>  | Drain (Output) Terminal for Switch 4       |  |  |  |  |  |  |

| 8                   | IN <sub>4</sub> | Logic Control for Switch 4                 |  |  |  |  |  |  |

| 9                   | IN <sub>3</sub> | Logic Control for Switch 3                 |  |  |  |  |  |  |

| 10                  | $D_3$           | Drain (Output) Terminal for Switch 3       |  |  |  |  |  |  |

| 11                  | $S_3$           | Source (Input) Terminal for Switch 3       |  |  |  |  |  |  |

| 12                  | $V_{REF}$       | Logic Reference Voltage                    |  |  |  |  |  |  |

| 13                  | V+              | Positive Power Supply Terminal (Substrate) |  |  |  |  |  |  |

| 14                  | S <sub>2</sub>  | Source (Input) Terminal for Switch 2       |  |  |  |  |  |  |

| 15                  | D <sub>2</sub>  | Drain (Output) Terminal for Switch 2       |  |  |  |  |  |  |

| 16                  | IN <sub>2</sub> | Logic Control for Switch 2                 |  |  |  |  |  |  |

## Typical Applications

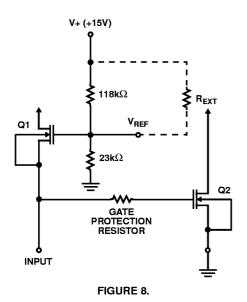

## Using the V<sub>REF</sub> Terminal

The DG200 and DG201 have an internal voltage divider setting the TTL threshold on the input control lines for V+ equal to +15V. The schematic shown in Figure 8 with nominal resistor values, gives approximately 2.4V on the  $V_{REF}$  pin. As the TTL input signal goes from +0.8V to +2.4V, Q1 and Q2 switch states to turn the switch ON and OFF.

If the power supply voltage is less than +15V, then a resistor must be added between V+ and the  $V_{REF}$  pin, to restore +2.4V at  $V_{REF}$ . The table shows the value of this resistor for various supply voltages, to maintain TTL compatibility. If CMOS logic levels with a +5V supply are being used, the threshold shifts are less critical, but a separate column of suitable values is given in the table. For logic swings of -5V to +5V, no resistor is needed.

In general, the "low" logic level should be <0.8V to prevent Q1 and Q2 from both being ON together (this will cause incorrect switch function).

TABLE 1.

| V+ SUPPLY (V) | TTL RESISTOR ( $\mathbf{k}\Omega$ ) | CMOS RESISTOR ( $\mathbf{k}\Omega$ ) |

|---------------|-------------------------------------|--------------------------------------|

| +15           | -                                   | -                                    |

| +12           | 420                                 | -                                    |

| +10           | 190                                 | -                                    |

| +9            | 136                                 | 136                                  |

| +8            | 98                                  | 98                                   |

| +7            | 70                                  | 70                                   |

## Die Characteristics

**DIE DIMENSIONS:**

75 mils x 78 mils x 14 mils

**METALLIZATION:**

Type: Al

Thickness: 10kÅ

## **PASSIVATION:**

Type:  $SiO_2/Si_3N_4$  $SiO_2$  Thickness:  $7k\mathring{A}$  $Si_3N_4$  Thickness:  $8k\mathring{A}$

## **WORST CASE CURRENT DENSITY:**

1 x 10<sup>5</sup> A/cm<sup>2</sup>

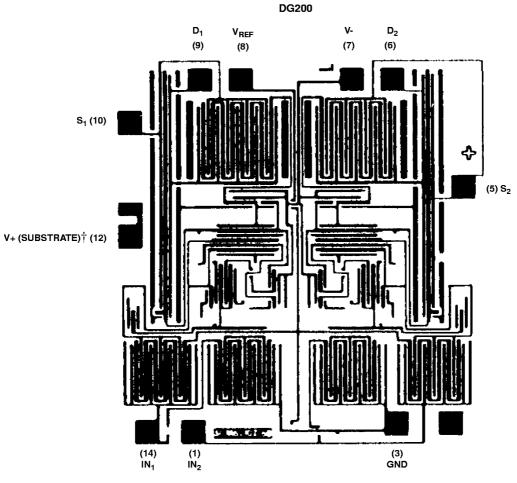

## Metallization Mask Layout

\*BACKSIDE OF CHIP IS V+

## Die Characteristics

## **DIE DIMENSIONS:**

94 mils x 101 mils x 14 mils

## **METALLIZATION:**

Type: Al

Thickness: 10kÅ

## **PASSIVATION:**

Type:  $SiO_2/Si_3N_4$  $SiO_2$  Thickness:  $7k\mathring{A}$  $Si_3N_4$  Thickness:  $8k\mathring{A}$

## **WORST CASE CURRENT DENSITY:**

1 x 10<sup>5</sup> A/cm<sup>2</sup>

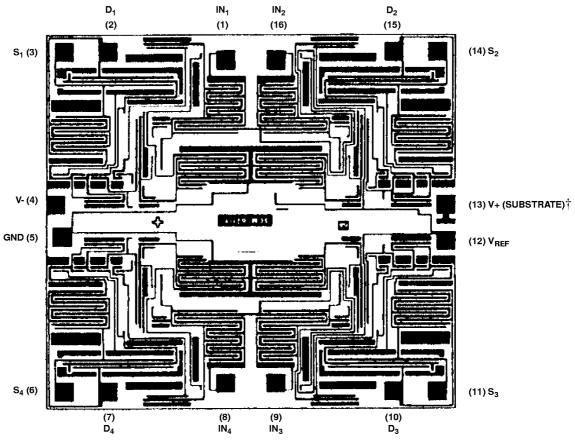

## Metallization Mask Layout

## DG201

† BACKSIDE OF CHIP IS V+