# C\$8221 NEW ENHANCED AT (NEAT™) DATA BOOK 82C211/82C212/82C215/82C206 (IPC) CHIPSet™

- 100% IBM™ PC/AT Compatible New Enhanced CHIPSet™ for 12MHz to 16MHz systems

- Supports 16MHz 80286 operation with only 0.5-0.7 wait states for 100ns DRAMs and 12 MHz operation with 150ns DRAMs, 0 wait state 12MHz operation with 80ns DRAMs

- Separate CPU and AT Bus clocks

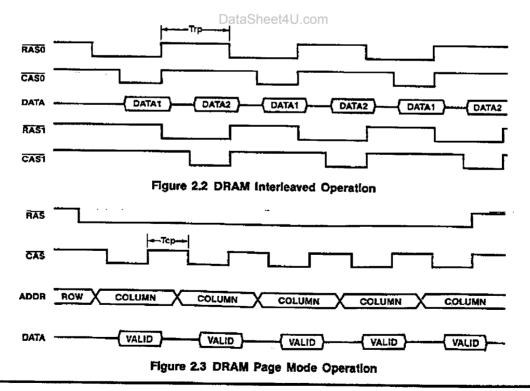

- Page Interleaved Memory supports single bank page mode, 2 way and 4 way page interleaved mode

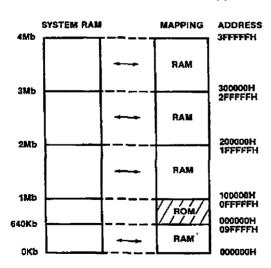

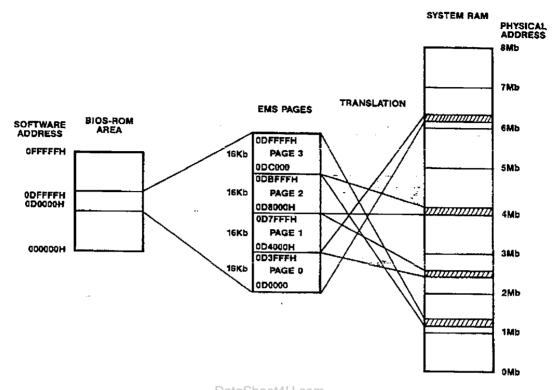

- Integrated Lotus-Intel-Microsoft Expanded Memory Specification (LIM EMS) Memory Controller. Supports EMS 4.0.

The CS8221 PC/AT compatible NEAT CHIPSet™ is an enhanced, high performance 4 chip VLSI implementation (including the 82C206 IPC) of the control logic used on the IBM™ Personal Computer AT. The flexible

- Software Configurable Command Delays, Wait states and Memory Organization

- Optimized for OS/2 operation

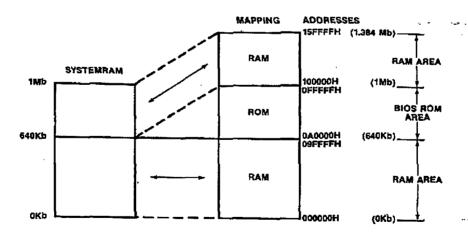

- Shadow RAM for BIOS and video ROM to improve system performance

- Complete AT/286 system board requires only 28 logic components plus memory and processor

- Targeted at Desktop PC/ATs, Laptops and CMOS Industrial Control Applications

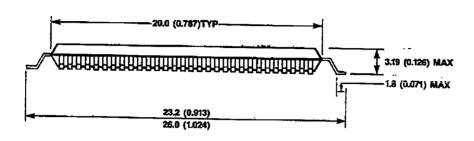

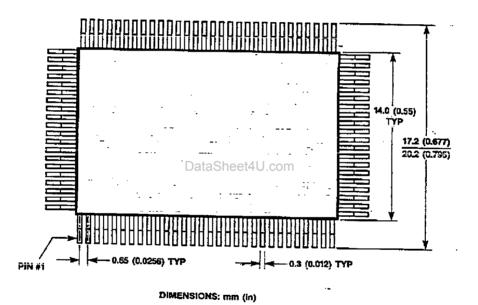

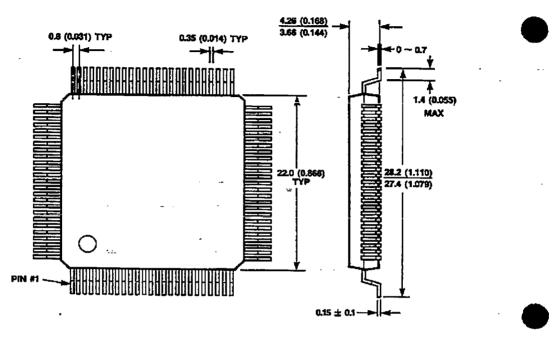

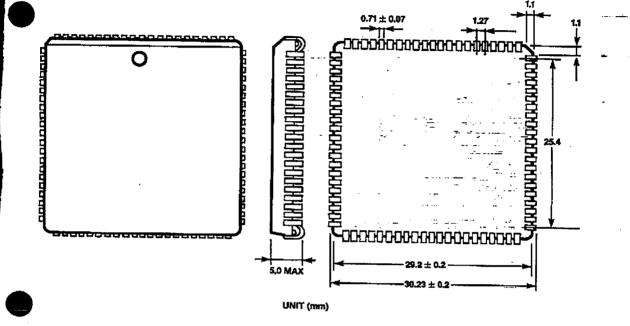

- Available as four CMOS 84-pin PLCC or 100-pin PFP components.

architecture of the NEAT CHIPSet\* allows it to be used in any 80286 based system.

The CS 8221 NEAT CHIPSet™ provides a complete 286 PC/AT compatible system,

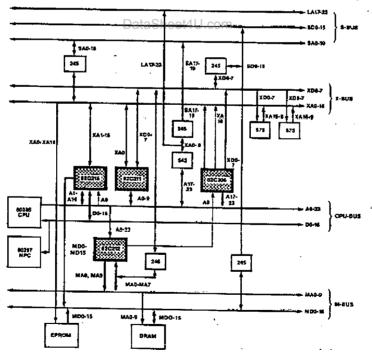

Figure 1. NEAT System Block Diagram

Publication No. 2-221-B

Printed in U.S.A. 8/89 Rev. 03

www.DataSheet4U.com

DataShe

requiring only 24 logic components plus memory devices.

The CS8221 NEAT CHIPSet™ consists of the 82C211 CPU/Bus controller, the 82C212 Page/Interleave and EMS Memory controller, the 82C215 Data/Address buffer and the 82C206 Integrated Peripherals Controller (IPC).

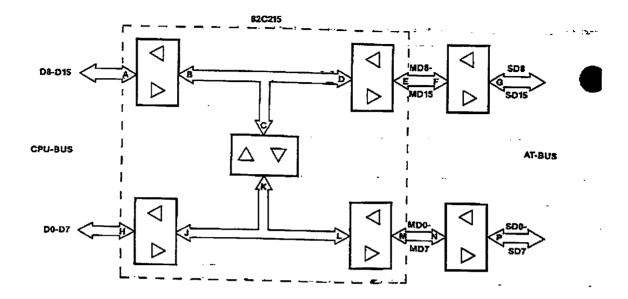

The NEAT CHIPSet™ supports the local CPU bus, a 16 bit system memory bus, and the AT buses as shown in the NEAT System Block Diagram. The 82C211 provides synchronization and control signals for all buses. The 82C211 also provides an independent AT bus clock and allows for dynamic selection between the processor clock and the user selectable AT bus clock. Command delays and wait states are software configurable, providing flexibility for slow or fast peripheral boards.

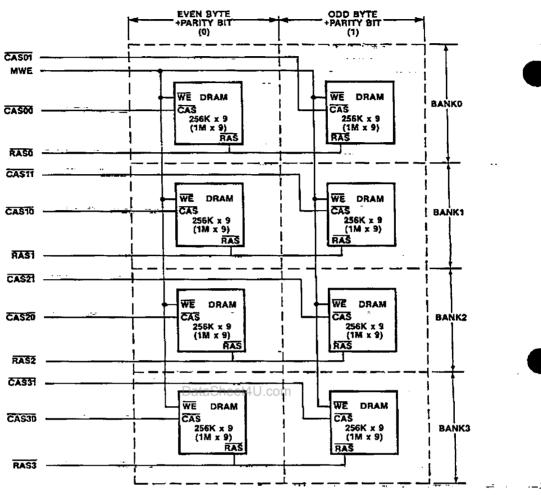

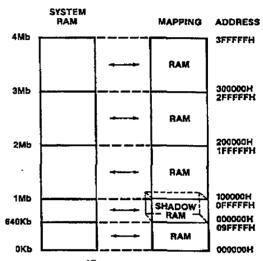

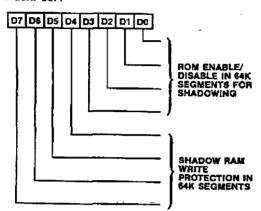

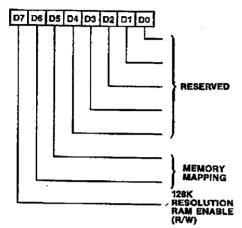

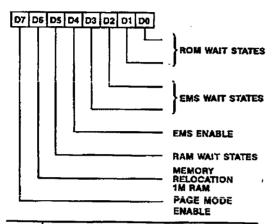

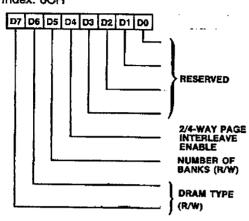

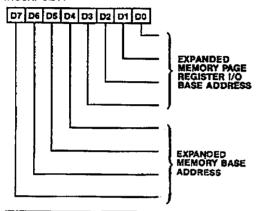

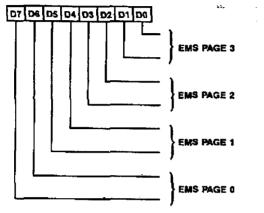

The 82C212 Page/Interleave and EMS Memory controller provides an interleaved memory sub-system design with page mode operation. It supports up to 8 MB of on-board DRAM with combinations of 64Kbit, 256Kbit and 1Mbit DRAMs. The processor can operate at 16MHz with 0.5–0.7 wait state memory accesses, using 100 nsec DRAMs. This is possible through the Page Interleaved memory scheme. The Shadow RAM feature allows faster execution of code stored in EPROM, by down loading code from EPROM to RAM. The RAM then shadows the EPROM for further code execution. In a DOS environment, memory above 1Mb can be treated as LIM EMS memory.

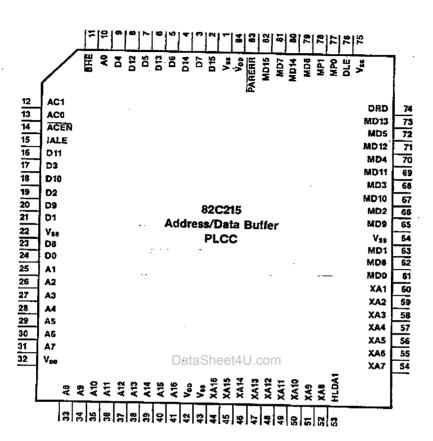

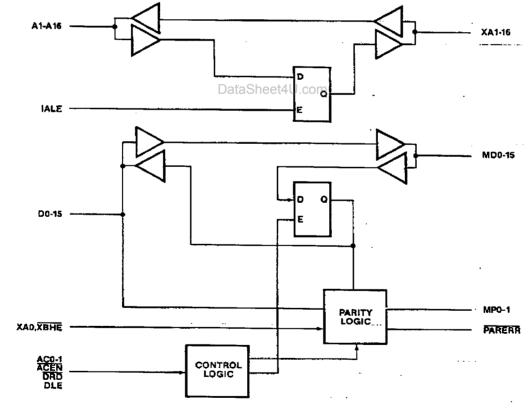

The 82C215 Data/Address buffer provides the buffering and latching between the local CPU address bus and the Peripheral address bus. It also provides buffering between the local

CPU data bus and the memory data bus. The parity bit generation and error detection logic resides in the 82C215.

The 82C206 Integrated Peripherals Controller is an integral part of the NEAT CHIPSet™. It is described in the 82C206 Integrated Peripherals Controller data book.

#### System Overview

The CS8221 NEAT CHIPSet™ is designed for use in 12 to 16 MHz 80286 based systems and provides complete support for the IBM PC/AT bus. There are four buses supported by the CS8221 NEAT CHIPSet™ as shown in Figure 1: CPU local bus (A and D), system memory bus (MA and MD), I/O channel bus (SA and SD), and X bus (XA and XD). The system memory bus is used to interface the CPU to the DRAMs and EPROMs controlled by the 82C212. The I/O channel bus refers to the bus supporting the AT bus adapters which could be either 8 bit or 16 bit devices. The X bus refers to the peripheral bus to which the 82C206 IPC and other peripherals are attached in an IBM PC/AT.

### eet4 **Notation and Glossary**

The following notations are used to refer to the configuration and diagnostics registers internal to the 82C211 and 82C212:

**REGNH** denotes the internal register of index n in hexadecimal notation.

REGnH<x:y> denotes the bit field from bits x to y of the internal register with index n in hexadecimal notation. DataShe

2

et4U.com

RESET4 12 13 14 15 16 17 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 ROMOS XIOW XIOR XMEMW XMEMR osc HLDA1 REF 82C212 Memory Interleaved/Page OSC/12 VIII

X1

X2

LMEGES

XDEN

XDIR

MWE Controller **PLCC** READY GATEA20 A20 Voo M/IQ 54

3

DataSheet4U.com

www.DataSheet4U.com

DataShee

4

DataShe

et4U.com

DataSheet4U.com

www.DataSheet4U.com

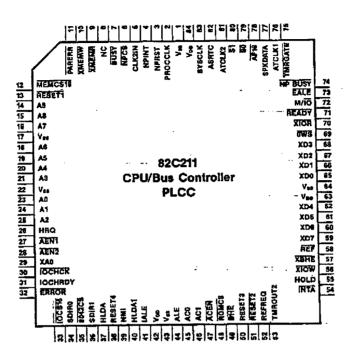

## 82C211 Pin Description

| Pin<br>No. | Pin<br>Type | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks     |             |         | . •                                                                                                                                                                                                                                                                                                                                                                                               |

| 5          | i           | CLK2IN  | CLOCK 2 Input from a TTL crystal oscillator having a maximum of twice the rated frequency of the 80286 processor clock.                                                                                                                                                                                                                                                                           |

| 2          | 0           | PROCCLK | PROCESSOR CLOCK output for the 80286 and the 82C212. It is derived from CLK2IN. It can also be programmed to be derived from ATCLK.                                                                                                                                                                                                                                                               |

| 76         | 1           | ATCLK1  | AT Bus Clock 1 input source from crystal or oscillator. This clock input is used for the AT bus operation and is only required if the AT bus state machine clock, BCLK (internal) will not be derived from CLK2IN. This clock input should be tied low if not used. Its frequency should be lower than CLK2IN. BCLK is the AT bus state machine clock and can be programmed to be equal to ATCLK. |

| 81         | 0           | ATCLK2  | AT Bus Clock 2 output is connected to the crystal (if a crystal is used to generate AT bus clock). A series damping resistor of 10 ohms should be used to reduce amplitude of the resonant circuit. It should be left open if a TTL oscillator is used.                                                                                                                                           |

| 83         | 0           | SYSCLK  | AT System Clock output is buffered to drive the SYSCLK line on the AT bus I/O channel. It is half the frequency of BCLK and should be between 6 and 8 MHz for maintaining correct AT I/O bus timing compatibility with the IBM™ PC/AT.                                                                                                                                                            |

| Control    |             |         |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13         | 3           | RESET1  | RESET1 is an active low input generated by the power good signal of the power supply. When low, it activates RESET3 and RESET4. RESET1 is latched internally.                                                                                                                                                                                                                                     |

| 51         | I           | RESET2  | RESET2 is an active low input generated from the keyboard controller (8042/8742) for a "warm reset" not requiring the system power to be shut off. It forces a CPU reset by activating RESET3.                                                                                                                                                                                                    |

| 38         | 0           | RESET4  | RESET4 is an active high output used to reset the AT bus, 82C206 IPC, 8042 keyboard controller, 82C212 memory controller. It is synchronized with the processor clock.                                                                                                                                                                                                                            |

| 50         | O           | RESET3  | RESET3 is an active high output to the 80286 when RESET1 or RESET2 is active. It is also activated when shut-down condition in the CPU is detected. RESET3 will stay active for at least 16 PROCLK cycles.                                                                                                                                                                                        |

et4U.com

DataShe

----

## 82C211 Pin Description (Continued)

| Pin<br>No. | Pin<br>Type | Symbol        | Description                                                                                                                                                                                                                                                                                                                        |

|------------|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Inte   | erface      |               |                                                                                                                                                                                                                                                                                                                                    |

| 71         | 1/0         | READY         | READY as an output, is driven low to terminate the current CPU cycle after IOCHRDY is high and 0WS is high, or if "time out" condition is detected. During all other cycles, it is an input from the 82C212. It is an open collector output requiring an external pull-up resistor of 1KΩ and is connected to the 80286 READY pin. |

| 79, 80     | İ           | <u>sō, sī</u> | STATUS is an active low input from the CPU. The status signals are used by the 82C211 to determine the state of the CPU. Pull up resistors of $10K\Omega$ each should be provided.                                                                                                                                                 |

| 72         |             | M/ĪŌ          | MEMORY INPUT/OUTPUT is the signal from the CPU. When high, it indicates a memory access, when low it indicates an I/O access. It is used to generate memory and I/O signals for the system. A 10KΩ pull up resistor is recommended.                                                                                                |

| 55         | 0           | HOLD          | CPU HOLD REQUEST is an active high output to the CPU. It is activated during DMA, Master or refresh cycles.                                                                                                                                                                                                                        |

| 37         | ı           | HLDA          | HOLD ACKNOWLEDGE is an active high input generated by the CPU to indicate to the requesting master that it has relinquished the bus. When active, it forces all commands (IOR, IOW, MEMR, MEMW, INTA) to be tri-stated.                                                                                                            |

| 49         | 1/0         | BHE           | BYTE HIGH ENABLE is an active low signal which indicates the transfer of data on the upper byte of the data bus, in conjunction with A0, it is input during CPU cycles and in conjunction with XA0, it is output during DMA, MASTER cycles. A pull up resistor of 10KΩ is required.                                                |

| 39         | 0           | NMI           | NON MASKABLE INTERRUPT is an active high output to the NMI pin of the CPU and is generated by the 82C211 to invoke a non-maskable interrupt.                                                                                                                                                                                       |

| 41         | 0           | IALE          | ADDRESS LATCH ENABLE (INTERNAL) is an active high output synchronized with PROCCLK and controls address latches used to hold addresses during bus cycles. It is not issued for halt bus cycles.                                                                                                                                    |

et4U.com

DataShee

### 82C211 Pin Description (Continued)

| Pin<br>No. | Pin<br>Type   | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Cha    | nnel Interfac | ce      |                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31         | 1             | IOCHRDY | I/O CHANNEL READY is an active high input from the AT bus. When low it indicates a not ready condition and inserts wait states in AT-I/O or AT-memory cycles. When high it allows termination of the current AT-bus cycle. A series damping resistor of 53Ω at the AT bus connector is recommended to limit the negative under shoot. A 1KΩ pull up resistor is required for this open collector line. |

| 30         |               | IOCHCK  | I/O CHANNEL CHECK is an active low input from the AT bus causing an NMI to be generated if enabled. It is used to signal an I/O error condition from a device residing on the AT bus. A 10KΩ pull up resistor is required.                                                                                                                                                                             |

| 11         | l             | PARERR  | PARITY ERROR is an active low input from the 82C215 which causes an NMI if enabled. It indicates a parity error in local system memory.                                                                                                                                                                                                                                                                |

| 44         | 0             | ALE -   | ADDRESS LATCH ENABLE is an active high output to the AT bus and is synchronized with the AT state machine clock. It controls the address latches used to hold the addresses during bus cycles. This signal should be buffered to drive the AT bus.                                                                                                                                                     |

| 73 .       | 0             | EALE    | EXTERNAL ADDRESS LATCH ENABLE is an active low output used to latch the CPU A17-A23 address lines to the LA17-LA23 lines on the AT bus.                                                                                                                                                                                                                                                                |

| DMA Ir     | terface       |         | 44                                                                                                                                                                                                                                                                                                                                                                                                     |

| 40         | 0             | HLDA1   | HOLD ACKNOWLEDGE 1 is an active high output when a bus cycle is granted in response to HOLD REQUEST.                                                                                                                                                                                                                                                                                                   |

| 26         | 1             | HRQ     | HOLD REQUEST is an active high input when DMA/Master is requesting a bus cycle. For an AT compatible architecture, it should be connected to the HOLD REQUEST signal from DMA1 and DMA2.                                                                                                                                                                                                               |

| 27         | 1             | AEN1    | ADDRESS ENABLE 1 is an active low input from one of the two DMA controllers enabling the address latches for 8 bit DMA transfers.                                                                                                                                                                                                                                                                      |

| 28         | I             | AEN2    | ADDRESS ENABLE 2 is an active low input from one of the two DMA controllers enabling the address latches for 16 bit DMA transfers.                                                                                                                                                                                                                                                                     |

| 48         | 1             | ROMOS   | ROM CHIP-SELECT is an active low input from the 82C212. It is used to disable parity checks for local ROM cycles.                                                                                                                                                                                                                                                                                      |

et4U.com

DataShee

- 45.

## 82C211 Pin Description (Continued)

| Pin<br>No. | Pin<br>Type | Symbol  | Description                                                                                                                                                                                                                           |

|------------|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Inpu   | ıts         |         |                                                                                                                                                                                                                                       |

| 12         | ı           | MEMCS16 | MEMORY CHIP SELECT 16 is an active low input from the AT bus indicating a 16 bit memory transfer. If high it implies an 8 bit memory transfer. A pull up resistor of 330Ω is required.                                                |

| 33         | Ī           | IOCS16  | I/O CHANNEL SELECT 16 is an active low input from the AT bus indicating a 16 bit I/O transfer. If high it implies an 8 bit I/O transfer. A pull up resistor of 330Ω is required.                                                      |

| 69         | 1           | 0WS     | ZERO WAIT STATES is an active low input from the AT bus, causing immediate termination of the current AT bus cycle. Memories requiring zero wait states use this line to speed up memory cycles. It requires a 330Ω pull up resistor. |

| Device I   | Decode      |         |                                                                                                                                                                                                                                       |

| 35         | 0           | 8042CS  | 8042 CHIP SELECT is an active low signal for the keyboard controller chip select.                                                                                                                                                     |

| 82         | 0           | ASRTC   | ADDRESS STROBE to Real Time Clock is an active high signal used on the 82C206.                                                                                                                                                        |

| Refresh    | ,           |         |                                                                                                                                                                                                                                       |

| 52         |             | REFREQ  | REFRESH REQUEST is an input active on rising edge initiating a DRAM refresh sequence. It is generated by the 8254 compatible timer controller #1 of the 82C206 IPC in a PC/AT implementation.                                         |

| 58         | 1/0         | REF .   | REFRESH is an active low signal. As an open drain output, it initiates a refresh cycle for the DRAMs. As an input, it can be used to force a refresh cycle from an I/O device. An external pull up of 620Ω is required.               |

| X Bus in   | terface     |         |                                                                                                                                                                                                                                       |

| 9          | 1/0         | XMEMR   | X BUS MEMORY READ is an active low control strobe directing memory to place data on the data bus. It is an output if the CPU is controlling the bus and is an input if a DMA controller is in control of the bus.                     |

| 10         | 1/0         | XMEMW   | X BUS MEMORY WRITE is an active low control strobe directing memory to accept data from the data bus, it is an output if the CPU is controlling the bus and is an input if a DMA controller is in control of the bus.                 |

et4U.com

DataShee

### 82C211 Pin Description (Continued)

| Pin<br>No.     | Pin<br>Type  | Symbol             | Description                                                                                                                                                                                                                                                             |

|----------------|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70             | 1/0          | XIOR               | X BUS I/O READ is an active low strobe directing an I/O port to place data on the data bus. It is an output if the CPU is controlling the bus and is an input if a DMA controller is in control of the bus.                                                             |

| 56             | 1/0          | XIOW               | X BUS I/O WRITE is an active low strobe directing an I/O port to accept data from the data bus. It is an output if the CPU is controlling the bus and is an input if a DMA controller is in control of the bus.                                                         |

| 57             | 1/0          | XBHE               | X BYTE HIGH ENABLE is an active low signal indicating the high byte has valid data on the bus. It is an output when the CPU is in control of the bus and is an input when a DMA controller is in control of the bus. A 4,7ΚΩ pull-up resistor is required on this line. |

| 59-62<br>65-68 | _ I/O<br>I/O | XD<7:4><br>XD<0:3> | X DATA BUS bits <7:0>                                                                                                                                                                                                                                                   |

| 8              |              | NC                 | No Connect                                                                                                                                                                                                                                                              |

| 75             | 0            | TMRGATE            | TIMER GATE is an active high output that enables the timer on the 8254 compatible counter timer in the 82C206 to enable the tone signal for the speaker.                                                                                                                |

| 53             | i            | TMROUT2            | TIMER OUT 2 is an active high input from the 8254 compatible counter timer in the 82C206 that can be read from port B.                                                                                                                                                  |

| 77             | 0            | SPKDATA            | SPEAKER DATA is an active high output used to gate the 8254 compatible tone signal of the 82C206 to the speaker.                                                                                                                                                        |

| 54             | 0            | INTA               | INTERRUPT ACKNOWLEDGE is an active low output to the 82C206 interrupt controller. It is also used to direct data from the X to S bus during an interrupt acknowledge cycle.                                                                                             |

| Buffer C       | ontrol       | _                  |                                                                                                                                                                                                                                                                         |

| 34             | 0            | SDIR0              | SYSTEM BUS DIRECTION 0 for the low byte. A low sets the data path from the S bus to the M bus. A high sets the data path from the M bus to the S bus.                                                                                                                   |

| 36             | 0            | SDIR1              | SYSTEM BUS DIRECTION 1 for the high byte. A low sets the data path from the S bus to the M bus. A high sets the data path from the M bus to the S bus                                                                                                                   |

| 47             | O            | ACEN               | ACTION CODE ENABLE is an active low output that validates the action code signals AC<1, 0> that are used by the 82C215 address/data buffer.                                                                                                                             |

et4U.com

DataShe

## 82C211 Pin Description (Continued)

| Pin<br>No.              | Pin<br>Type     | Symbol                     | Description                                                                                                                                                                                                         |

|-------------------------|-----------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46, 45                  | 0               | AC<1, 0>                   | ACTION CODE is a two bit encoded output command for bus size control and byte assembly operations performed in the 82C215.                                                                                          |

| Memory                  | Control         |                            |                                                                                                                                                                                                                     |

| 78                      | 1               | AF16                       | AF16 is an active low input indicating that the current cycle is a local bus cycle. A high indicates an AT bus cycle. A 10KΩ pull up resistor is required.                                                          |

| 23-25<br>18-21<br>14-18 | I/O -           | A<0:2><br>A<3:6><br>A<7:9> | ADDRESS lines A0-A9 are input from the CPU. These lines are output during refresh. A1 is used to detect shut down condition of the CPU. A0 is used to generate the enable signal for the data bus transceivers.     |

| 29                      | 1/0             | XA0                        | ADDRESS line XA0 from the X bus. It is an output during CPU accesses on the X bus and is an input for 8 bit DMA cycles.                                                                                             |

| CoProces                | ssor Interfa    | Ce                         |                                                                                                                                                                                                                     |

| 6                       | 0               | NPCS                       | NUMERIC COPROCESSOR CHIP SELECT is an active low output signal used to select the internal registers of the 80287 NPX.                                                                                              |

| 7                       | 0               | BUSY                       | BUSY is an active low output to the CPU initiated by the 80287 NPX dindicatig that it is busy. A 4.7KΩ pull up resistor is required.                                                                                |

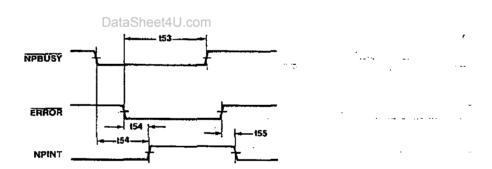

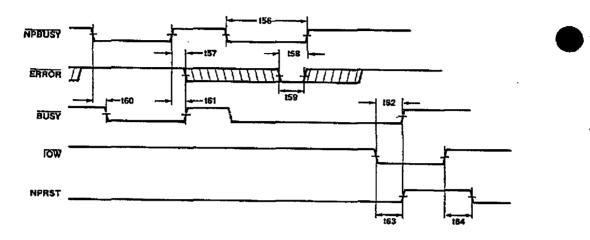

| 74                      | ı               | NPBUSY                     | NUMERIC COPROCESSOR BUSY is an active low input from the NPX, indicating that it is currently executing a command. It is used to generate the BUSY signal to the CPU. A 4.7KΩ pull up resistor is required.         |

| 32 -                    | -l <sup>:</sup> | ERROR                      | ERROR is an active low input from the NPX indicating that an unmasked error condition exists. A 4.7K $\Omega$ pull up resistor is required.                                                                         |

| 4                       | 0               | NPINT                      | NUMERIC COPROCESSOR INTERRUPT is an active high output. It is an interrupt request from the 80287 and is connected to the IRQ13 line of the 82C206 IPC in a PC/AT environment. A 10KΩ pull up resistor is required. |

et4U.com

DataShee

## 82C211 Pin Description (Continued)

| Pin<br>No.          | Pin<br>Type | Symbol | Description                                                                                                                                                                                                       |  |

|---------------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3                   | 0           | NPRST  | NUMERICAL PROCESSOR RESET is an active high reset to the 80287. It is active when RESET4 is active or when a write operation is made to Port 0F1H. In the later case, it is active for the period of the command. |  |

| Power Sup           | plies       |        |                                                                                                                                                                                                                   |  |

| 42, 63, 84          | _           | VDD    | POWER SUPPLY.                                                                                                                                                                                                     |  |

| 1, 17, 22<br>43, 64 |             | vss    | GROUND.                                                                                                                                                                                                           |  |

et4U.com

DataSheet4U.com

DataShe

11

DataSheet4U.com www.DataSheet4U.com

## 82C212 Pin Description

| Pin<br>No. | Pin<br>Type | Symbol   | Description                                                                                                                                                                                              |

|------------|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks and | Control     |          | ,                                                                                                                                                                                                        |

| 83         | 1           | PROCCLK  | PROCESSOR CLOCK input from the 82C211                                                                                                                                                                    |

| 23         | 1           | X1       | CRYSTAL 1 input from the 14.31818 MHz crystal.                                                                                                                                                           |

| 24         | 0           | X2 _     | CRYSTAL 2 output to the 14.31818 MHz crystal.                                                                                                                                                            |

| 18         | 0 :         | OSC.     | OSCILLATOR output for the system clock at 14.31818 MHz and 24 mA (on the 82C212 only).                                                                                                                   |

| 18         | 1/0         | OSC/ADTL | (On the 82C212B only.) Either ADTL input from the 82C631 Mapper chip, or OSC output, depending on the External EMS bit at register index 6FH, bit 4.                                                     |

| 21         | 0           | OSC/12   | OSCILLATOR divided by 12 is an output with a clock frequency equal to 1/12 of the crystal frequency across the X1, X2 pins.                                                                              |

| 12         | I           | RESET4   | RESET 4 is the active high reset input from the 82C211. It resets the configuration registers to their default values. When active, RAS<0:3> and CAS<00:31> remain high, OSC and OSC/12 remain inactive. |

| 20         | 1 .         | REF      | REFRESH is an active low input for DRAM refresh control from the 82C211. It initiates a refresh cycle for the DRAMs.                                                                                     |

| 65, 63     | 1 .         | S<1, 0>  | STATUS input lines from the CPU are active low. These lines are monitored to detect the start of a cycle.                                                                                                |

| 54         | ſ           | M/IO     | MEMORY I/O signal from the CPU. If high it indicates a memory cycle. If low, it indicates an I/O cycle.                                                                                                  |

| 15         | 1           | XIOR     | I/O READ command, input active low.                                                                                                                                                                      |

| 14         | 1           | XIOM     | I/O WRITE command, input active high.                                                                                                                                                                    |

| 17         | 1           | XMEMR    | X BUS MEMORY READ command, input active low.                                                                                                                                                             |

| 16         | Į.          | XMEMW    | X BUS MEMORY WRITE command, input active low.                                                                                                                                                            |

| 19         | 1           | HLDA1    | HOLD ACKNOWLEDGE 1 is an active high input from the 82C211. It is used to generate RAS, CAS signals for DMA cycles, in response to a hold request.                                                       |

| 13         | 0           | ROMCS    | ROM CHIP SELECT is an active low chip select output to the BIOS EPROM. It can be also connected to the output enable pin of the EPROM.                                                                   |

| 48, 74, 82 | ı           | A<0:2>   | ADDRESS input lines A<0:2> from the CPU local bus.                                                                                                                                                       |

| 2-8        | ı           | A<3:9>   | ADDRESS input lines A<3:9> from the CPU local bus.                                                                                                                                                       |

| 46         | ı           | A10      | ADDRESS input line A10 from the CPU local bus.                                                                                                                                                           |

| 9-11       | i           | A<11:13> | ADDRESS input lines A<11:13> from the CPU local bus.                                                                                                                                                     |

| 47         | 1           | A14      | ADDRESS input line A14 from the CPU local bus.                                                                                                                                                           |

et4U.com

DataShee

### 82C212 Pin Description (Continued)

| Pin<br>No.    | Pin<br>Type | Symbol   | Description                                                                                                                                                                                                                                                                                                    |

|---------------|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>49-</b> 53 | 1           | A<15:19> | ADDRESS input lines A<15:19> from the CPU local bus.                                                                                                                                                                                                                                                           |

| 55-58         | į.          | A<20:23> | ADDRESS input lines A<20:23> from the CPU local bus.                                                                                                                                                                                                                                                           |

| 34            | I           | BHE      | BYTE HIGH ENABLE is an active low input from the CPU for transfer of data on the upper byte.                                                                                                                                                                                                                   |

| 29            | 1/0         | READY ** | READY is the system ready signal to the CPU. It is an active low output after requested memory or I/O data transfer is completed. It is an input when the current bus cycle is an AT bus cycle and is an output for local memory and I/O cycles.                                                               |

| 59            | 0 -         | AF16     | AF16 is an active low output asserted on local memory (EPROM or DRAM) cycles. It is high for all other cycles. This signal is sampled by the 82C211.                                                                                                                                                           |

| DRAM In       | iterface    |          |                                                                                                                                                                                                                                                                                                                |

| 77-80         | 0           | BAS<3:0> | ROW ADDRESS STROBES 3 to 0 are active low outputs used as RAS signals to the DRAMs for selecting different banks. RAS3 selects the highest bank and RAS0 selects the lowest bank. These signals should be buffered and line terminated with 75Ω resistors to reduce ringing before driving the DRAM RAS lines. |

| 41            | 0           | CAS00    | COLUMN ADDRESS STROBE 00 is an active low output used to select the low byte DRAMs of bank 0. This signal should be line terminated with a $75\Omega$ resistor to reduce ringing before driving the DRAM CAS line.                                                                                             |

| 44            | 0 -         | CAS01    | COLUMN ADDRESS STROBE 01 is an active low output used to select the high byte DRAMs of bank 0. This signal should be line terminated with a $75\Omega$ resistor to reduce ringing before driving the DRAM CAS line.                                                                                            |

| 39            | . 0 .       | CAS10    | COLUMN ADDRESS STROBE 10 is an active low output used to select the low byte DRAMs of bank 1. This signal should be line terminated with a 75Ω resistor to reduce ringing before driving the DRAM CAS line.                                                                                                    |

| 40            | O .         | CAS11    | COLUMN ADDRESS STROBE 11 is an active low output used to select the high byte DRAMs of bank 1. This signal should be line terminated with a $75\Omega$ resistor to reduce ringing before driving the DRAM CAS line.                                                                                            |

| 37            | 0           | CAS20    | COLUMN ADDRESS STROBE 20 is an active low output used to select the low byte DRAMs of bank 2. This signal should be line terminated with a 75Ω resistor to reduce ringing before driving the DRAM CAS line.                                                                                                    |

et4U.com

DataShe

## 82C212 Pin Description (Continued)

| Pin<br>No. | Pin<br>Type | Symbol   | Description                                                                                                                                                                                                                                                                              |

|------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38         | 0           | CAS21    | COLUMN ADDRESS STROBE 21 is an active low output used to select the high byte DRAMs of bank 2. This signal should be line terminated with a $75\Omega$ resistor to reduce ringing before driving the DRAM CAS line.                                                                      |

| 35         | 0           | CAS30    | COLUMN ADDRESS STROBE 30 is an active low output used to select the low byte DRAMs of bank 3. This signal should be line terminated with a 75Ω resistor to reduce ringing before driving the DRAM CAS line.                                                                              |

| 36         | 0           | CAS31    | COLUMN ADDRESS STROBE 31 is an active low output used to select the high byte DRAMs of bank 3. This signal should be line terminated with a 75Ω resistor to reduce ringing before driving the DRAM CAS line.                                                                             |

| 28         | 0           | MWE      | MEMORY WRITE ENABLE is an active low output for DRAM write enable.                                                                                                                                                                                                                       |

| 45         | 0           | DLE .    | DATA LATCH ENABLE is an active high output used to enable the local memory data buffer latch in the 82C215.                                                                                                                                                                              |

| 33         | 0           | DRD      | DATA READ is an active low output used to transfer data from the memory bus to the local CPU bus in the 82C215. If high it sets the data path from the local CPU bus to the memory bus.                                                                                                  |

| 81         | 0           | DLYOUT   | DELAY LINE OUT is an active high output to the defay line for generating the DRAM control signals.                                                                                                                                                                                       |

| 73, 75, 76 | J           | DLY<0:2> | DELAY IN 0, 1, 2 are active high inputs from the first to<br>third taps on the delay line used to generate DRAM contro-<br>signals.                                                                                                                                                      |

| 26         | 0           | XDEN     | X DATA BUFFER ENABLE is an active low output asserted during I/O accesses to locations 22H and 23H. These locations contain the index and data registers for the NEAT CHIPSet. It is used to enable the buffers between the XD and MA buses for accessing the 82C212 internal registers. |

| 27         | 0           | XDIR     | X BUS DIRECTION is used to control the drivers between the X and S buses. The driver should be used such that data flow is from the S to X bus when XDIR is high and in the other direction when XDIR is low.                                                                            |

| 71-72      | 0           | MA<8:9>  | MULTIPLEXED DRAM ADDRESS lines MA8, MA9. These lines should be buffered and line terminated with 750 resistors before driving the DRAM address lines.                                                                                                                                    |

et4U.com

DataShe

## 82C212 Pin Description (Continued)

| Pin<br>No.       | Pin<br>Type | Symbol               | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|-------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66-70<br>60-62   | I/O<br>I/O  | MA<3:7><br>. MA<0:2> | MULTIPLEXED DRAM ADDRESS lines MA0 to MA7. Also used as bi-directional lines to read/write to the internal registers of the 82C212. An external 74ALS245 buffer is required to isolate this path during normal DRAM operation. These lines should be buffered and line terminated with 75Ω resistors before driving the DRAM address lines. |

| Miscellane       | ous         |                      |                                                                                                                                                                                                                                                                                                                                             |

| 31               | 1/0         | GA20                 | ADDRESS line 20 is the gated A20 bit which is controlled by GATEA20.                                                                                                                                                                                                                                                                        |

| 30               | ı           | GATEA20              | GATE ADDRESS 20 is an input used to force A20 low when GATEA20 is low. When high it propagates CPUA20 onto the A20 line. It is used to keep address under 1Mb during DOS operation.                                                                                                                                                         |

| 25               | 0           | LMEGCS               | LOW MEG CHIP SELECT is an unlatched active low output asserted when the low Meg memory address space (0 to 1024 Kbytes) is accessed or during refresh cycles. It is used to disable SMEMR and SMEMW signals on the AT bus if accesses are made beyond the 1Mbyte address space to maintain PC and PC/XT compatibility.                      |

| Power and        | Ground      |                      | DetaCheetalleen                                                                                                                                                                                                                                                                                                                             |

| 32, 42, 84       |             | VDD                  | POWER SUPPLY.                                                                                                                                                                                                                                                                                                                               |

| 1, 22, 43,<br>64 | <b></b>     | VSS                  | GROUND.                                                                                                                                                                                                                                                                                                                                     |

et4U.com

DataShe

## 82C215 Pin Description

| Pin<br>No.                                                            | Pin<br>Type | Symbol              | Description                                                                                                                                                                             |

|-----------------------------------------------------------------------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controls                                                              |             |                     |                                                                                                                                                                                         |

| 14                                                                    | 1           | ACEN                | ACTION CODE ENABLE is an active low input from the 82C211 that validates the action_codes.                                                                                              |

| 12, 13                                                                | l           | AC<1:0>             | ACTION CODES input from the 82C211 are used for bus sizing and byte assembly operations. They are discussed in Section 1.2.4.                                                           |

| 76                                                                    | ı           | DLE                 | DATA LATCH ENABLE is an active high input from the 82C212 used to enable the local memory data buffer latch.                                                                            |

| 74                                                                    | ı           | DRD                 | DATA READ is an active low input from the 82C212 used to transfer data from the M data bus to the CPU data bus. If high, it sets the data path from the CPU data bus to the M data bus. |

| 53                                                                    | ı           | HLDA1               | HOLD ACKNOWLEDGE 1 is an active high input from the 82C211 used for address and data direction control during DMA cycles.                                                               |

| 15                                                                    | 1           | IALE                | ADDRESS LATCH ENABLE (INTERNAL) is an active high input from the 82C211 used to latch the CPU address lines on to the X address lines.                                                  |

| 11                                                                    | ı           | BHE                 | BYTE HIGH ENABLE is an active low input from the CPU. It is used to enable the high byte parity checking.                                                                               |

| 10                                                                    | ı           | AO                  | ADDRESS line A0 is input from the CPU. It is used to enable the low byte parity checking.                                                                                               |

| Address                                                               |             | -                   |                                                                                                                                                                                         |

| 25-31<br>33-41                                                        | 1/0         | A<1:7><br>A<8:16>   | ADDRESS lines A1-A16 from the CPU. They are input during CPU and refresh cycles and output during DMA/ Master cycles.                                                                   |

| 44-52<br>54-60                                                        | I/O<br>I/O  | XA<16:8><br>XA<7:1> | X ADDRESS lines XA16-XA1 (latched) are connected to the peripheral bus in the IBM™ PC/AT architecture.                                                                                  |

| Data                                                                  |             |                     |                                                                                                                                                                                         |

| 2, 4, 6,<br>8, 16, 18,<br>20, 23, 3,<br>5, 7, 9,<br>17, 19,<br>21, 24 | 1/0         | D<15:0>             | DATA lines D15-D0 from the CPU.                                                                                                                                                         |

et4U.com

DataShee

# CHIP'5

### 82C215 Pin Description (Continued)

| Pin<br>No.                                          | Pin<br>Type | Symbol   | Description                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------------------------------------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 82, 80,<br>73, 71, 69,                              | 1/0         | MD<15:0> | MEMORY DATA lines MD15-MD0 from the memory bus.                                                                                                                                                                                                      |  |  |  |  |  |

| 67, 65, 62,<br>81, 79, 72,<br>70, 68, 66,<br>63, 61 | <br>-       |          |                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Parity                                              |             |          |                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 78, 77                                              | 1/0         | MP1, MP0 | MEMORY PARITY bits MP1, MP0 are the parity bits for the high and low order bytes of the system DRAMs. These lines are input during memory operations for parity error detection and are output during memory write operations for parity generation. |  |  |  |  |  |

| 83                                                  | 0           | PARERR   | PARITY ERROR is an active low output to the 82C211 which goes active upon detecting a parity error during a system memory read operation. It is used to generate a non-maskable interrupt to the CPU.                                                |  |  |  |  |  |

| Power and                                           | Ground      |          | · ·                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 32, 42, 84                                          | . —         | VDD      | POWER                                                                                                                                                                                                                                                |  |  |  |  |  |

| 1, 22, 43                                           |             | VSS      | GROUND                                                                                                                                                                                                                                               |  |  |  |  |  |

et4U.com

DataShee

17

DataSheet4U.com www.DataSheet4U.com

#### 1. 82C211 BUS CONTROLLER

#### 1.1 Features

- Clock generation with software speed selection.

- Optional independent AT bus clock.

- CPU interface and bus control.

- Programmable command delays and wait state generation.

- Port B register.

#### 1.2 Functional Description

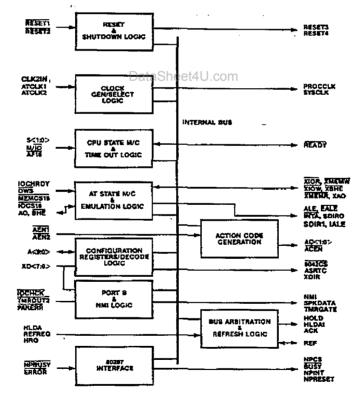

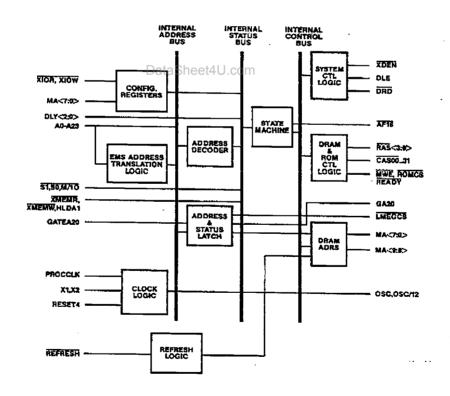

The 82C211 Bus Controller consists of the following functional sub-modules as illustrated in figure 1.1:

- Reset and Shut down logic

- Clock generation and selection logic

- CPU state machine, AT bus state machine and bus arbitration logic

- Action Codes generation logic

- Port B register and NMI logic

- DMA and Refresh logic

- Numeric Coprocessor interface logic

- Configuration registers

#### 1.2.1 Reset and Shut Down Logic

Two reset inputs RESET1 and RESET2 are provided on the 82C211 bus controller. RESET1 is the Power Good signal from the power supply. When RESET1 is active, the 82C211 asserts RESET3 and RESET4 for a system reset. RESET2 is generated from the 8042 (or 8742) keyboard controller when a "warm reset" is required. The warm reset activates RESET3 to reset the 80286 CPU.

Figure 1.1 82C211 Block Diagram

DataShe

RESET3 is also activated by the 82C211 when a shut down condition is detected in the CPU. Additionally, a low to high transition in REG60<5> causes RESET3 to be active after the current I/O command goes inactive. RESET3 is asserted for at least 16 PROCCLK cycles and then deasserted. RESET4 is used to reset the AT bus, 82C206 IPC, 8042 keyboard controller and the 82C212 memory controller. It is synchronized with respect to PROCCLK and is asserted as long as the Power Good signal is held low.

After a shut down condition is detected. RESET3 is asserted and held high for at least 16 PROCCLK cycles and then deasserted. RESET3 resulting from a shut down condition is synchronous with PROCCLK, ensuring proper CPU operation. Both RESET3 and RESET4 meet the setup and hold timing requirements of the 80286 CPU.

#### 1.2.2 Clock Generation and Selection Logic

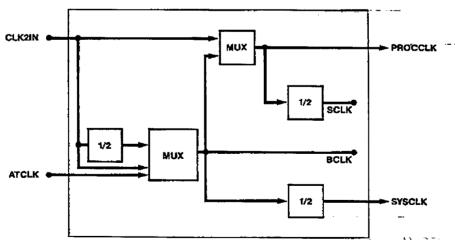

The 82C211 provides a flexible clock selection scheme as shown in Figure 1.2. It has two input clocks; CLK2IN and ATCLK. CLK2IN is driven from a TTL crystal oscillator, running at a maximum of twice the processor clock neet4U.coBCLK = CLK2IN/2 (PROCCLK) frequency. ATCLK is derived from a crystal. Typically, it should be of a lower frequency than CLK2IN. ATCLK and CLK2IN can be selected under program controi.

The 82C211 generates processor clock, PROCCLK, for driving the CPU state machine and Interface, SCLK (internal) is PROCCLK/2 and is in phase with the Internal states of the 80286. BCLK (internal) is the AT bus state machine clock and is used for the AT bus interface, SYSCLK is the AT bus system clock and is always BCLK/2.

PROCCLK can be derived from CLK2IN or from ATCLK. In the synchronous mode, both PROCCLK and BCLK are derived from CLK2IN, so that the processor state machine and the AT bus state machine run synchronous. In the asynchronous mode, BCLK is generated from the ATCLK and PROCCLK is generated from CLK2IN or the ATCLK. In this case, the processor and AT bus state machines run asynchronous to each other. The following clock selections are possible:

#### Synchronous mode

- 1. PROCCLK = BCLK = CLK2IN SYSCLK = BCLK/2 = CLK2IN/2

- 2. PROCCLK = CLK2IN SYSCLK = BCLK/2 = CLK2IN/4

- 3. PROCCLK = BCLK = CLK2IN/2 . SYSCLK = BCLK/2 = CLK2IN/4 - : .--- -.. **-**.. **-**.. - :: :...

Figure 1.2 Clock Selection Block Diagram

DataShe

#### Asynchronous mode

- 1. PROCCLK = CLK2IN BCLK = ATCLK SYSCLK = BCLK/2 = ATCLK/2

- 2. PROCCLK = ATCLK

BCLK = ATCLK

SYSCLK = BCLK/2 = ATCLK/2.

Under normal operation, CLK2IN should be selected as the processor clock (PROCCLK) to allow the processor to run at full speed. BCLK can either be a sub-division of CLK2IN or the ATCLK. ATCLK may be selected to generate PROCCLK only when it is desired to slow down the processor for timing dependent code execution. Once the options for clock switching are set, the switching occurs with clean transition in the asynchronous or synchronous mode. During clock switching, no phases of PROCCLK are less

than the minimum value or greater than the maximum value specified for the 80286 CPU. The clock source selection is made by writing to REG62H<0:1> first and then to REG60H<4>, which default to: PROCCLK = CLK2IN, SYSCLK = CLK2IN/4.

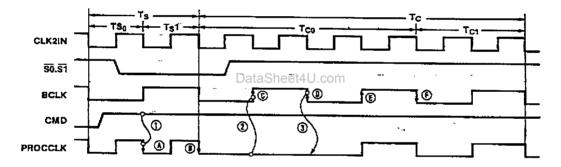

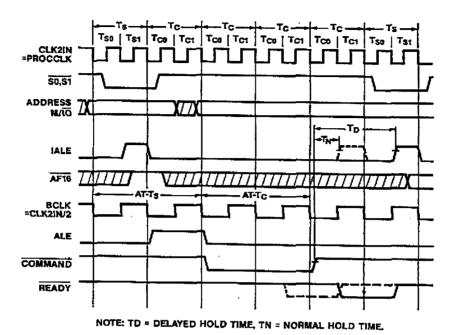

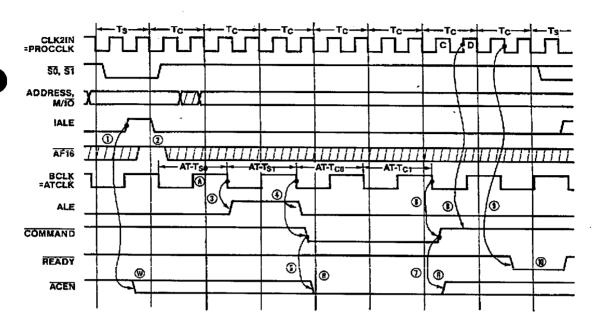

Figures 1.3 and 1.4 illustrate the sequence of events that switch PROCCLK from high to low speed and from low to high speed, upon receiving a request from the configuration register. In Figure 1.3, the falling edge (A) of PROCCLK is used to latch the command inactive condition (1). On the falling edge (B), CLK2IN is disabled on the PROCCLK line. This ensures that clock switching will occur when PROCCLK is low. Once CLK2IN has been disabled, the first rising edge (C) of BCLK latches this condition as denoted by sequence (2). BCLK then enables Itself on the PROCCLK line on the falling edge (D) as

Figure 1.3 Sequence Diagram for High to Low Frequency Transition

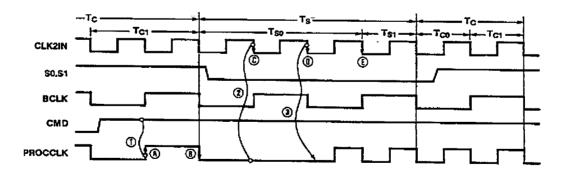

Figure 1.4 Sequence Diagram for Low to High Frequency Transition

et4U.com

DataShe

## Chir's

denoted by sequence (3). This ensures a glitch free transition between the two clocks. It also does not violate the min and max 80286 CPU clock specifications. If BCLK is asynchronous with respect to CLK2IN, it is possible that sequence (2) could violate setup time requirements with respect to edge (C). In this case, edge (D) will register the state of PROCCLK as still being high in sequence (3). Hence, edge (E) samples PROCCLK to be low and edge (F) enables BCLK on the PROCCLK line. This case does not violate the min and max 80286 CPU clock specifications.

In Figure 1.4, the rising edge (A) of PROCCLK latches command inactive as denoted by sequence (1). Edge (B) disables BCLK on the PROCCLK line. In sequence (2), edge (C) of CLK2IN latches PROCCLK low. Edge (D) then enables CLK2IN on the PROCCLK line as denoted by sequence (3). If sequence (2) does not meet setup time requirements of edge (C), then the state of PROCCLK is sampled as being high in sequence (2). In this case, edge (D) samples PROCCLK low and edge (E) enables CLK2IN on the PROCCLK line. In this case also, PROCCLKheet4L does not violate the min and max 80286 CPU clock specifications.

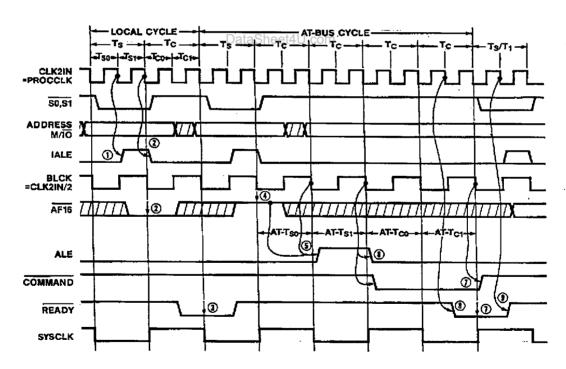

# 1.2.3 CPU State Machine, Bus State Machine and Bus Arbitration

In order to extract maximum performance out of the 80286 on the system board, it is desirable to run the system board at the rated maximum CPU frequency. This frequency may be too fast for the slow AT bus. In order to overcome this problem, the 82C211 has two state machines: the CPU state machine which typically runs off CLK2IN, and the AT bus state machine which runs off BCLK. The two state machines maintain an asynchronous protocol under external mode operation.

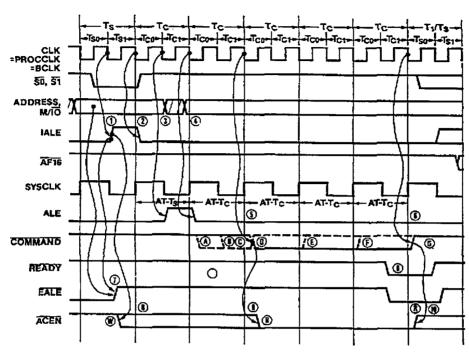

#### **CPU State Machine**

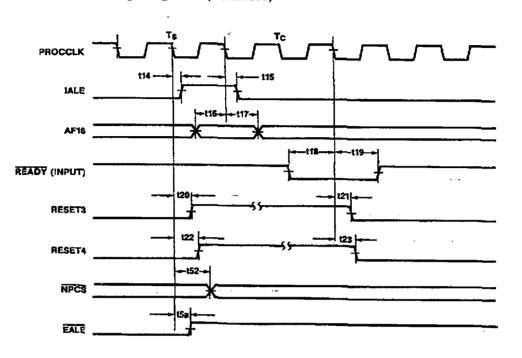

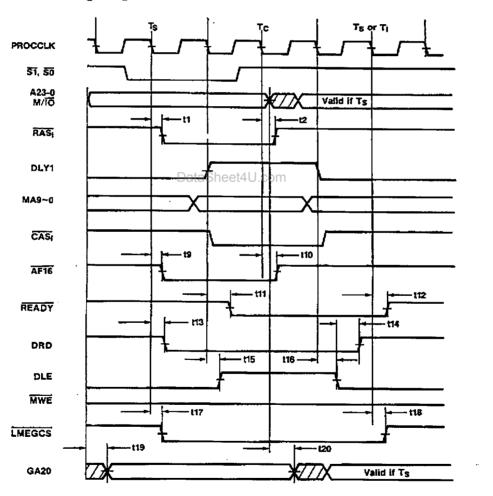

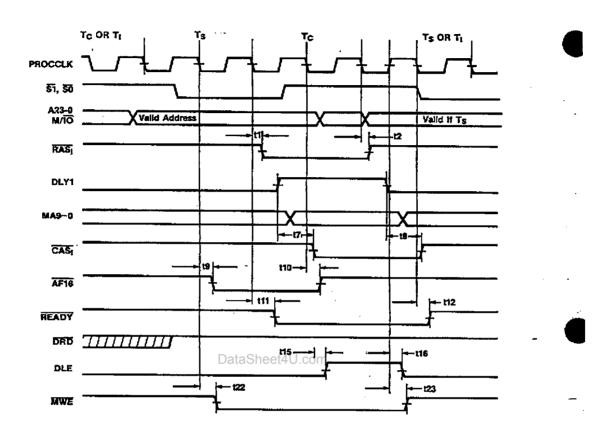

Interface to the 80286 requires interpretation of the status lines S0, S1, M/IO during TS0 and the synchronization and generation of READY to the CPU upon completion of the requested operation. IALE is issued in res-

ponse to the beginning of a new cycle in TS1 by the 82C211. If AF16 is detected as being inactive at the end of the processor TS state, control is handed over to the AT bus state machine. The CPU state machine then waits for READY to be active to terminate the current cycle. All local memory cycles are 16 bit cycles. If AF16 is asserted in response to a new CPU cycle and READY is not returned to the 82C211 within 128 clocks, and REG60H<2> is enabled, then an NMI is generated to signal bus time-out, if NMI has been enabled.

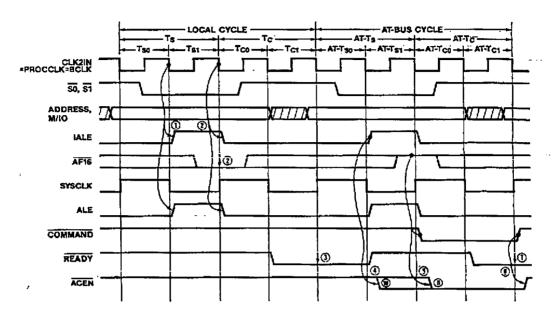

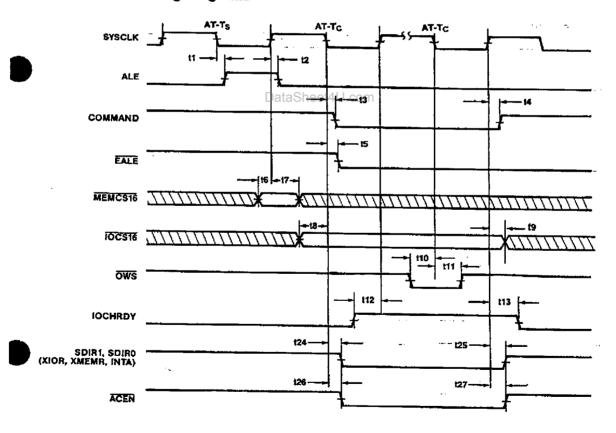

#### AT Bus State Machine

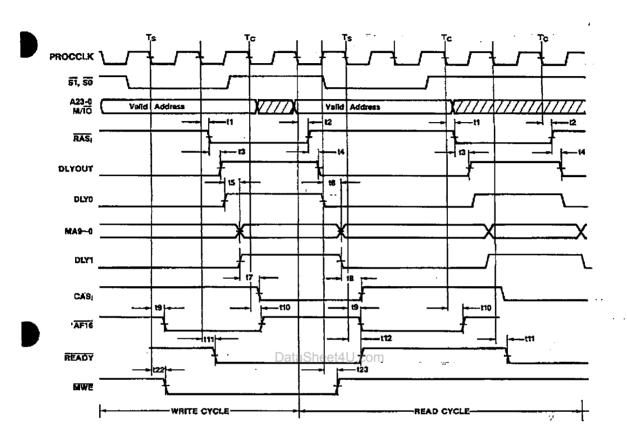

The AT bus state machine gains control when AF16 is detected inactive by the CPU state machine. It uses BCLK which is twice the frequency of AT system clock SYSCLK. When ATCLK is selected as the source for BCLK, it also performs the necessary synchronization of control and status signals between the AT bus and the processor. The 82C211 supports 8 and 16 bit transfers between the processor and 8 or 16 bit memory or I/O devices located on the AT bus. The action codes AC0, AC1 qualified by ACEN are used for bus sizing and 8, 16 bit bus conversions by the 82C215. They are discussed in section 1.2.4.

The AT bus cycle is initiated by asserting ALE in AT-TS1. On the falling edge of ALE, MEMCS16 is sampled for a memory cycle to determine the bus size. It then enters the command cycle AT-TC and provides the sequencing and timing signals for the AT bus cycle. For an I/O cycle, IOCS16 is sampled in the middle of the processor TC state. These control signals emulate the lower speed AT bus signals. The command cycle is terminated when IOCHRDY is active on the AT bus and all programmed wait states have been executed.

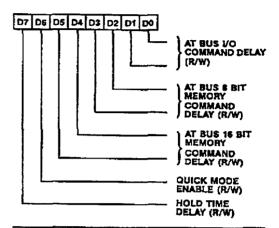

It is possible to provide software selectable wait states and command delays to the AT state machine. Providing command delays causes the commands (XMEMR XMEMW XIOR or XIOW) to be delayed from going active in BCLK steps. Providing wait states causes READY to be delayed to the CPU in steps of the AT command cycles (AT-TC). The defaults and settings are discussed in section 1.4.

DataShe

21

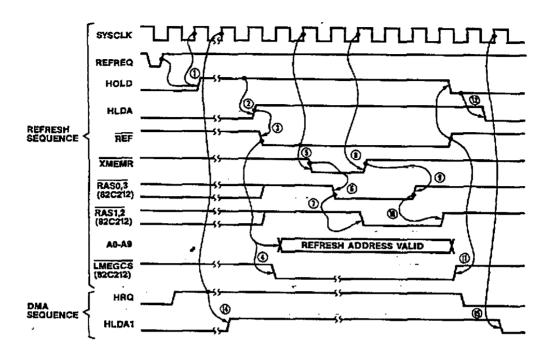

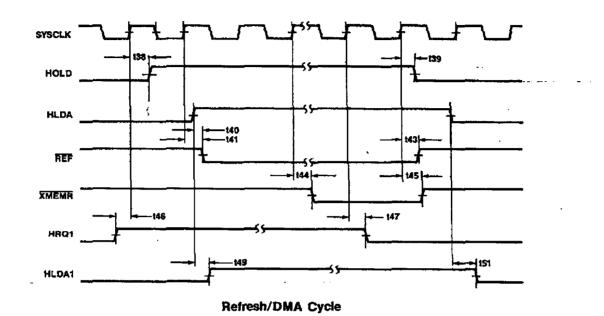

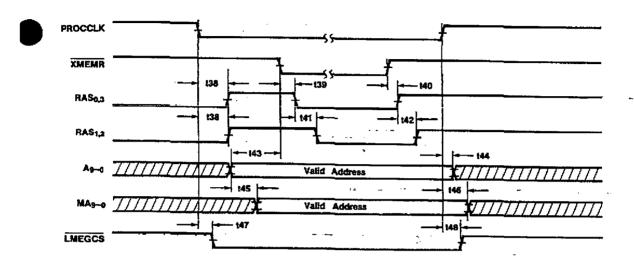

Figure 1.5 Refresh/DMA Sequence

#### **Bus Arbitration**

The 82C211 controls all bus activity and provides arbitration between the CPU, DMA/ Master devices, and DRAM refresh logic. It handles HRQ and REFREQ by generating HOLD request to the CPU and arbitrating among these requests in a non-preemptive manner. The CPU relinquishes the bus by issuing HLDA. The 82C211 responds by issuing REF or HLDA1 depending on the requesting device. During a refresh cycle, the refresh logic has control of the bus until REF goes inactive. XMEMR is asserted low during a refresh cycle and the refresh address is provided on the A0-A9 address lines by the 82C211 to be used by the 82C212 memory controller. During a DMA cycle, the DMA controller has control of the bus until HRQ goes inactive. The 82C211 puts out the action codes for bus sizing. ALE, EALE and ACEN are active during DMA cycle.

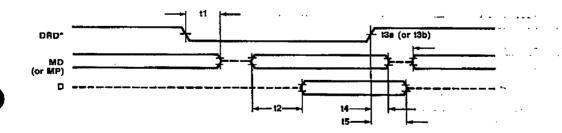

Figure 1.5 is a sequence diagram for Refresh/ DMA cycles. Upon receiving a refresh request

DataSheet (BEFREQ) it is internally latched by the 82C211. On the first rising edge of SYSCLK, HOLD is output to the processor in sequence 1. Depending on the current activity of the processor, a hold acknowledge (HLDA) is issued by the processor in sequence 2, after a DMA latency time. The 82C211 responds with REF active in sequence 3. LMEGCS from the 82C212 goes active in sequence 4. XMEMR is asserted low on the second rising edge of SYSCLK after REF is low in sequence 5. The 82C212 pulls all its RAS lines (RAS0-RAS3) high when REF goes low. The RAS lines go active in sequences 6 and 7 when the refresh address is active on the AO-A9 lines of the 82C211. The 82C212 uses the A0-A9 lines to generate the refresh address on the MA0-MA9 address lines. XMEMR goes inactive in sequence 8 followed by the RAS lines going inactive in sequences 9, 10. REF, LMEGCS and HOLD go inactive in sequence 11. Control is transferred to the CPU after HLDA goes inactive in sequence 12.

If a DMA device requests control of the bus.

DataShe

22

the 82C211 receives HRQ active. After a DMA latency time, the CPU relinquishes the bus to the requesting device by Issuing HLDA1 in sequence 14. HLDA1 is active as long as HRQ is active. Once the DMA device deasserts HRQ, HLDA1 is deasserted by the 82C211 in sequence 15, to return control to the processor.

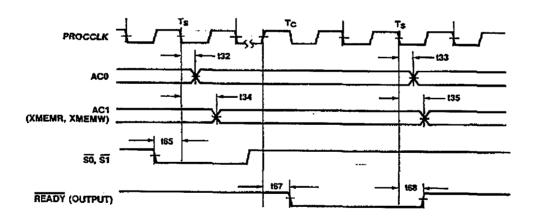

#### 1.2.4 Action Codes Generation Logic

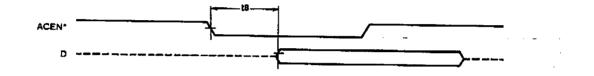

The AT state machine performs data conversion for CPU accesses to devices not on the CPU or Memory Bus. The AT bus conversions are performed for 16 to 8 bit read or write operations. Sixteen bit transfers to/from the CPU are broken into smaller 8 bit AT bus or peripheral bus reads or writes. The action codes are generated as shown in Table 1.1 to control the buffers in the 82C215. The action codes are in response to signals MEMCS16, IOCS16.

Table 1.1

Action Codes Enable (ACEN) Generation

| Operation    | ACEN                                                                         |

|--------------|------------------------------------------------------------------------------|

| DMA/MASTER   | 0                                                                            |

| CPU (local)  | 1                                                                            |

| CPU (AT bus) | 0 for write 0 qualified by command for read and interrupt acknowledge cycles |

| REFRESH      | 1 qualified by REF                                                           |

#### AT-Bus CPU Cycles HLDA1 = 0

| •  |                                         |

|----|-----------------------------------------|

| AC | Operation                               |

| 00 | 16 bit write and 8 bit write (low byte) |

| 01 | 16 bit read and 8 bit read (low byte)   |

| 10 | 8 bit write (high byte)                 |

| 11 | 8 bit read (high byte)                  |

I White

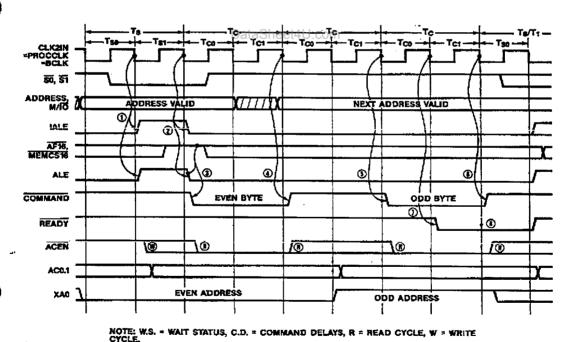

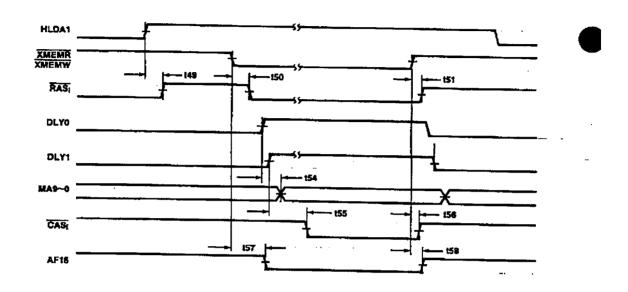

Figure 1.6 Quick Mode Bus Conversion Cycle (0WS, 0CD)

et4U.com

DataShe

23

www.DataSheet4U.com

#### DMA/MASTER Cycles, HLDA1 = 1

| AC | Operation                                                                           |

|----|-------------------------------------------------------------------------------------|

| 00 | MD bus tri-stated from the 82C215 for 16 bit and 8 (low byte) read/write operations |

| 01 | Reserved                                                                            |

| 10 | High memory write MD0-7 to MD8-15                                                   |

| 11 | High memory read MD8-15 to MD0-7                                                    |

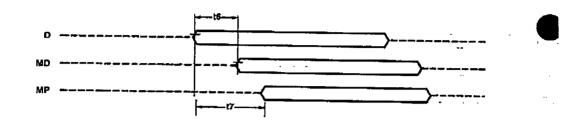

Figure 1.6 shows a sequence diagram for a data conversion cycle in Quick mode with zero walt states (0 W.S.) and zero command delays (0 C.D.). Quick mode is discussed in section 1.3.2. In Quick mode ALE is issued on the AT bus as shown in sequences 1 and 2. MEMCS16 from an external device is sampled high by the 82C211 in sequence 3, initiating a bus conversion cycle. The first command also goes active in sequence 3 for the first byte operation and is terminated in sequence 4. In order to provide sufficient back to back time between the two 8 bit cycles, the second byte command is issued ated in sequence 6. No second ALE is issued for the second byte operation since only address line XA0 changes from zero to one. READY is asserted low in sequence 7 and is sampled low by the processor in sequence 8, to terminate the current cycle. ACEN and ACO, AC1 are issued by the 82C211 for bus conversion as shown.

#### 1.2.5 Port B and NMI generation logic

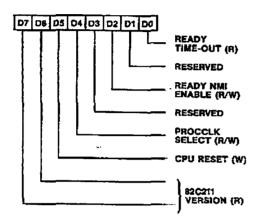

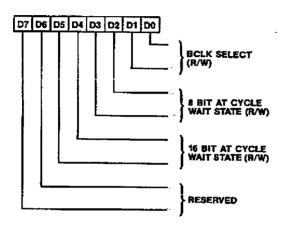

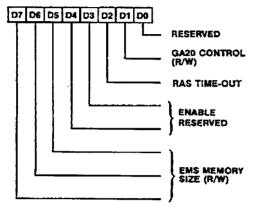

The 82C211 provides access to Port B defined for the PC/AT as shown in Figure 1.7.

| IO ADDR | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|------|---|

| 61H     | PCK | CHK | 720 | ŖFD | EIC | EPR | SPK | T2G | PORT | Ŗ |

Figure 1.7 Port B

| Bits | Read/<br>Write | Function                                 |  |  |  |  |

|------|----------------|------------------------------------------|--|--|--|--|

| 7    | R              | PCK-System memory parity check           |  |  |  |  |

| 6    | R              | CHK-I/O channel check                    |  |  |  |  |

| 5    | R              | T20-Timer 2 Out                          |  |  |  |  |

| 4    | R              | RFD-Refresh Detect                       |  |  |  |  |

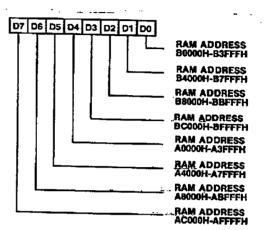

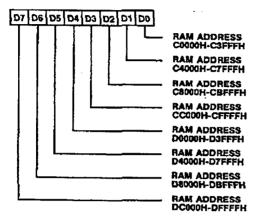

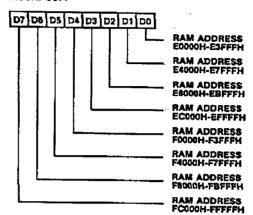

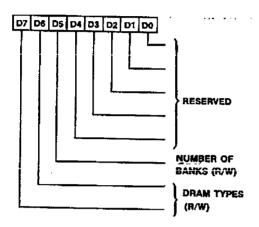

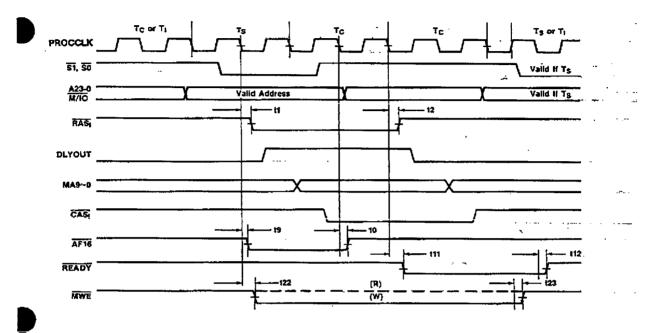

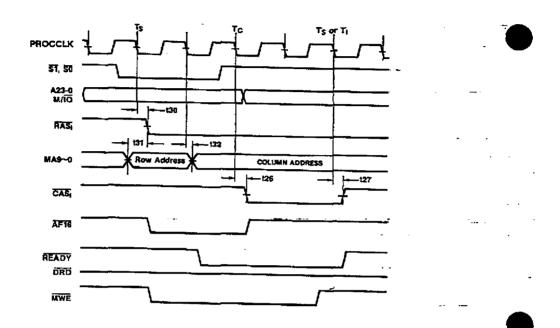

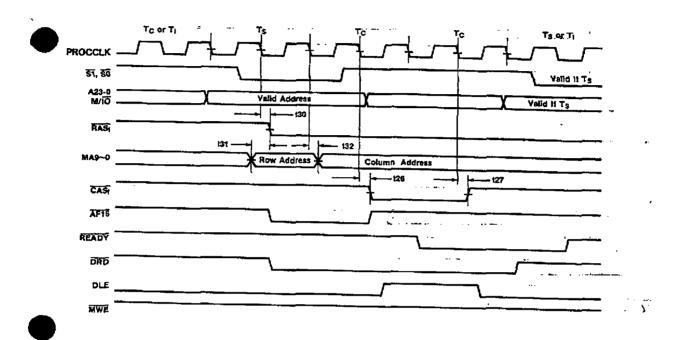

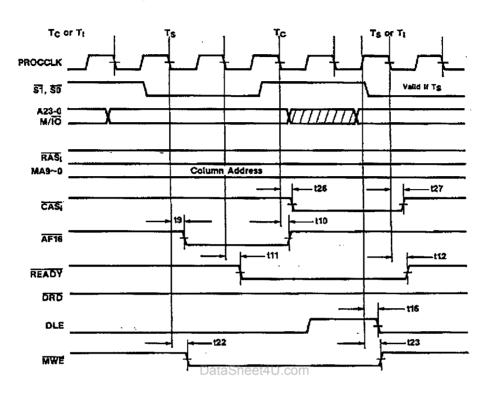

| 3    | R/W            | EIC-Enable I/O channel check             |  |  |  |  |